# An Investigation into the Realities of a Quantum Datapath

Nemanja Isailovic

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-60 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-60.html

May 11, 2010

Copyright © 2010, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### An Investigation into the Realities of a Quantum Datapath

by

Nemanja Isailovic

B.S. (University of California, Berkeley) 1999M.S. (University of California, Berkeley) 2002

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

Graduate Division of the University of California, Berkeley

Committee in charge:

Professor John David Kubiatowicz, Chair Professor Kurt Keutzer Professor Dorit Hochbaum

Spring Semester 2010

The dissertation of Nemanja Isailovic, titled An Investigation into the Realities of a Quantum Datapath, is approved:

| Chair | <br>Date |  |

|-------|----------|--|

|       | <br>Date |  |

|       | <br>Date |  |

University of California, Berkeley

Spring Semester 2010

#### An Investigation into the Realities of a Quantum Datapath

Copyright 2010 by Nemanja Isailovic

#### Abstract

An Investigation into the Realities of a Quantum Datapath

by

Nemanja Isailovic Doctor of Philosophy in Computer Science

University of California, Berkeley Professor John David Kubiatowicz, Chair

Quantum computing has shown great potential for being able to solve certain problems which are intractable on classical machines. Peter Shor devised a means to factor large number in polynomial time on a quantum machine, a feat which would compromise modern public key cryptosystems. Further, simulation of quantum mechanical systems, which is exponential in both space and time on a classical machine, is expected to be far faster on a quantum machine. In this work, we present mechanisms for producing a laid out and scheduled quantum datapath tailored to a particular target circuit.

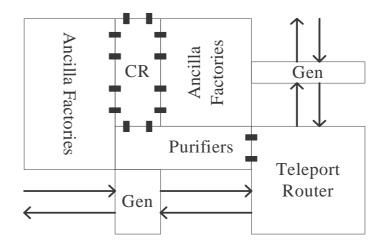

We identify two key pieces of support infrastructure in a quantum datapath. First, some quantum operations require the use of helper qubits known as ancilla qubits which are not part of the target circuit specification. We introduce and design efficient ancilla factories to use as basic functional units in our datapath layouts. Second, we provide designs for the basic components that allow the construction of a teleportation network, which is necessary for long distance communication on a quantum datapath.

We utilize our basic component designs in proposing a malleable architectural specification which we call Qalypso. The benefit of the flexibility of Qalypso lies in the ability to fine tune the various components of the datapath to suit the needs of a given quantum circuit. Ancilla bandwidth, network resources and interfacing of support infrastructure to data may all be tailored to fit circuit characteristics.

To complete the process of laying out and scheduling a quantum circuit, we device heuristics for mapping the circuit onto Qalypso while simultaneously finalizing the datapath characteristics as appropriate for the circuit. Our methods produce a final realizable datapath layout and associated scheduling, both optimized for the circuit in question.

We have implemented these heuristics in a quantum CAD flow toolset currently tailored to designing architectures in ion trap technology. We conclude this thesis by demonstrating the application of these heuristics through the automated toolset to construct a datapath and schedule optimized for Shor's factorization algorithm.

Professor John David Kubiatowicz Dissertation Committee Chair I dedicate this body of work to my wife, Lisa, for her infinite patience and compassion, to my mother, father and sister for their support and encouragement and to my newborn angel Evelyn for the motivation to finish.

### Contents

| Li       | st of | Figures                                                                                                 | $\mathbf{v}$ |

|----------|-------|---------------------------------------------------------------------------------------------------------|--------------|

| Lis      | st of | Tables                                                                                                  | xiii         |

| 1        | Intr  | oduction                                                                                                | 1            |

|          | 1.1   | Quantum Circuits                                                                                        | 2            |

|          |       | 1.1.1 Qubits, Superposition and Measurement                                                             | 2            |

|          |       | 1.1.2 Quantum Circuit Model                                                                             | 3            |

|          |       | 1.1.3 Universal Gates                                                                                   | 4            |

|          |       | 1.1.4 Encoded Qubits                                                                                    | 5            |

|          |       | 1.1.5 Performing Quantum Error Correction                                                               | 8            |

|          |       | 1.1.6 Teleportation $\ldots$                                                                            | 9            |

|          | 1.2   | Quantum Computing Technologies                                                                          | 10           |

|          |       | 1.2.1 Ion Traps at a Glance                                                                             | 11           |

|          |       | 1.2.2 Trap Electrodes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$           | 11           |

|          |       | 1.2.3 Gate Lasers                                                                                       | 12           |

|          |       | 1.2.4 Measurement $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               | 13           |

|          | 1.3   | Quantum Computer Architecture                                                                           | 14           |

|          |       | 1.3.1 Hardware Components                                                                               | 15           |

|          |       | 1.3.2 The Mapping Problem                                                                               | 16           |

|          |       | 1.3.3 Metrics $\ldots$ | 17           |

|          | 1.4   | Thesis Roadmap                                                                                          | 18           |

| <b>2</b> | Ove   | erview of Computer Aided Design for Quantum Circuits                                                    | 19           |

|          | 2.1   | Classical Computer Aided Design Flows                                                                   | 19           |

|          |       | 2.1.1 Logic Synthesis and Optimization                                                                  | 19           |

|          |       | 2.1.2 Functional Verification                                                                           | 20           |

|          |       | 2.1.3 Placement and Routing                                                                             | 20           |

|          |       | 2.1.4 Physical Verification                                                                             | 21           |

|          | 2.2   | Differences Between Classical and Quantum CAD Flows                                                     | 21           |

|          | 2.3   | Application Circuit Specification                                                                       | 23           |

|          | 2.4   | Quantum Logic Synthesis                                                                                 | 29           |

|          |       |                                                                                                         |              |

| 3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded $\pi/8$ Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla Factories       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | 2.4.1    | Technology Dependent Gates                                    | 29 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------|---------------------------------------------------------------|----|

| 2.5       Ion Trap Layout       31         2.5.1       Data Qubit Area       32         2.5.2       Layout Graph Representation       33         2.6       Custom Modules       34         2.7       Fault Tolerance Verification       34         2.7.1       Determining Failure Probability       36         2.7.2       Fault Tolerance Metrics       36         2.8.3       Benchmarks for Evaluating Quantum CAD       36         2.8.4       Ractorization and Its Subcircuits       37         2.9       ADCR-Optimal       37         2.9       ADCR-Optimal       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmarks       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmarks       45         3.2.2       QEC Circuit Characteristics       43         3.2       Benchmarks       45         3.2.1       Benchmarks       47         3.3                                                                     |   |     | 2.4.2    | Fault Tolerant Gate Constructions                             | 29 |

| 2.5.1Data Qubit Area322.5.2Layout Graph Representation332.6Custom Modules342.7Fault Tolerance Verification342.7.1Determining Failure Probability362.7.2Fault Tolerance Metrics362.8Benchmarks for Evaluating Quantum CAD362.8.1Factorization and Its Subcircuits372.8.2Random Circuit Generation372.9ADCR-Optimal373Ancilla Factories393.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factory493.3.2Encoded $\pi/8$ Ancilla Factory493.3.3Encoded $\pi/8$ Ancilla Factory493.3.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla Factories59                                                                                                                                                                                                                    |   |     | 2.4.3    | Error Correction Circuit Optimization                         | 29 |

| 2.5.2Layout Graph Representation332.6Custom Modules342.7Fault Tolerance Verification342.7.1Determining Failure Probability362.7.2Fault Tolerance Metrics362.8Benchmarks for Evaluating Quantum CAD362.8.1Factorization and Its Subcircuits372.8Random Circuit Generation372.9ADCR-Optimal373Ancilla Factories393.1Ancilla Preparation Circuits393.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmark Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3Simple Ancilla Factory533.3.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla Factories594Datapath Variations614.1.1Network Model614.1.1Network Components614.1.2Purification63                                                                                                                                                                                                                      |   | 2.5 | Ion Tr   | ap Layout                                                     | 31 |

| 2.6Custom Modules342.7Fault Tolerance Verification342.7.1Determining Failure Probability362.7.2Fault Tolerance Metrics362.8Benchmarks for Evaluating Quantum CAD362.8.1Factorization and Its Subcircuits372.8.2Random Circuit Generation372.9ADCR-Optimal373Ancilla Factories393.1Ancilla Preparation Circuits393.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmark Characteristics: Ancilla Need443.2.1Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factories483.3.2Encoded Zero Ancilla Factory493.3.3Loubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined AncillaFactories594Datapath Variations614.1.1Network Model614.1.2                                                                                                                                                                                     |   |     | 2.5.1    | Data Qubit Area                                               | 32 |

| 2.7       Fault Tolerance Verification       34         2.7.1       Determining Failure Probability       36         2.7.2       Fault Tolerance Metrics       36         2.7.2       Fault Tolerance Metrics       36         2.8.1       Factorization and Its Subcircuits       37         2.8.1       Factorization and Its Subcircuits       37         2.8.2       Random Circuit Generation       37         2.9       ADCR-Optimal       37         3       Ancilla Factories       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/2^k$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Simple Ancilla Factory       49         3.3.1       Si                  |   |     | 2.5.2    | Layout Graph Representation                                   | 33 |

| 2.7.1       Determining Failure Probability       36         2.7.2       Fault Tolerance Metrics       36         2.8       Benchmarks for Evaluating Quantum CAD       36         2.8.1       Factorization and Its Subcircuits       37         2.8.2       Random Circuit Generation       37         2.9       ADCR-Optimal       37         3       Ancilla Factories       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3.1       Simple Ancilla Factory       49         3.3.2       Encoded Zro Ancilla Factory       49         3.3.3       Sinceded $\pi/8$ Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4              |   | 2.6 | Custo    | m Modules                                                     | 34 |

| 2.7.2Fault Tolerance Metrics362.8Benchmarks for Evaluating Quantum CAD362.8.1Factorization and Its Subcircuits372.8.2Random Circuit Generation372.9ADCR-Optimal373Ancilla Factories393.1Ancilla Preparation Circuits393.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3.1Simple Ancilla Factory493.3.3Encoded Zero Ancilla Factory493.3.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories594Datapath Variations614.1.1Network Model614.1.2Purification63                                                                                                                                                                                                                                                                                                                                         |   | 2.7 | Fault    | Tolerance Verification                                        | 34 |

| 2.8       Benchmarks for Evaluating Quantum CAD       36         2.8.1       Factorization and Its Subcircuits       37         2.8.2       Random Circuit Generation       37         2.9       ADCR-Optimal       37         37       Ancilla Factories       39         3.1       Ancilla Preparation Circuits       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmarks       45         3.2.2       QEC Circuit Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factory       49         3.3.2       Encoded Zero Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural T                  |   |     | 2.7.1    |                                                               | 36 |

| 2.8.1Factorization and Its Subcircuits372.8.2Random Circuit Generation372.9ADCR-Optimal373Ancilla Factories393.1Ancilla Preparation Circuits393.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmark Characteristics: Ancilla Need443.2.1Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factories483.3.2Encoded Zero Ancilla Factory493.3.3Encoded $\pi/8$ Ancilla Factory533.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories594Datapath Variations614.1Network Components614.1.2Purification63                                                                                                                                                                                                                                                                                               |   |     | 2.7.2    | Fault Tolerance Metrics                                       | 36 |

| 2.8.2Random Circuit Generation372.9ADCR-Optimal373Ancilla Factories393.1Ancilla Preparation Circuits393.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmark Characteristics: Ancilla Need443.2.1Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factories483.3.2Encoded Zero Ancilla Factory493.3.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories594Datapath Variations614.1Network Model614.1.2Purification63                                                                                                                                                                                                                                                                                                                                                                                |   | 2.8 | Bench    |                                                               | 36 |

| 2.9       ADCR-Optimal       37         3       Ancilla Factories       39         3.1       Ancilla Preparation Circuits       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factory       49         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded A/8 Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need                        |   |     | 2.8.1    |                                                               | 37 |

| 3 Ancilla Factories       39         3.1 Ancilla Preparation Circuits       39         3.1.1 Computing on Encoded Data Bits       39         3.1.2 Circuit Evaluation Methodology       41         3.1.3 Encoded Ancilla Preparation       41         3.1.4 Fault Tolerant $\pi/8$ Gate       42         3.1.5 Fault Tolerant $\pi/2^k$ Gates       43         3.2 Benchmark Characteristics: Ancilla Need       44         3.2.1 Benchmarks       45         3.2.2 QEC Circuit Characteristics       45         3.2.3 Non-Transversal One-Qubit Gates       47         3.3 Ancilla Factory Layout       47         3.3.1 Simple Ancilla Factories       48         3.3.2 Encoded Zero Ancilla Factory       49         3.3.3 Encoded $\pi/8$ Ancilla Factory       53         3.4 Qubit Fidelity When Multiplexing       55         3.4 Architectural Trade-offs       56         3.4.1 Matching Production to Need       56         3.4.2 Latency/Area Evaluation       57         3.4.3 Qalypso: Microarchitectural Implications of Pipelined Ancilla Factories       59         4 Datapath Variations       61         4.1 Network Model       61         4.1.2 Purification       63  |   |     | 2.8.2    |                                                               |    |

| 3.1       Ancilla Preparation Circuits       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Simple Ancilla Factories       48         3.3.1       Simple Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61       61         4.1       Network Model       61       6 |   | 2.9 | ADCF     | R-Optimal                                                     | 37 |

| 3.1       Ancilla Preparation Circuits       39         3.1.1       Computing on Encoded Data Bits       39         3.1.2       Circuit Evaluation Methodology       41         3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Simple Ancilla Factories       48         3.3.1       Simple Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61       61         4.1       Network Model       61       6 | 2 | And | silla Fa | atorios                                                       | 20 |

| 3.1.1Computing on Encoded Data Bits393.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmark Characteristics: Ancilla Need443.2.1Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factories483.3.2Encoded Zero Ancilla Factory493.3.3Encoded $\pi/8$ Ancilla Factory533.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories594Datapath Variations614.1.1Network Model614.1.2Purification63                                                                                                                                                                                                                                                                                                                                                                                                                                                | J |     |          |                                                               |    |

| 3.1.2Circuit Evaluation Methodology413.1.3Encoded Ancilla Preparation413.1.4Fault Tolerant $\pi/8$ Gate423.1.5Fault Tolerant $\pi/2^k$ Gates433.2Benchmark Characteristics: Ancilla Need443.2.1Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factories483.3.2Encoded Zero Ancilla Factory493.3.3Encoded $\pi/8$ Ancilla Factory533.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories594Datapath Variations614.1Network Model614.1.2Purification63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 0.1 |          | -                                                             |    |

| 3.1.3       Encoded Ancilla Preparation       41         3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Rubit Fidelity When Multiplexing       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla Factories       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.2       Purification       63                                                                              |   |     | -        |                                                               |    |

| 3.1.4       Fault Tolerant $\pi/8$ Gate       42         3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Rchitectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61       61         4.1       Network Model       61       61         4.1.2       Purification       63                                                                                                                                        |   |     |          |                                                               |    |

| 3.1.5       Fault Tolerant $\pi/2^k$ Gates       43         3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded $\pi/8$ Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1.1       Network Model       61         4.1.2       Purification       61                                                                                                                                                                                                           |   |     |          |                                                               |    |

| 3.2       Benchmark Characteristics: Ancilla Need       44         3.2.1       Benchmarks       45         3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1.1       Network Model       61         4.1.2       Purification       61                                                                                                                                                                                                                                                                                                                                     |   |     |          | Fault Tolerant $\pi/9$ Gates                                  |    |

| 3.2.1Benchmarks453.2.2QEC Circuit Characteristics453.2.3Non-Transversal One-Qubit Gates473.3Ancilla Factory Layout473.3.1Simple Ancilla Factories483.3.2Encoded Zero Ancilla Factory493.3.3Encoded $\pi/8$ Ancilla Factory533.4Qubit Fidelity When Multiplexing553.4Architectural Trade-offs563.4.1Matching Production to Need563.4.2Latency/Area Evaluation573.4.3Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories594Datapath Variations614.1Network Model614.1.2Purification63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 3.2 |          |                                                               | -  |

| 3.2.2       QEC Circuit Characteristics       45         3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1.1       Network Model       61         4.1.2       Purification       61                                                                                                                                                                                                                                                                                                                                     |   | 0.2 |          |                                                               |    |

| 3.2.3       Non-Transversal One-Qubit Gates       47         3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded Zero Ancilla Factory       53         3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.2       Purification       61                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | -        |                                                               |    |

| 3.3       Ancilla Factory Layout       47         3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded $\pi/8$ Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     | -        | 6                                                             |    |

| 3.3.1       Simple Ancilla Factories       48         3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded $\pi/8$ Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla Factories       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 3.3 |          |                                                               |    |

| 3.3.2       Encoded Zero Ancilla Factory       49         3.3.3       Encoded $\pi/8$ Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1.1       Network Model       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     |          |                                                               |    |

| 3.3.3       Encoded $\pi/8$ Ancilla Factory       53         3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       57         Factories       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     | 3.3.2    | -                                                             | 49 |

| 3.3.4       Qubit Fidelity When Multiplexing       55         3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     | 3.3.3    | *                                                             | 53 |

| 3.4       Architectural Trade-offs       56         3.4.1       Matching Production to Need       56         3.4.2       Latency/Area Evaluation       56         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | 3.3.4    |                                                               | 55 |

| 3.4.2       Latency/Area Evaluation       57         3.4.3       Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories       59         4       Datapath Variations       61         4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 3.4 | Archit   |                                                               | 56 |

| 3.4.3 Qalypso: Microarchitectural Implications of Pipelined Ancilla<br>Factories       59         4 Datapath Variations       61         4.1 Network Model       61         4.1.1 Network Components       61         4.1.2 Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     | 3.4.1    | Matching Production to Need                                   | 56 |

| Factories       59         4 Datapath Variations       61         4.1 Network Model       61         4.1.1 Network Components       61         4.1.2 Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     | 3.4.2    | Latency/Area Evaluation                                       | 57 |

| 4 Datapath Variations       61         4.1 Network Model       61         4.1.1 Network Components       61         4.1.2 Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | 3.4.3    | Qalypso: Microarchitectural Implications of Pipelined Ancilla |    |

| 4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     |          | Factories                                                     | 59 |

| 4.1       Network Model       61         4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4 | Dat | anath    | Variations                                                    | 61 |

| 4.1.1       Network Components       61         4.1.2       Purification       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | × |     | -        |                                                               |    |

| 4.1.2  Purification  .  .  .  .  .  .  .  .  .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |     |          |                                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     |          | 1                                                             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | 4.1.3    |                                                               | 65 |

|          |       | 4.1.4 Chain Teleportation                               | 66  |

|----------|-------|---------------------------------------------------------|-----|

|          |       | 4.1.5 Structuring Global Communication                  | 67  |

|          | 4.2   | Compute Region Layout                                   | 69  |

|          |       | 4.2.1 Designing the Interior of a Compute Region        | 69  |

|          |       | 4.2.2 Interfacing with the Network                      | 70  |

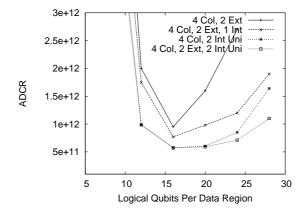

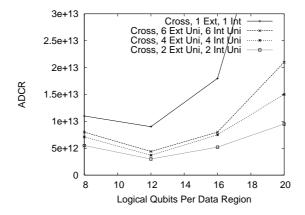

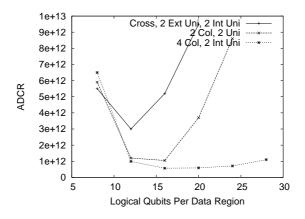

|          |       | 4.2.3 Choosing Between Layouts                          | 71  |

|          | 4.3   | Sizing Ancilla Factories and the Teleport Network       | 73  |

|          | 4.4   | Summary and Findings                                    | 75  |

| <b>5</b> | Mar   | pping Quantum Circuits to Qalypso                       | 76  |

|          | 5.1   | Overview of Mapping Techniques                          | 78  |

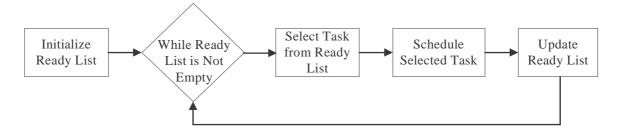

|          | 5.2   | Priority List Scheduling                                | 79  |

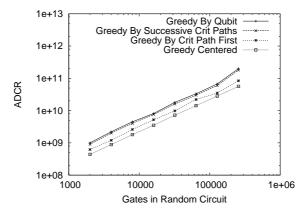

|          |       | 5.2.1 Vertex Priorities                                 | 80  |

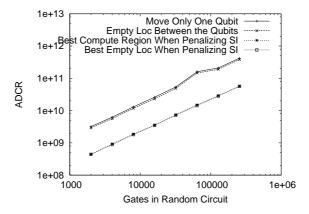

|          |       | 5.2.2 Options for "Best" Gate Location                  | 82  |

|          |       | 5.2.3 Issues with Naive Mapping                         | 83  |

|          | 5.3   | Home Assignment By Circuit Analysis                     | 85  |

|          | 0.0   | 5.3.1 Random Home Assignment                            | 86  |

|          |       | 5.3.2 Critical Qubit-Based Home Assignment              | 86  |

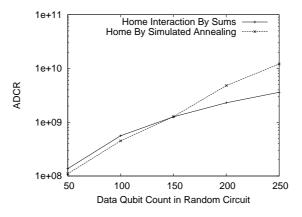

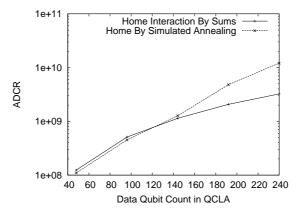

|          |       | 5.3.3 Interaction-Based Home Assignment                 | 86  |

|          |       | 5.3.4 Comparison Between Deterministic Techniques       | 87  |

|          | 5.4   | Home Assignment By Simulated Annealing                  | 89  |

|          |       | 5.4.1 Classical Simulated Annealing                     | 89  |

|          |       | 5.4.2 Quantum Simulated Annealing                       | 90  |

|          |       | 5.4.3 Comparison with Previous Techniques               | 91  |

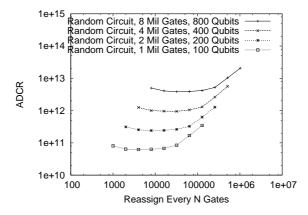

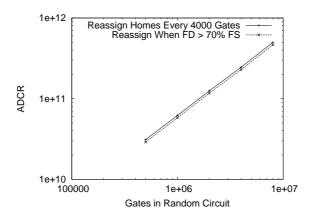

|          | 5.5   | Reassigning Homes for Longer Runs                       | 93  |

|          | 5.6   | Summary of Mapping Techniques                           | 97  |

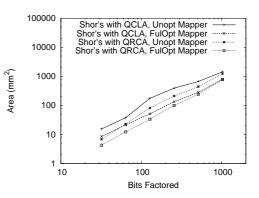

| 6        | Map   | pping Large Circuits                                    | 98  |

|          | 6.1   | Unoptimized and Optimized Mappers                       | 98  |

|          | 6.2   | Quantum Addition Circuits                               | 99  |

|          |       | 6.2.1 Quantum Ripple Carry Adder                        | 99  |

|          |       | 6.2.2 Quantum Carry Lookahead Adder                     | 101 |

|          | 6.3   |                                                         | 103 |

|          | 6.4   | Future Work                                             | 103 |

|          |       | 6.4.1 Laser Limitations                                 | 104 |

|          |       | 6.4.2 Classical Control Hardware for Ballistic Movement | 104 |

|          |       | 6.4.3 Alternative Technologies                          | 104 |

|          |       | 8                                                       | 105 |

|          | 6.5   |                                                         | 105 |

| Bi       | bliog | graphy                                                  | 107 |

### List of Figures

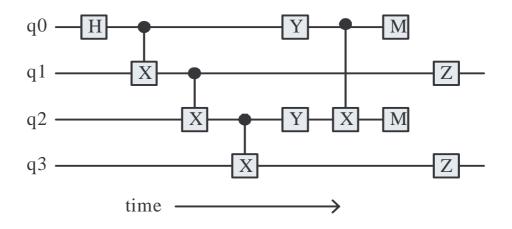

- 1.1 An example of a quantum circuit on four qubits with five one-qubit gates, four two-qubit gates and two measurement operations. . . . .

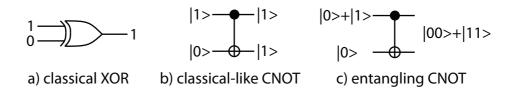

- 1.2 A comparison between a classical XOR and its quantum analog: the controlled-not or CNOT. The CNOT gate is reversible, thus the additional output. Figure b) outputs the XOR result to the bottom bit. Figure c) shows the same CNOT when the input is a quantum superposition. In this case the output is an *entangled* qubit state, not representable as independent qubit values for the two outputs. . . .

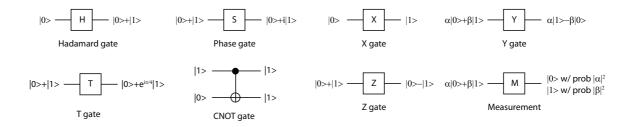

- 1.3 Basic gates for quantum circuits: this is a set of gates which supports a universal quantum computing model. The Hadamard gate converts bit values to phase values and vice versa. The phase, T and Z gates rotate the phase of the "1" qubit value by different angles. The CNOT gate is the same as shown in Figure 1.2 and performs the XOR functionality. The measurement "gate" measures a quantum state, returning a 1 or 0 and collapses any superposition to that value as well. The X is a bit flip, Z a phase flip, and Y a combination of both. The X, Y, Z, and phase gates can be generated by the other gates shown here but we include them since they are often included as physical primitives.

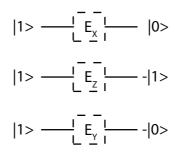

- 1.4 Types of errors corrected by quantum error correcting codes: The X error  $(E_X)$  flips the bit value, the Z error  $(E_Z)$  flips the phase difference between 1 and 0 by  $\pi$  radians, the Y error does both these things, flipping the bit and phase of the qubit.

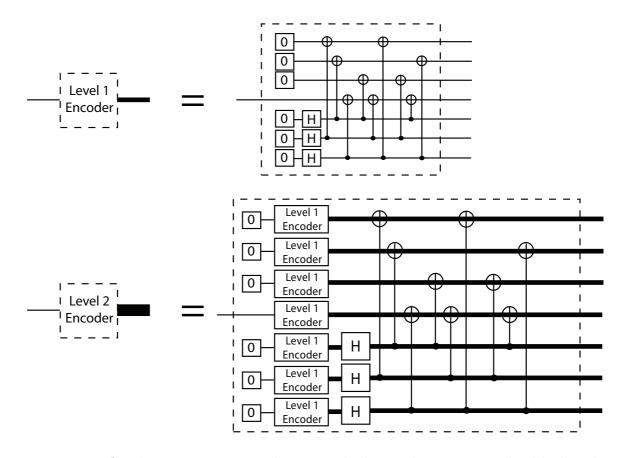

- 1.5 On the top, we are encoding a single data qubit into a 7 qubit block code (the [[7,1,3]] CSS code). The boxes with zeros indicate a preparation of a new qubit in the  $|0\rangle$  state, if the input qubit is a single physical qubit, this is a level 1 encoder, producing a level 1 logical qubit. The bottom figure is a level 2 encoder, using a level one encoder as a building block to produce a level 1 logical zero valued qubit.

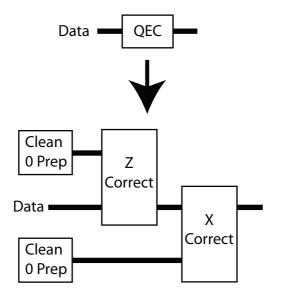

- 1.6 Steane-style error correction schemes have the following form: generate two encoded zero states then perform sequential Z and X correction operations.

8

3

4

5

6

7

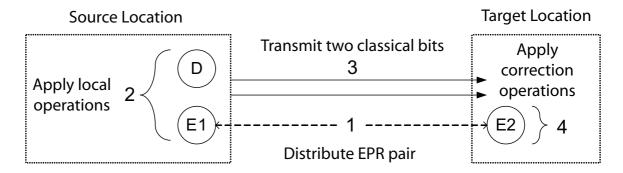

| 1.7   | Teleporting data qubit D to the target location requires $(1)$ a high-fidelity EPR pair $(E1/E2)$ , $(2)$ local operations at the source, $(3)$ trans- |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | mission of classical bits, and (4) correction operations to recreate D                                                                                 |    |

|       | from E2 at the target.                                                                                                                                 | 9  |

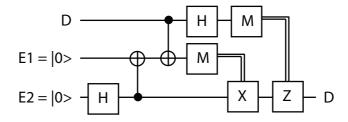

| 1.8   | Circuit representation for the teleportation operation: The first Hadamard<br>and CNOT gates prepare qubits E1 and E2 in the EPR state. One half       | [  |

|       | of the EPR pair is CNOTed with the data followed by a Hadamard and                                                                                     |    |

|       | measurements. The measurement results (classical information repre-                                                                                    |    |

|       | sented by double bit lines) are used to apply X and Z gates to adjust                                                                                  |    |

|       | the final state                                                                                                                                        | 10 |

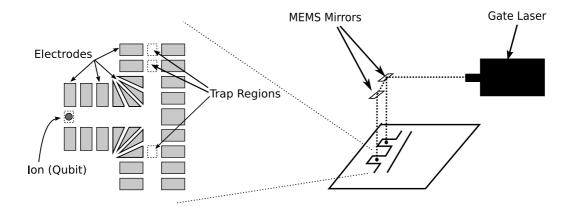

| 1.9   | Simplified ion trap technology view. Ions (qubits) are trapped between                                                                                 |    |

|       | electrodes in the trap regions. Ballistic movement of ions is performed                                                                                |    |

|       | by changing the voltages of the electrodes. A laser is routed to the                                                                                   |    |

| 1 10  | location of the ions to perform a gate                                                                                                                 | 11 |

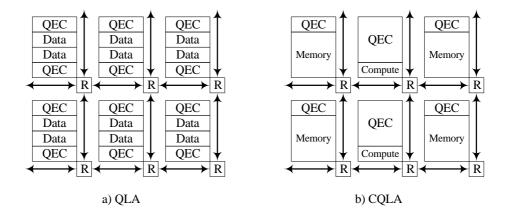

| 1.10  | Two architectures from prior work: a) The Quantum Logic Array (QLA) consists of a mesh grid of tiles linked by routers (R) to im-                      |    |

|       | plement long distance communication. Each tile has room for two                                                                                        |    |

|       | encoded data qubits and quantum error correction (QEC) resources                                                                                       |    |

|       | for each. b) The Compressed Quantum Logic Array diversifies into                                                                                       |    |

|       | two types of tiles: Memory tiles in which qubits are idle and don't                                                                                    |    |

|       | need to be error corrected as often and Compute tiles which require                                                                                    |    |

| 1 1 1 | relatively more QEC resources per data qubit.                                                                                                          | 14 |

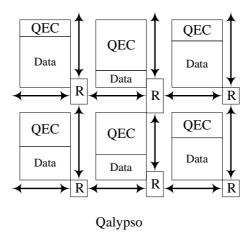

| 1.11  | Qalypso is a malleable architecture consisting of components similar<br>to those in (C)QLA. By allowing the datapath to be varied somewhat             |    |

|       | while mapping a quantum circuit, we may better fine tune the end result.                                                                               | 15 |

|       | while mapping a quantum circuit, we may better file tule the end result.                                                                               | 10 |

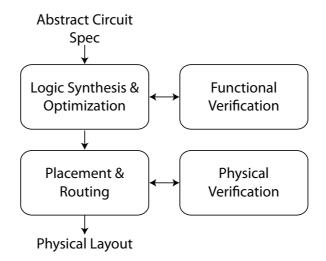

| 2.1   | Simplified view of a classical computer-aided design flow. A user-                                                                                     |    |

|       | specified application circuit specification is first synthesized into some                                                                             |    |

|       | sort of gate network, then physical components are geometrically mapped                                                                                |    |

|       | to a substrate to make physical design. Verification steps ensure equiv-<br>alence between stages.                                                     | 20 |

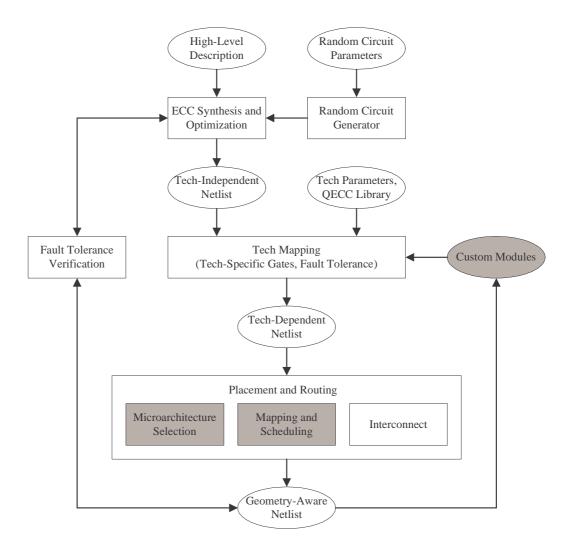

| 2.2   | A high level view of our computer-aided design flow for quantum cir-                                                                                   | 20 |

| 2.2   | cuits. The highlighted blocks denote the contributions focused on in                                                                                   |    |

|       | this work.                                                                                                                                             | 23 |

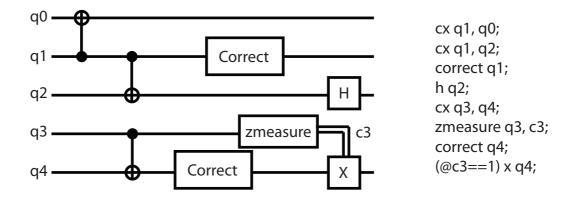

| 2.3   | A quantum circuit and the equivalent QASM instruction stream rep-                                                                                      |    |

|       | resenting it                                                                                                                                           | 25 |

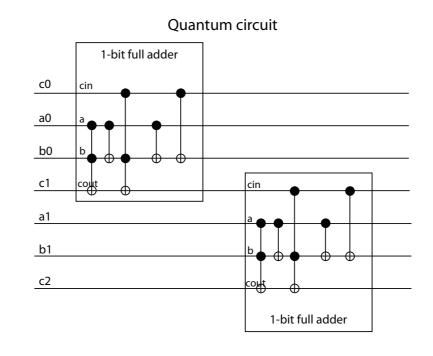

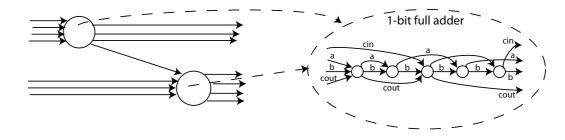

| 2.4   | Gate networks are represented as linked, modular dataflow graphs.                                                                                      |    |

|       | In this example, the top level graph consists of two nodes that each                                                                                   |    |

|       | correspond to a 1-bit full adder. They both refer to the 1-bit full adder                                                                              | 07 |

|       | module dataflow graph                                                                                                                                  | 27 |

vi

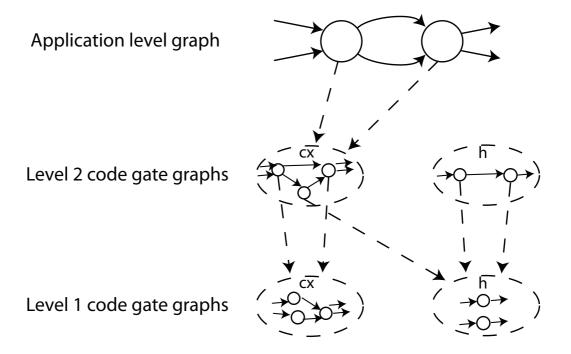

| 2.5        | Hierarchical dataflow graphs are used to represented different levels of QEC encodings. In this example we have the 2 gate application circuit encoded in 2 levels of codes. Each code has a library of graphs, each                                                                                                                                                                                                                          |          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

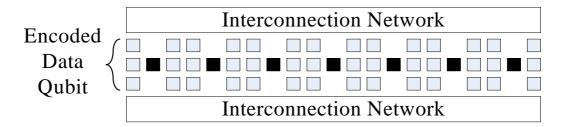

| 2.6        | graph implementing an encoded version of one gate type The basic building blocks of our ion trap layouts. Each <i>macroblock</i> consists of 3x3 electrodes or spaces to provide functionality as a straight                                                                                                                                                                                                                                  | 28       |

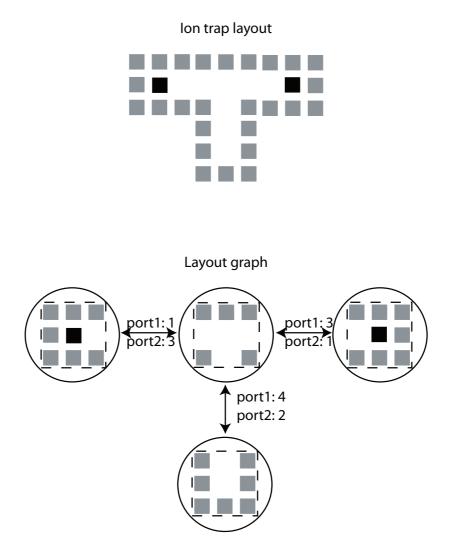

| 2.7<br>2.8 | channel, a gate, a turn, or an intersection                                                                                                                                                                                                                                                                                                                                                                                                   | 31<br>32 |

| 2.9        | with respect to each other                                                                                                                                                                                                                                                                                                                                                                                                                    | 33       |

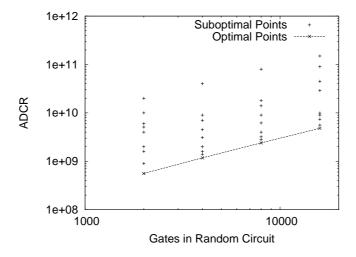

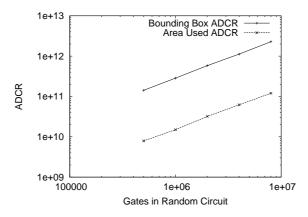

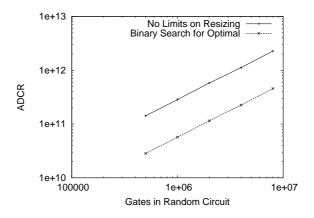

| 2.10       | instantiate two of them in different positions and orientations For a given input circuit, our CAD flow iterates through various datapath configurations, each of which produces a value for ADCR. The best, or <i>ADCR-optimal</i> , hardware configuration is selected                                                                                                                                                                      | 35<br>38 |

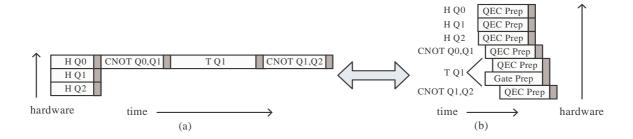

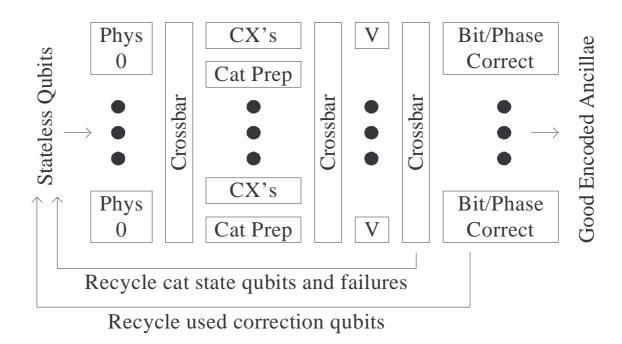

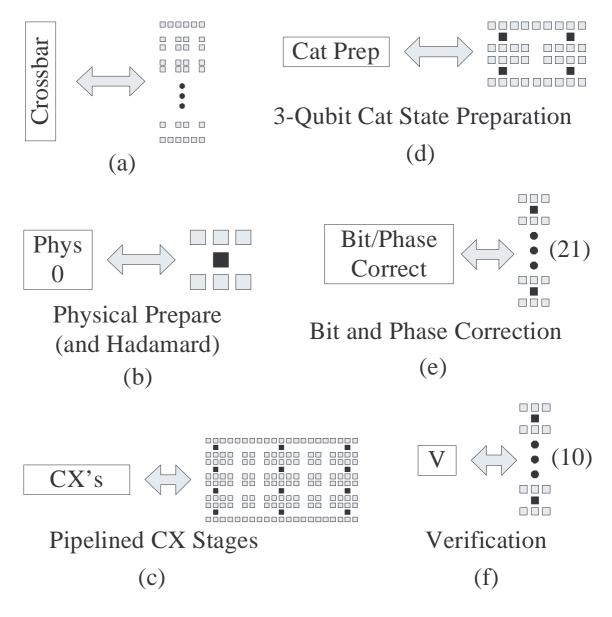

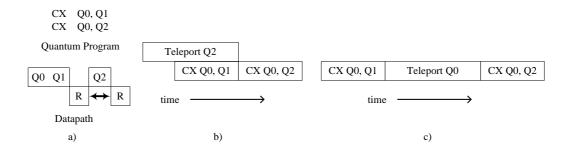

| 3.1        | (a) Standard implementation of a circuit involving qubits Q0, Q1 and Q2. Only the grey blocks represent interactions with actual data. The bulk of the critical path involves independent ancilla preparation. (b) An optimized version of the circuit in which ancilla preparation is pulled off the critical path through use of increased hardware. Here, the speed of the computation is limited only by data dependencies (grey blocks). | 40       |

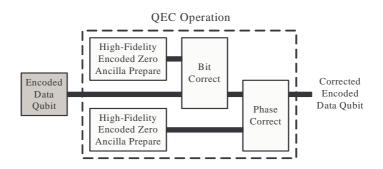

| 3.2        | A quantum error correcting (QEC) operation is composed of a <i>bit-flip</i> correction and a <i>phase-flip</i> correction, corresponding to the two types of errors that can happen to a qubit. The thick bars represent encoded                                                                                                                                                                                                              |          |

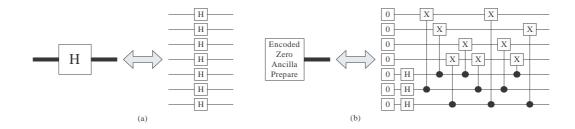

| 3.3        | qubits                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40       |

| 3.4        | qubit                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41<br>42 |

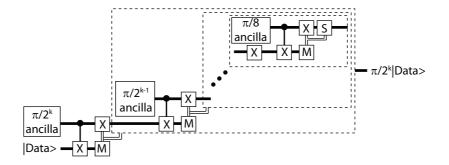

- 3.5 (a) Applying an encoded π/8 gate on an encoded data qubit involves creating an encoded π/8 ancilla and performing some transversal gates.

(b) Creating the encoded π/8 ancilla used in the circuit in (a) requires an encoded zero ancilla, a 7-qubit cat state (a specially prepared qubit set) and a series of transversal gates. Note that the π/8 gate near the far right is transversal but does not implement an encoded π/8 gate.

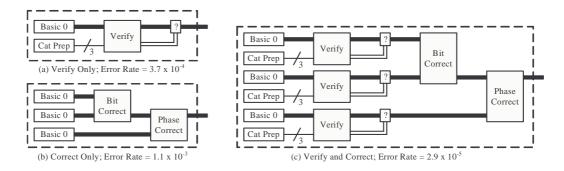

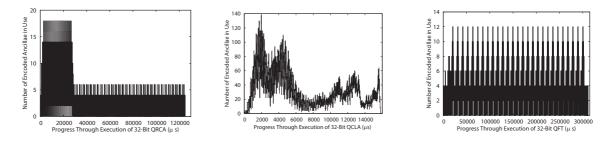

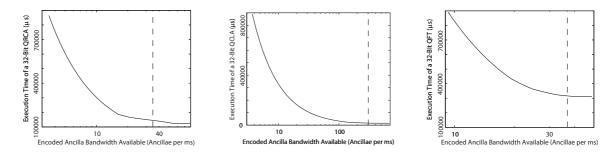

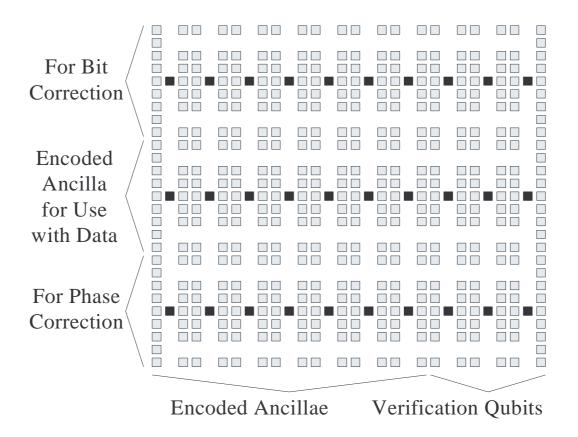

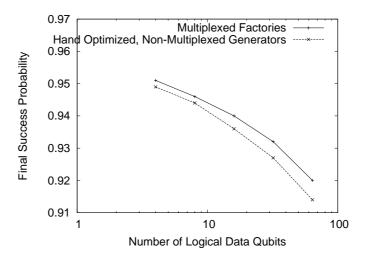

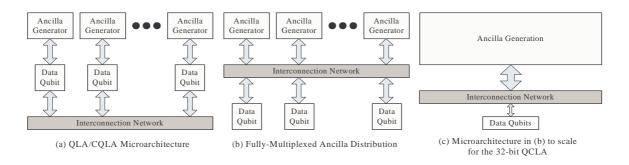

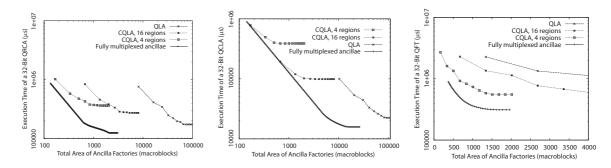

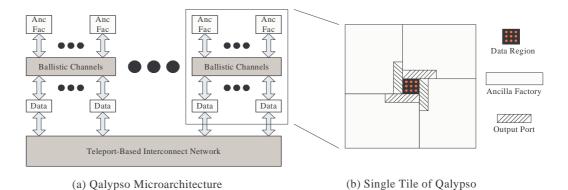

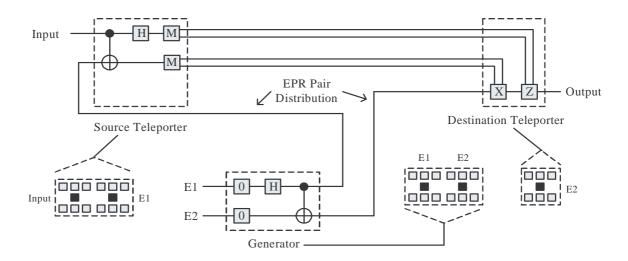

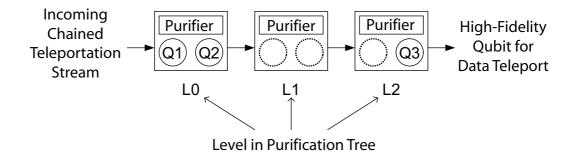

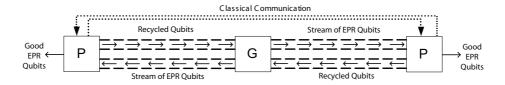

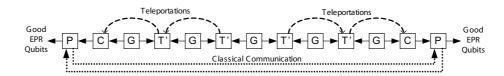

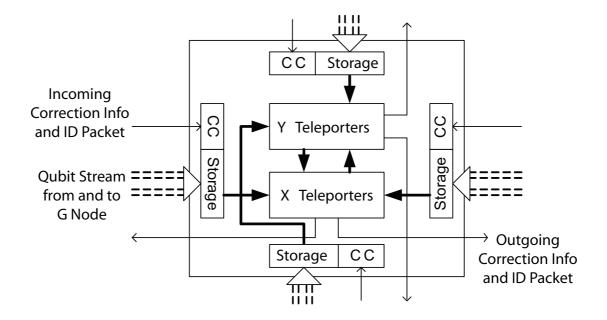

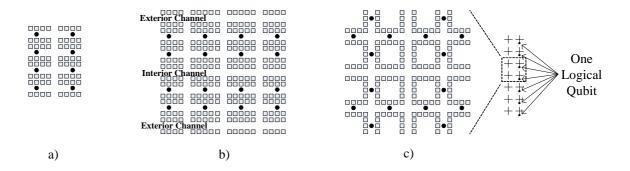

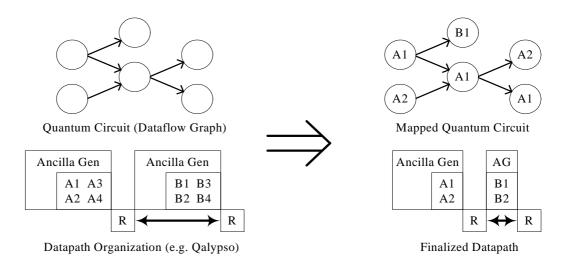

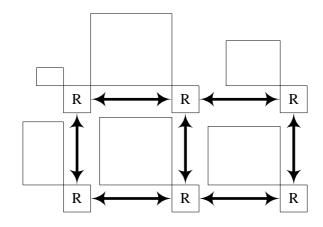

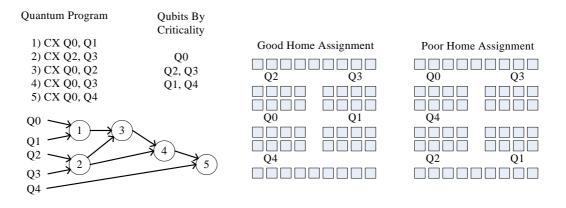

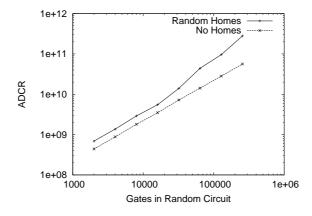

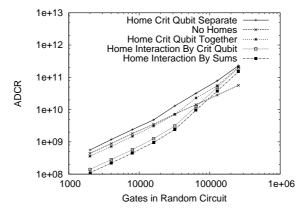

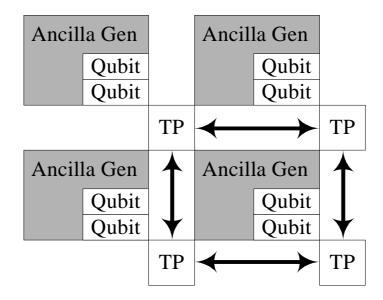

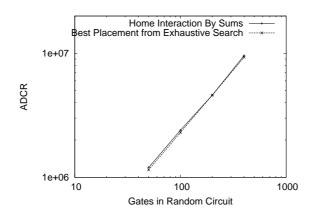

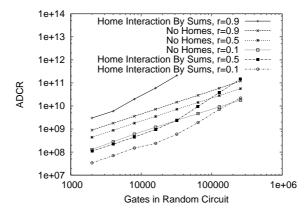

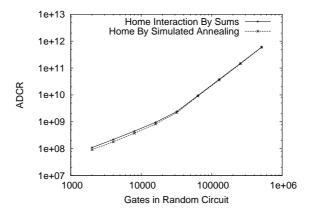

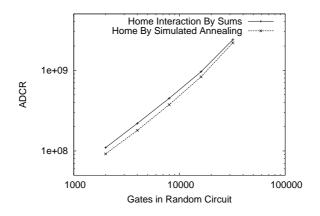

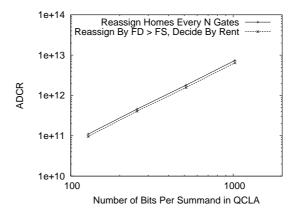

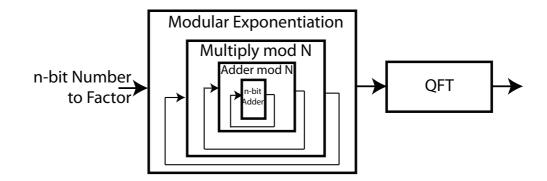

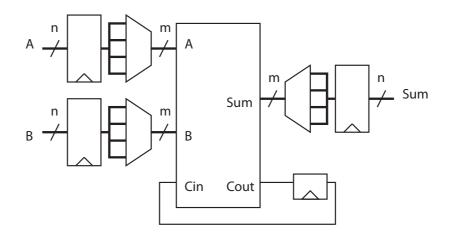

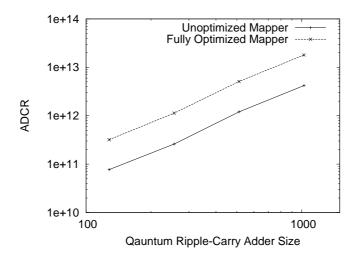

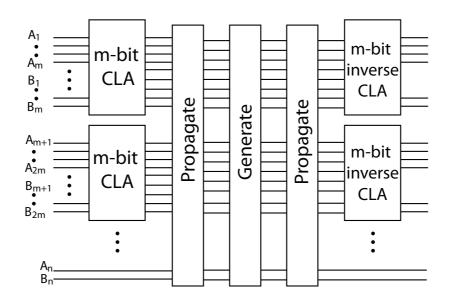

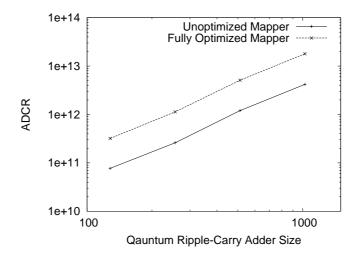

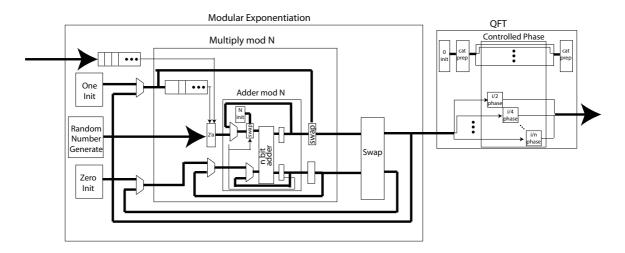

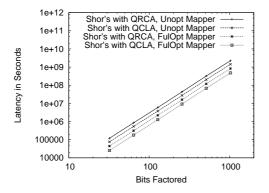

- 43Fault tolerant  $\pi/2^k$  gates can be performed recursively with a cascade 3.6of  $\pi/2^i | i = 3...k$  ancilla factories and k - 2 CX and X gates. Each measure gate output controls both the single qubit X gate and the compound gate involving more ancilla factories. Each measurement has a equal chance of giving the "correct" state, in which the remaining circuit is skipped or a "wrong" state in which a larger rotation has to be done to adjust the state. The actual output data from the circuit connects to the first quantum bitline associated with a correct measurement. 443.7Encoded zero ancilla needs for the QRCA (left), the QCLA (middle) and QFT (right) to run at the speed of data. 46 The execution time of the QRCA (left), the QCLA (middle) and the 3.8 QFT (right) as a function of a steady throughput of encoded zero ancillae. The vertical line in each shows the average bandwidth for 473.9An ancilla factory for the circuit in Figure 3.4c. Each row of gates generates and verifies one of the three encoded zero ancillae, then bit 483.10 A fully pipelined encoded zero ancilla creation unit implementing the circuit in Figure 3.4c. 493.11 A layout of each unit in Figure 3.10. 503.12 a) Ancilla production proposed in prior work: Each data qubit location is adjacent to an In-Place Ancilla Generator which produces encoded ancillae exclusively for that location. b) Multiplexed Ancilla Factories: Data qubits are more tightly packed together, with ports to Ancilla Factories at the edges of the Compute Region. (not to scale) . . . . 54