# Compilation Techniques for Embedded Data Parallel Languages

Bryan Catanzaro

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2011-45 http://www.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-45.html

May 11, 2011

# Copyright © 2011, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Acknowledgement

This research has been supported by a National Science Foundation Graduate Research Fellowship, an NVIDIA Graduate Fellowship, a Qualcomm Innovation Fellowship, the Gigascale Research Center, and the Parallel Computing Laboratory, which itself is supported by Microsoft (Award #024263), Intel (Award #024894), and by matching funding from U.C. Discovery (Award #DIG07-10227), with additional support from affiliates National Instruments, NEC, Nokia, NVIDIA, and Samsung.

#### Compilation Techniques for Embedded Data Parallel Languages

by

Bryan Christopher Catanzaro

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Kurt W. Keutzer, Chair Professor David A. Patterson Professor Sara McMains

Spring 2011

# Compilation Techniques for Embedded Data Parallel Languages

Copyright 2011 by Bryan Christopher Catanzaro

#### **Abstract**

Compilation Techniques for Embedded Data Parallel Languages

by

Bryan Christopher Catanzaro

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kurt W. Keutzer, Chair

Contemporary parallel microprocessors exploit Chip Multiprocessing along with Single Instruction, Multiple Data parallelism to deliver high performance on applications that expose substantial fine-grained data parallelism. Although data parallelism is widely available in many computations, implementing data parallel algorithms in low-level efficiency languages such as C++ is often a difficult task, since the programmer is burdened with mapping data parallelism from an application onto the hardware structures designed to execute it. Languages specifically designed for data parallelism, such as NESL, aim to improve programmer productivity by allowing the programmer to express computation as a composition of data parallel primitives, such as map, reduce and scan. However, efficiently compiling nested data parallel computations to contemporary parallel microprocessors is challenging.

Additionally, the rise of productivity languages, such as Ruby and Python, has facilitated the construction of domain-specific embedded languages. These embedded languages employ familiar syntactic constructs, which eases the task of learning a new programming environment, while also retaining the full capabilities of the host language. This work capitalizes on the productivity of domain-specific embedded languages as well as the nested data parallel abstraction to create a programming environment that is both productive and efficient on contemporary parallel microprocessors. We describe Copperhead, a high-level data parallel language embedded in Python. The Copperhead programmer writes parallel computations via composition of familiar data parallel primitives supporting both flat and nested data parallel computation on arrays of data. Copperhead programs are expressed in a subset of the widely used Python programming language and interoperate with standard Python modules, including libraries for numeric computation, data visualization, and analysis.

Compiling data parallel computations requires analyses and transformations to schedule data parallel operations onto a target platform. We discuss the language, compiler, and runtime features that enable Copperhead to efficiently do so. We define the restricted subset of Python that Copperhead supports and introduce the program analysis techniques and transformations necessary for compiling Copperhead code into efficient low-level implementations. We demonstrate that indiscriminate use of the flattening or vectorization transform, common to data parallel compilers, is inefficient on contemporary microprocessors, and we advocate a more direct mapping of nested data parallel operations onto the natural parallelism hierarchy

provided by today's parallel platforms. We show how this direct mapping allows a data parallel compiler to capitalize on hierarchical on-chip memory structures, as well as perform data parallel primitive fusion in order to gain efficiency. We outline the runtime support that allows Copperhead programs to efficiently interoperate with standard Python modules.

We demonstrate the effectiveness of our techniques with several examples targeting the CUDA platform for parallel programming on graphics processors. Copperhead code is concise, on average requiring 3.6 times fewer lines of code than CUDA, and the compiler generates efficient low-level implementations, yielding 45-100% of the performance of hand-crafted, well optimized CUDA code. Copperhead provides an efficient and productive way to program parallel microprocessors.

To Jena

# **Contents**

| Lis | List of Figures |                                   |      |  |  |

|-----|-----------------|-----------------------------------|------|--|--|

| Lis | st of Ta        | ables                             | viii |  |  |

| 1   | Intro           | oduction                          | 1    |  |  |

|     | 1.1             | The Implementation Gap            | 3    |  |  |

|     | 1.2             | Copperhead                        | 5    |  |  |

|     | 1.3             | Contributions                     | 6    |  |  |

|     | 1.4             | Outline                           | 7    |  |  |

| 2   | Back            | rground                           | 9    |  |  |

|     | 2.1             | Data Parallelism                  | 9    |  |  |

|     |                 | 2.1.1 Data Parallel Architectures | 10   |  |  |

|     |                 | 2.1.2 Contemporary Processors     | 11   |  |  |

|     |                 | 2.1.3 Parallelism Hierarchy       | 11   |  |  |

|     | 2.2             | Embedded Languages                | 14   |  |  |

|     | 2.3             | Data Parallel Programming Models  | 16   |  |  |

|     | 2.4             | Summary                           | 17   |  |  |

| 3   | The             | Copperhead Language               | 18   |  |  |

|     | 3.1             | Restricted Subset of Python       | 19   |  |  |

|     |                 | 3.1.1 Expressions                 | 20   |  |  |

|     |                 | 3.1.2 Statements                  | 21   |  |  |

|     | 3.2             | Type System                       | 21   |  |  |

|     | 0               | 3.2.1 Definition                  | 22   |  |  |

|     | 3.3             | Side Effects                      | 24   |  |  |

|     | 0.0             | 3.3.1 Side Effects in Host Code   | 26   |  |  |

|     |                 | 3.3.2 Loops                       | 27   |  |  |

|     | 3.4             | Scoping and Ordering              | 27   |  |  |

|     | 3.5             | Closures                          | 28   |  |  |

|     | 3.6             | Data-Parallel Primitives          | 29   |  |  |

|     | 0.0             | 3.6.1 map                         | 29   |  |  |

|     |                 | 3.6.2 zin                         | 30   |  |  |

|   |      | 3.6.3 reduce                                                       |

|---|------|--------------------------------------------------------------------|

|   |      | 3.6.4 scan                                                         |

|   |      | 3.6.5 gather                                                       |

|   |      | 3.6.6 scatter                                                      |

|   |      | 3.6.7 permute                                                      |

|   |      | 3.6.8 indices                                                      |

|   | 3.7  | Example programs                                                   |

|   |      | 3.7.1 Compressed Sparse Row Sparse Matrix Vector Multiplication 32 |

|   |      | 3.7.2 Radix Sort                                                   |

|   | 3.8  | Conclusion                                                         |

| 1 | Cam  | piling Data Parallel Languages 3'                                  |

| 4 |      | 1 0 0                                                              |

|   | 4.1  | Source to source compilation                                       |

|   | 4.2  | Normalized Form                                                    |

|   |      | 4.2.1 Closure Conversion                                           |

|   |      | 4.2.2 Single Assignment Conversion                                 |

|   |      | 4.2.3 Procedure Flattening                                         |

|   |      | 4.2.4 Expression Flattening                                        |

|   |      | 4.2.5 Inlining                                                     |

|   |      | 4.2.6 Final Result                                                 |

|   | 4.3  | Shape Analysis                                                     |

|   | 4.4  | Data Parallel Primitive Scheduling                                 |

|   |      | 4.4.1 Data Parallel Primitive Fusion                               |

|   | 4.5  | The Flattening Transform                                           |

|   | 4.6  | Quantifying the Flattening Transform                               |

|   |      | 4.6.1 Load Balancing                                               |

|   |      | 4.6.2 SIMD Effects                                                 |

|   |      | 4.6.3 Summary                                                      |

|   | 4.7  | Scheduling Methodology                                             |

|   | 4.8  | Phase Analysis and Scheduling                                      |

|   |      | 4.8.1 Phase Analysis                                               |

|   |      | 4.8.2 Phase Scheduling                                             |

|   |      | 4.8.3 Phase Analysis and Scheduling Example 6                      |

|   |      | 4.8.4 Limitations                                                  |

|   | 4.9  | Using On-chip Memories                                             |

|   | 4.10 | Structures of Arrays                                               |

|   | 4.11 | Conclusion                                                         |

| _ |      | - 1 In                                                             |

| 5 |      | Copperhead Runtime 73                                              |

|   | 5.1  | CUDA C++ Back End                                                  |

|   | 5.2  | Runtime                                                            |

|   |      | 5.2.1 Runtime Static Compilation                                   |

|   |      | 5.2.2 Places                                                       |

|     | 5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Data Structures795.3.1 Arbitrarily Nested Sequences795.3.2 Uniformly Nested Sequences80Foreign Function Interface81Runtime Overheads82Systems without compilers83Conclusion84 |

|-----|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | Resu                            | lts 85                                                                                                                                                                        |

|     | 6.1                             | Sparse Matrix Vector Multiplication                                                                                                                                           |

|     | 6.2                             | Preconditioned Conjugate Gradient Linear Solver                                                                                                                               |

|     | 6.3                             | Lanczos Eigensolver                                                                                                                                                           |

|     | 6.4                             | Quadratic Programming: Nonlinear Support Vector Machine Training 97                                                                                                           |

|     | 6.5                             | Productivity                                                                                                                                                                  |

|     | 6.6                             | Conclusion                                                                                                                                                                    |

| 7   | Conc                            | clusions 105                                                                                                                                                                  |

| •   | 7.1                             | Contributions                                                                                                                                                                 |

|     | , •                             | 7.1.1 Direct Mapping of Nested Data Parallelism                                                                                                                               |

|     |                                 | 7.1.2 Phase Analysis and Scheduling                                                                                                                                           |

|     |                                 | 7.1.3 Runtime Static Compilation                                                                                                                                              |

|     | 7.2                             | Availability                                                                                                                                                                  |

|     | 7.3                             | Future Work                                                                                                                                                                   |

|     | , .0                            | 7.3.1 Alternative Backends                                                                                                                                                    |

|     |                                 | 7.3.2 Autotuning                                                                                                                                                              |

|     |                                 | 7.3.3 Aspect Oriented Debugging                                                                                                                                               |

|     |                                 | 7.3.4 Usability Studies                                                                                                                                                       |

|     | 7.4                             | Conclusion                                                                                                                                                                    |

| Bib | oliogra                         | phy 111                                                                                                                                                                       |

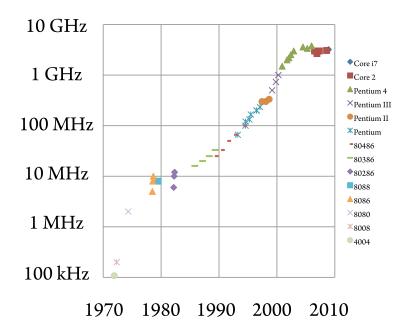

# List of Figures

| Historical Clock Speeds of Intel Microprocessors. Data from [44] The Implementation Gap | 2 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

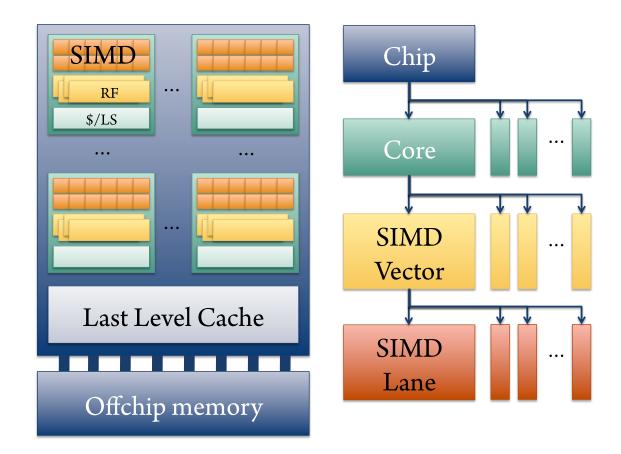

| Two representative processors                                                           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parallel Hierarchy                                                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

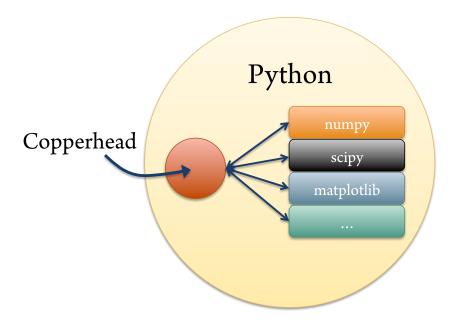

| Copperhead is an Embedded Subset of Python, designed to interoperate                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| with standard Python libraries for numeric computing                                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Grammar for Copperhead Expressions                                                      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Grammar for Copperhead Statements                                                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Well typed and ill-typed programs                                                       | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A grammar for the Copperhead type system                                                | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Describing Copperhead Types                                                             | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Example code with and without side effects                                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Python code with side effects                                                           | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Illustrating Closures                                                                   | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Procedure for computing $Ax$ for a matrix $A$ in CSR form and a dense vector            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

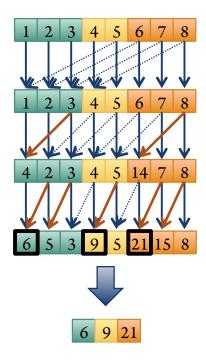

| Illustrating Radix Sort                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

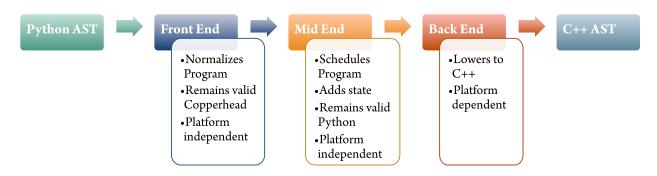

| Copperhead Compiler Flow                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Scaled vector addition before Closure Conversion                                        | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Scaled vector addition after Closure Conversion                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A procedure before Single Assignment Conversion                                         | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A procedure after Single Assignment Conversion                                          | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Scaled vector addition before procedure flattening                                      | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Scaled vector addition after procedure flattening                                       | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Scaled vector addition before expression flattening                                     | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                         | Two representative processors High level parameters of two representative processors Abstract Architecture Parallel Hierarchy  Copperhead is an Embedded Subset of Python, designed to interoperate with standard Python libraries for numeric computing Grammar for Copperhead Expressions Grammar for Copperhead Statements Well typed and ill-typed programs A grammar for the Copperhead type system Describing Copperhead Types Example code with and without side effects Python code with side effects Referencing procedure identifiers defined outside a Copperhead procedure Referencing data identifiers defined outside a Python procedure Dynamic scoping in Python Illustrating Closures Procedure for computing Ax for a matrix A in CSR form and a dense vector x. Underlined operations indicate potential sources of parallel execution. Radix sort in Copperhead Illustrating Radix Sort  Copperhead Compiler Flow Scaled vector addition before Closure Conversion |

| 4.9  | Scaled vector addition after expression flattening                               | 42 |

|------|----------------------------------------------------------------------------------|----|

| 4.10 | Example procedure before inlining                                                | 42 |

| 4.11 | Example procedure after inlining                                                 | 42 |

| 4.12 | SpMV procedure from Figure 3.13 after transformation by the front end            |    |

|      | compiler                                                                         | 43 |

| 4.13 | A program with indeterminate shape                                               | 44 |

| 4.14 | Fusion Example Code                                                              | 46 |

| 4.15 | Fusion Example Code after Normalization                                          | 47 |

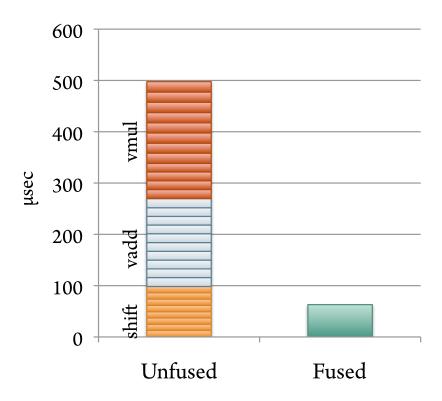

| 4.16 | The performance impact of data parallel primitive fusion                         | 48 |

| 4.17 | A nested sum operation                                                           | 49 |

| 4.18 | Executing a Segmented Reduction                                                  | 50 |

| 4.19 | Copperhead code for multi_norm                                                   | 52 |

| 4.20 | Copperhead-like code for the flattened version of multi_norm                     | 52 |

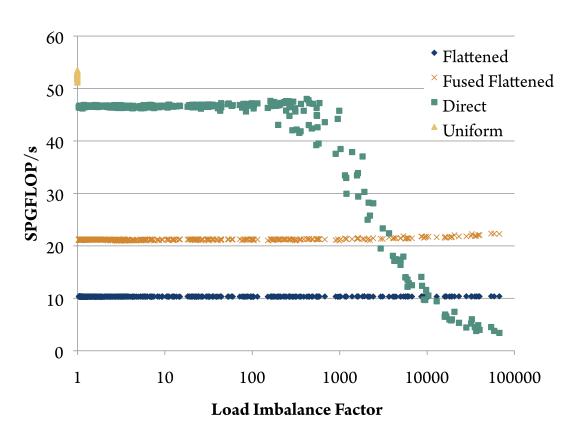

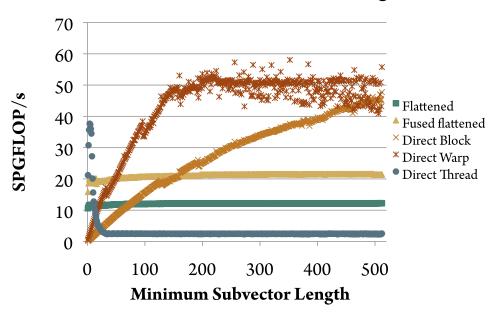

| 4.21 | Performance comparison of flattened versus direct mapped scheduling              | 55 |

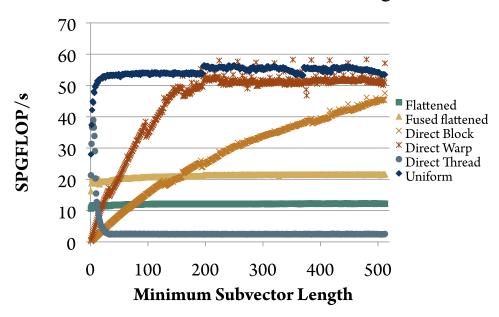

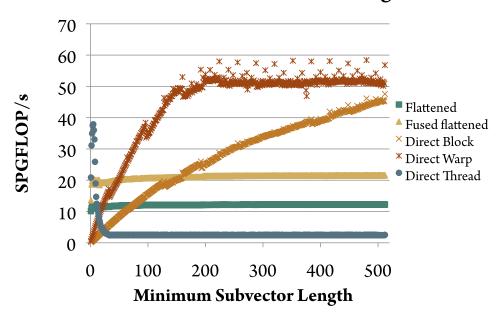

| 4.22 | Performance comparison of nested parallelism mapping strategies, $\psi=1$        | 57 |

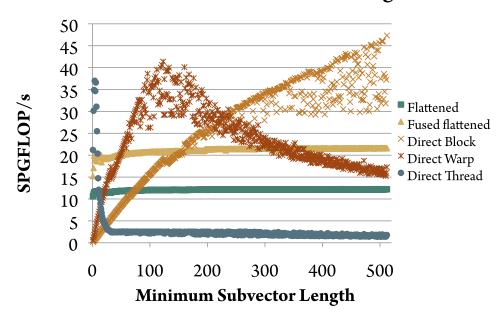

| 4.23 | Performance comparison of nested parallelism mapping strategies, $\psi=10$       | 58 |

| 4.24 | Performance comparison of nested parallelism mapping strategies, $\psi=100$ .    | 58 |

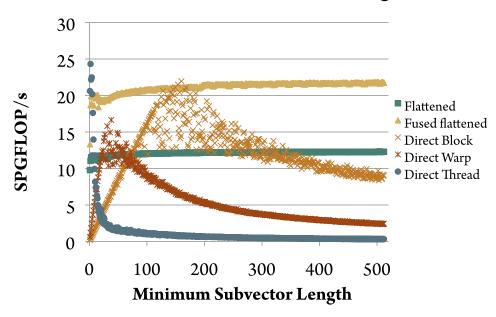

| 4.25 | Performance comparison of nested parallelism mapping strategies, $\psi=1000$     | 59 |

| 4.26 | Performance comparison of nested parallelism mapping strategies, $\psi = 10000$  | 59 |

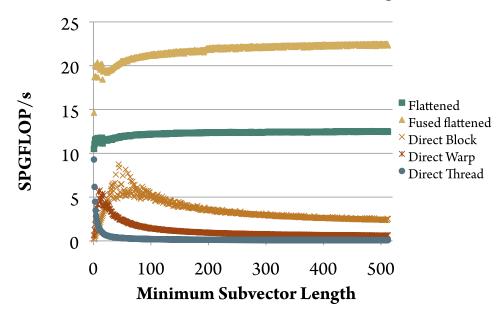

| 4.27 | Performance comparison of nested parallelism mapping strategies, $\psi = 100000$ | 60 |

| 4.28 | Simple flat data parallel example                                                | 67 |

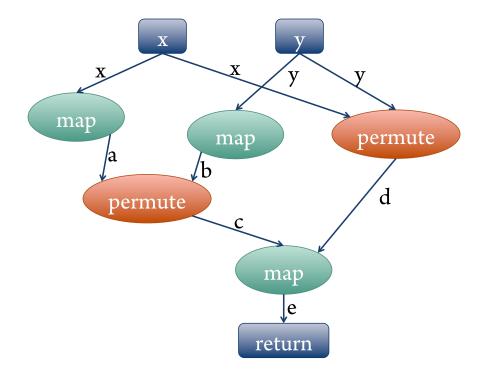

| 4.29 | Data Dependence graph for code in figure 4.28                                    | 68 |

| 4.30 | Analyzed and Scheduled data dependence graph for code in figure 4.28             | 68 |

| 4.31 | Unfused primitives                                                               | 69 |

| 4.32 | Closed over data may be intensively reused                                       | 70 |

| 4.33 | Creating an Array of Structures                                                  | 71 |

|      |                                                                                  |    |

| 5.1  | Normalized, scheduled output of Mid-end compiler                                 | 74 |

| 5.2  | Sample CUDA C++ code generated for spmv_csr. Ellipses () indicate in-            |    |

|      | cidental type and argument information elided for brevity                        | 75 |

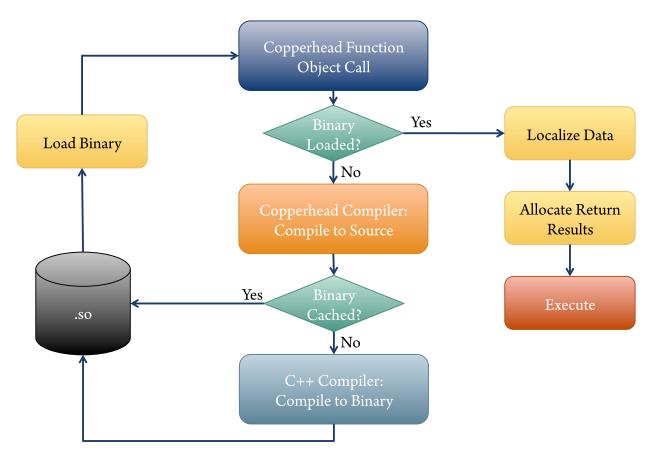

| 5.3  | Runtime Compilation                                                              | 77 |

| 5.4  |                                                                                  | 78 |

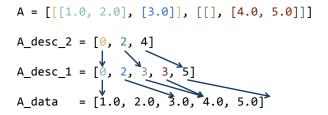

| 5.5  | Implementing an Arbitrarily Nested Sequence                                      | 79 |

| 6.1  | SpMV procedure for sparse matrices in ELL format                                 | 87 |

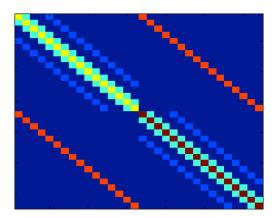

| 6.2  | Sparse Matrix and its Representation in ELL Format                               | 87 |

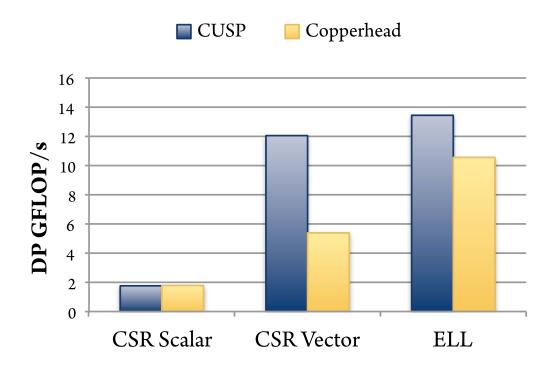

| 6.3  | Average Double Precision Sparse Matrix Vector Multiply Performance               | 89 |

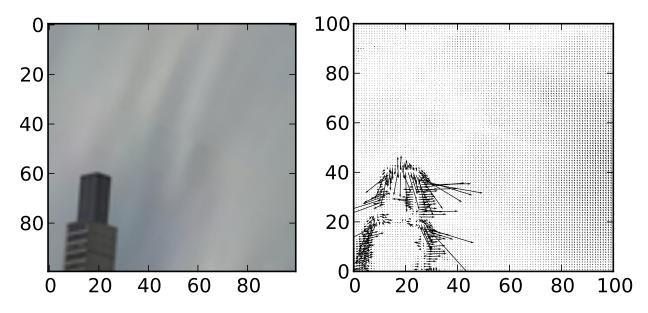

| 6.4  | Left: closeup of video frame. Right: gradient vector field for optical flow      | 90 |

| 6.5  | Structure of the matrix from the optical flow problem                            | 90 |

| 6.6  | Forming and applying the block Jacobi preconditioner                             | 92 |

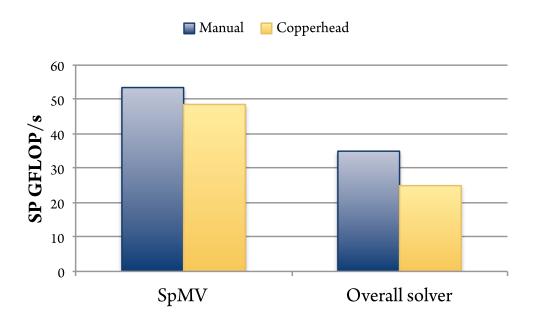

| 6.7  | Initializing the Conjugate Gradient Iterations                                   | 93 |

| 6.8  | Preconditioned Conjugate Gradient Iteration                                      | 94 |

| 6.9  | Performance on Preconditioned Conjugate Gradient Solver                          | 95 |

| 6.10 | Lanczos eigensolver iteration                                                    | 96 |

| -    |                                                                                  |    |

| 6.11 | RBF Kernel evaluation                                        |  |  |  | 99  |

|------|--------------------------------------------------------------|--|--|--|-----|

| 6.12 | Reduction operator for computing the Arg Extrema of a vector |  |  |  | 100 |

| 6.13 | SVM Training iteration                                       |  |  |  | 101 |

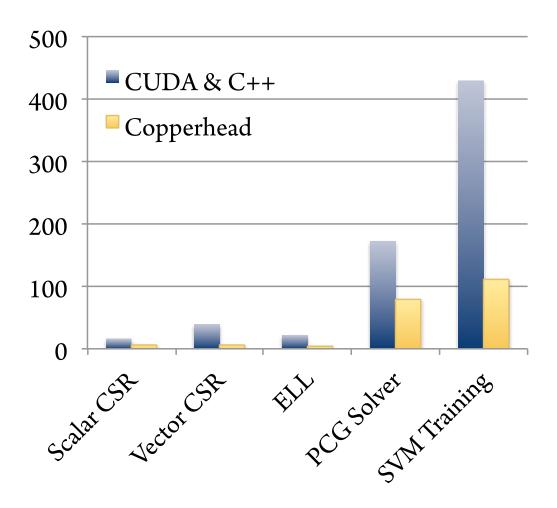

| 6.14 | Standardized Lines of Code for Copperhead and C++ Programs   |  |  |  | 103 |

# **List of Tables**

| 3.1 | Basic monotypes in the Copperhead type system                                | 23  |

|-----|------------------------------------------------------------------------------|-----|

| 4.1 | Selected Partitionings and Performance                                       | 54  |

| 4.2 | The parallel hierarchy ${\cal P}$ provided by OpenCL and CUDA $\dots \dots$  | 63  |

| 4.3 | Completion and Directionality types for selected data parallel primitives at |     |

|     | the Distributed Level                                                        | 65  |

| 4.4 | Completion and Directionality types for selected data parallel primitives at |     |

|     | the Sequential Level                                                         | 65  |

| 5.1 | Runtime Overheads                                                            | 83  |

| 6.1 | Double Precision Sparse Matrix Vector Multiplication Performance in          |     |

|     | GFLOP/s                                                                      | 88  |

| 6.2 | Lanczos performance results                                                  | 97  |

| 6.3 | Support Vector Machine Training Performance                                  | 100 |

| 6.4 | Number of Lines of Code for Example Programs                                 | 102 |

### Acknowledgments

I'd like to thank my advisor, Kurt Keutzer, for his support, guidance and insight over the course of my time at Berkeley. Kurt went far beyond my expectations to make sure I felt comfortable and worked productively, and his advice has been instrumental in guiding this work, as well as preparing me for the future.

I'd also like to thank Michael Garland from NVIDIA Research, who made significant contributions to the design and implementation of Copperhead.

My work has been shaped by eight industrial internships; I'd like to thank Tom Fletcher for giving me my first exposure to the computer industry, as well as Kumar Anshumali, Herman Schmit, Pradeep Dubey, Jatin Chhugani, Sanjeev Kumar, Michael Garland and David Luebke for their mentorship.

Several academic instructors and advisors have broadened my horizons. I'd particularly like to thank Brent Nelson, Travis Oliphant, Tom Sederberg, Richard Frost, Raissa Solovyova, Rosalind Hall, Anna Muza and Karen Brotherson. They have enriched my understanding and challenged me to work harder, understand more deeply, and believe in myself. I'd also like to thank David Patterson and Sara McMains for serving on my dissertation committee and significantly improving this manuscript through their careful reading.

While at Berkeley, I've been privileged to collaborate with a stellar group of researchers, including Narayanan Sundaram, Bor-Yiing Su, Mark Murphy, Jike Chong, Yunsup Lee, Will Plishker, Kaushik Ravindran, NR Satish, Ekaterina Gonina, Chao-Yue Lai, Michael Anderson, and David Sheffield, as well as Armando Fox, David Patterson, Krste Asanović, James Demmel, and Kathy Yelick. Special thanks go to Henry Cook and Tyler Mecke, who contributed to the Copperhead project. Other graduate students in the department have made my experience at Berkeley lively and interesting, including Bryan Brady, Matt Moskewicz, Scott Weber, Andrew Mihal, Abhijit Davare, Elaine Cheong, Nathan Kitchen, Donald Chai, Christopher Batten, David Chinnery, and Doug Densmore, among others. Thanks to all for making my time here stimulating and productive.

Most importantly, I acknowledge my family: my wife Jena, my children Hyrum, Evelyn and Claire, and my parents Paul and Belinda. The sacrifices they have made in support of this work have made it possible, and their presence in my life gives me purpose.

# Introduction

Driven by the capabilities and limitations of modern semiconductor manufacturing, the computing industry is currently undergoing a massive shift towards parallel computing. For more than three decades, the increased integration capabilities provided by successive generations of semiconductor manufacturing yielded ever more capable sequential processors. During the 1990s alone, sequential processor performance improved by two orders of magnitude. These increases in processing power served as the foundation for advances in computing applications that have profoundly changed the way we live, learn, conduct business, and entertain ourselves.

However, during the 2000s, sequential processor performance improvements slackened [2]. This was due primarily to power consumption constraints – as processors became more and more complex, their power consumption increased superlinearly until it was no longer feasible to supply power and cooling. Figure 1.1 illustrates this trend by graphing the clock speed of Intel microprocessors as a function of time. Clock speeds increased at a rapid pace until around 2004, when the Prescott Pentium 4 processor was introduced at 3.8 GHz. After that point, clock speeds have remained stagnant for the past seven years. For the first time in the forty year history of the microprocessor, we find ourselves in an era where processor frequency has virtually ceased scaling. Of course, processor performance is only correlated with frequency; other architectural properties also influence single-threaded performance, and in fact, we have seen single-threaded performance improve, albeit at a reduced rate. However, it is clear that we are now in a new era, one that requires parallel software in order to take advantage of parallel hardware.

Instead of continuing to focus on sequential performance, microprocessor architects have turned their attention on power efficiency and single chip multiprocessing. By dialing back sequential performance by a few percent, architects have reaped large power savings per core, and then integrated larger numbers of cores into multicore and manycore processors. The aggregate performance of each of these assemblages of cores can be much higher than the power-limited performance that could have been reached by single-threaded processors alone – but taking advantage of parallel processors requires parallel software.

Ideally, we would be transitioning to parallel processing because breakthroughs in parallel programming models and applications had proven that parallel processing is successful and profitable. Instead, the shift towards parallel computing is actually a retreat from even more daunting problems in silicon manufacturing and computer architecture [2]. As a result, com-

Figure 1.1: Historical Clock Speeds of Intel Microprocessors. Data from [44]

putationally intensive applications must now be rewritten to be scalable and efficient on parallel platforms. Consequently, one of the preeminent challenges of the current computing era is to make parallel programming mainstream and successful.

Although parallel programming has a long and somewhat challenged history, the computing landscape is different this time, and so parallelism is much more likely to succeed.

First, thanks to the integration capabilities of modern semiconductor manufacturing, the nature of parallel implementation has changed. Previous efforts at parallel programming focused on clusters of multi-socket, multi-node systems. With such systems, the overhead of communication and synchronization often dominate the improved performance obtained through parallelism, leading to poor application scalability: increasing the number of cores in a system did not improve performance. Now that parallel processors are integrated into monolithic silicon devices that share the same off-chip memory, more algorithms and programming models can effectively exploit parallelism, since the cost of communication and synchronization has been reduced by orders of magnitude.

Second, the economics behind parallel processing have changed. Parallel processing used to require a large investment: if you wanted a machine with twice the parallelism, you needed to pay at least twice as much money to pay for the extra processors. Consequently, in order for parallelism to be considered successful, applications needed to show linear or near-linear scalability in order to justify hardware investments. The advent of on-chip multiprocessor architectures have changed this calculus, since they translate the increased integration capabilities provided by Moore's law directly into parallelism. Pollock and Gelsinger famously observed [35] that doubling the number of transistors in a sequential processor results in only about a

40% performance improvement. Accordingly, to stay on the same performance trend that we enjoyed during the sequential processing era, if we double the number of cores on the chip, we need demonstrate only 40% performance improvement to justify the investment. As a result, sub-linear performance scaling now makes sense, and so nowadays, virtually every processor on the market is parallel, including processors for mobile devices, such as smartphones and tablets. Parallelism is coming along essentially for free, it is ubiquitous, and does not require large investment or perfect scalability to be profitable.

Finally, this time around, we have no alternative. Earlier attempts to capitalize on parallel processing were less successful because sequential processors were improving so rapidly. If an application wasn't performing quickly enough, one could just wait for a year until a faster generation of sequential processors came out. Now that sequential processor performance increases have drastically slowed, we don't have the option of waiting for sequential processors to catch up with our performance needs. Instead, it's time to examine our applications for parallelism and find efficient parallel implementations.

The good news is that parallelism can actually be fairly easy to find and extract, if one uses the correct tools and mental models. The push to parallel software, albeit a significant change, is far from an impossible task. Parallelism is abundant, often derived from the properties of the computations we're trying to perform, which model, analyze, and synthesize large data sets consisting of many objects.

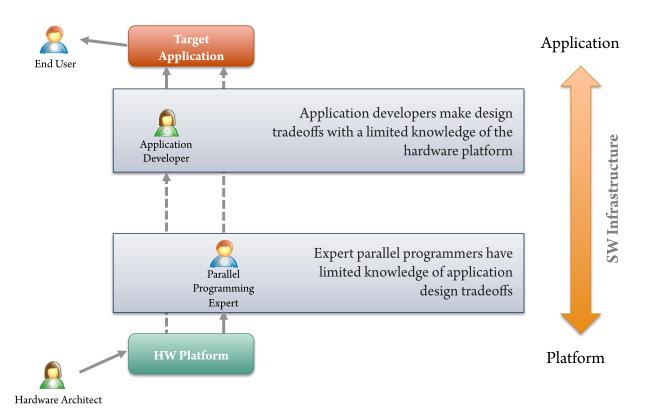

## 1.1 The Implementation Gap

Computer architects are now creating highly parallel architectures, the challenge is exploiting them efficiently and productively. Manual implementation of parallel programs using efficiency languages such as C and C++ can yield high performance, but at a large cost in programmer productivity. Some case studies show that productivity-oriented languages such as Ruby and Python are two to five times more productive than efficiency languages [46, 75]. Additionally, parallel programming in efficiency languages is often viewed as an esoteric endeavor, to be undertaken by experts only. Without higher-level abstractions that enable easier parallel programming, parallel processing will not be widely utilized.

Conversely, application developers do not have the means to capitalize on fine-grained, highly parallel microprocessors, which limits their ability to implement computationally intensive applications. Application developers require high productivity from programming environments, to enable algorithmic design space exploration and rapid application prototyping. Consequently, they often use highly productive programming languages and environments, such as Ruby, Python and MATLAB, despite the inefficient way these environments exploit computing resources.

Figure 1.2 illustrates this problem, which we call the implementation gap [82, 73, 25]. Closing the implementation gap requires creating software infrastructure that provides higher level abstractions to application developers that enable them to productively program their applications, but in a way that can be mapped to efficient parallel implementations. We argue that higher level data parallel abstractions can serve as a productive substrate for efficient parallel

Figure 1.2: The Implementation Gap

programming, enabling the creation of software infrastructure that bridges the implementation gap. We create such software infrastructure in the form of a compiler and runtime, embedded in the popular Python language. The programmer expresses computations at a much higher level of abstraction, and our compiler and runtime efficiently execute them on a parallel platform. Although computations expressed using our infrastructure are much more abstract than a low-level efficiency language, we can achieve performance within a factor of two of optimized code written in an efficiency language. This represents a step towards closing the implementation gap for parallel programming.

# 1.2 Copperhead

Although the need for higher-level parallel abstractions seems clear, perhaps less so are the abstractions that should be provided to bridge the implementation gap, since there are many potential abstractions that could be presented to productivity programmers. In our view, nested data parallelism, as introduced by languages such as NESL  $\lfloor 10 \rfloor$ , is particularly interesting. In data parallel languages, programmers express computation by using explicitly parallel operators that apply a computation element-wise across large sequences. Communication is expressed through data parallel primitives, such as reductions, scans, sorts, and compactions, which are also explicitly parallel. Although flat data parallel programming can be both highperformance and concise, its expressibility is limited. Many computations and data structures have a hierarchical structure, which is more naturally expressed by composing data parallel operations in a hierarchical fashion, operating on hierarchical data structures. For example, for sparse matrix vector multiplication, the matrix can be represented as a sequence of rows, each of which contains a sequence of non-zero elements. The computation involves applying a sparse vector dot product operation to each row of the matrix. The dot product operation itself can be expressed using data parallel primitives. Nested data parallelism is a natural way of expressing computation.

Nested data parallelism is abundant in many computationally intensive algorithms. It can be mapped efficiently to parallel microprocessors, which prominently feature hardware support for data parallelism. For example, mainstream x86 processors from Intel and AMD are adopting 8-wide vector instructions, Intel's Larrabee processor used 16-wide vector instructions, and modern Graphics Processing Units (GPUs) from NVIDIA and AMD use wider SIMD widths of 32 and 64, respectively. Consequently, programs that don't take advantage of data parallelism relinquish substantial performance.

Additionally, nested data parallelism as an abstraction explicitly exposes parallelism. In contrast to traditional auto-parallelizing compilers that must analyze and prove which operations can be parallelized and which can not, the compiler of a data-parallel language needs only to decide which operations to perform sequentially, and which to perform in parallel. Making these decisions involves mapping the nested data parallel operations onto the hierarchical structure of the parallel platform being targeted. The mechanisms by which we perform this mapping are crucial to achieving high performance, and are the central task of a data-parallel compiler.

Importantly, nested data parallel programs have a valid sequential interpretation, and are thus easier to understand and debug than parallel programs that expose race conditions and other complications of parallelism.

Motivated by these observations, Copperhead provides a set of nested data parallel abstractions, expressed in a restricted subset of the widely used Python programming language. Copperhead follows the ideas of Selective, Embedded, Just-in-Time Specialization (SEJITS)[13]. Instead of creating an entirely new programming language for nested data parallelism, we repurpose existing constructs in Python, such as map and reduce. Embedding Copperhead in Python provides several important benefits. For those who are already familiar with Python, learning Copperhead is more similar to learning how to use a Python package than it is to learning a new language. There is no need to learn any new syntax, instead the programmer must learn only what subset of Python is supported by the Copperhead language and runtime. Copperhead programs are clearly delineated from surrounding Python code using standard Python syntax, so that the selected parts of the application that conform to Copperhead's restricted syntax and semantics are obvious. The Copperhead runtime, which invokes compilation in limited ways, is implemented as a standard Python extension. Copperhead programs are invoked through the Python interpreter, allowing them to interoperate with the wide variety of Python libraries already extant for numeric computation, file manipulation, data visualization, and analysis. The ability to interoperate with the broad array of Python libraries makes Copperhead a productive environment for prototyping, debugging, and implementing entire applications, not just their computationally intense kernels.

Of course, without being able to efficiently compile nested data parallel programs, Copperhead would not be of much use. Previous work on compilers for nested data parallel programming languages has focused on *flattening transforms* to target flat arrays of processing units. As we will discuss in Chapter 4, flattening transforms are a useful tool, but applying them indiscriminately sacrifices factors of two to five in performance on contemporary parallel microprocessors, because flattening transforms do not take advantage of the MIMD capabilities of on-chip multiprocessors.

Contemporary parallel microprocessors support a hierarchy of parallelism, with independent cores containing tightly coupled processing elements. Accordingly, the Copperhead compiler maps nested data parallel programs to a nested parallelism hierarchy, forgoing the use of flattening transforms, which we find to substantially improve performance. This is the central task of the Copperhead compiler, to which we will devote much attention in this work.

The current Copperhead compiler targets CUDA C++, running on manycore Graphics Processors from NVIDIA. We generate efficient, scalable parallel programs, performing within 45-100% of well optimized, hand-tuned CUDA code. Our initial implementation focus on CUDA does not limit us to a particular hardware platform, as the techniques we have developed for compiling data-parallel code are widely applicable to other platforms as well.

### 1.3 Contributions

This work includes the following main contributions:

- A direct mapping strategy for nested data parallel operations onto the parallel hierarchy provided by a target parallel platform. We detail how the flattening or vectorization transform common to many other data parallel compilers in inefficient on contemporary microprocessors, with a performance loss of  $3-5\times$  compared to direct mappings of nested data parallel operations onto a parallel hierarchy. The direct mapping strategy allows us to use the control flow structures avaliable in contemporary multiprocessors, which is crucial to attaining efficient performance comparable with hand-written efficiency code.

- Supporting this strategy, we propose a simple *phase analysis* technique that analyzes dataflow graphs to discover synchronization points, as well as *phase scheduling*, which fuses data parallel operations into phases that proceed without synchronization. Fusing data parallel operations is also crucial in order to achieve efficiency: for simple examples, we show that not fusing data parallel operations can result in a performance loss of 9×, due to increased memory bandwidth usage as well as extraneous synchronization, which limits the effective parallelism the platform can sustain. The decision of which operations to fuse can be a complicated optimization, and so we choose to use a simple maximalist heuristic that works well in many cases.

- Finally, we show how *runtime static compilation* enables efficiently embedding compiled languages into productivity environments. Naive embeddings of compiled languages can incur large runtime compilation costs, which can be on the order of tens of seconds, thus overwhelming efficiencies from a compiled binary that may only run for milliseconds. Runtime static compilation provides productivity programmers with a familiar workflow, while mitigating runtime overheads. Consequently, more sophisticated code generation techniques may be employed, such as autotuning and design space exploration. Additionally, the results of our compiler can be reused as a library in other programs, and applications built using runtime static compilation can be deployed on targets that disallow dynamic code generation, whether due to security constraints or the fact that many clients may not have compilers installed.

### 1.4 Outline

This thesis follows the following outline:

- Chapter 2 gives the background necessary to understand this thesis, including a discussion of related work.

- Chapter 3 describes the Copperhead language, along with its type system, the data parallel primitives it provides, and its relationship to Python.

- Chapter 4 details the compilation techniques by which Copperhead programs are efficiently compiled to efficiency language implementations. Special attention is paid to mapping nested data parallel operations directly onto a parallelism hierarchy.

- Chapter 5 discusses the runtime by which Copperhead programs are embedded in Python programs, describing the runtime static compilation approach we employ.

- Chapter 6 provides experimental results to show that Copperhead programs are both concise and efficient.

- Chapter 7 concludes with a discussion of the contributions of this work.

The next chapter explains the importance of data parallelism, the history of data parallel programming models and architectures, as well as trends in embedded domain specific languages, all of which influence this work.

# 2 BACKGROUND

In this chapter, we discuss some important background and related work.

### 2.1 Data Parallelism

As mentioned in the introduction, the shift to parallelism has been motivated by power efficiency considerations. On parallelized workloads, multiple slower cores running in parallel can deliver the performance of a fast monolithic core, but at much lower power consumption. However, in order to keep performance scaling at historical rates, the number of cores on a chip must continue to scale along with Moore's law. This, in turn, requires programmers to write parallel software that can take advantage of all these cores. The Berkeley View [2] argued that, once the genie of parallelism had been released from its bottle, programmers and hardware architects ought to embrace highly parallel architectures, which sacrifice single threaded performance in order to deliver higher aggregate performance on parallelizeable code, while improving overall power efficiency. This argument was motivated by the observation that an exponential increase in core count, enabled by Moore's law, will drive all architectures to highly parallel architectures in a relatively short timeframe. Accordingly, computationally intensive applications must be able to use very large amounts of parallelism. If a single application is to scale to utilize large amounts of parallelism, it stands to reason that it will be taking advantage of relatively small, fine-grained parallelism, or, in other words, data parallelism.