# Active Testing: Predicting and Confirming Concurrency Bugs for Concurrent and Distributed Memory Parallel Systems

Chang Seo Park

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2012-243 http://www.eecs.berkeley.edu/Pubs/TechRpts/2012/EECS-2012-243.html

December 13, 2012

Copyright © 2012, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Active Testing: Predicting and Confirming Concurrency Bugs for Concurrent and Distributed Memory Parallel Systems

by

Chang Seo Park

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Koushik Sen, Chair Professor Rastislav Bodík Professor David Wessel

Fall 2012

# Active Testing: Predicting and Confirming Concurrency Bugs for Concurrent and Distributed Memory Parallel Systems

Copyright 2012 by Chang Seo Park

#### Abstract

Active Testing: Predicting and Confirming Concurrency Bugs for Concurrent and Distributed Memory Parallel Systems

by

Chang Seo Park

Doctor of Philosophy in Computer Science University of California, Berkeley Associate Professor Koushik Sen, Chair

Parallel and concurrent software sometimes exhibit incorrect behavior because of unintended interference between different threads of execution. Common classes of concurrency bugs include data races, deadlocks, and atomicity violations. These bugs are often non-deterministic and hard to find without sophisticated tools. We present Active Testing, a methodology to effectively find concurrency bugs that scales to large distributed memory parallel systems.

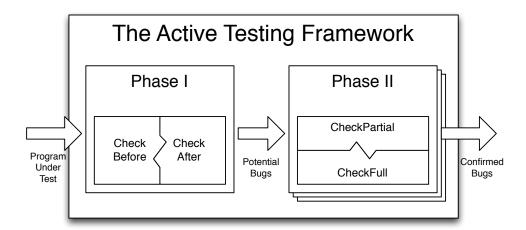

Active Testing combines the coverage and predictive power of program analysis with the familiarity of testing. It works in two phases: in the predictive analysis phase, a program is executed and monitored for potential concurrency bugs and in the testing phase, Active Testing re-executes the program while controlling the thread schedules in an attempt to reproduce the bug predicted in the first phase.

We have implemented Active Testing for multi-threaded Java programs in the CalFuzzer framework. We have also developed UPC-Thrille, an Active Testing framework for Unified Parallel C (UPC) programs written in the Single Program Multiple Data (SPMD) programming model combined with the Partitioned Global Address Space (PGAS) memory model. We explain in detail the design decisions and optimizations that were necessary to scale Active Testing to thousands of cores. We present extensions to UPC-Thrille that support hybrid memory models as well.

We evaluate the effectiveness of Active Testing by running our tools on several Java and UPC benchmarks, showing that it can predict and confirm real concurrency bugs with low overhead. We demonstrate the scalability of Active Testing by running benchmarks with UPC-Thrille on large clusters with thousands of cores.

To my father and mother,

# Contents

| $\mathbf{C}$ | ontents                                                                                                                             | ii           |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Li           | ist of Figures                                                                                                                      | iv           |

| Li           | ist of Tables                                                                                                                       | $\mathbf{v}$ |

| Li           | ist of Algorithms                                                                                                                   | vi           |

| Li           | ist of Programs                                                                                                                     | vii          |

| 1            | Introduction  1.1 Existing techniques to find concurrency bugs                                                                      |              |

|              | 1.3 Outline                                                                                                                         | . 4          |

| 2            | Common Concurrency Bugs  2.1 Data race through an example                                                                           | . 9          |

| 3            | Active Testing 3.1 Active Testing through an example 3.2 Concurrent system model 3.3 Phase I: Prediction 3.4 Phase II: Confirmation | . 17<br>. 20 |

| 4            | Instantiations of Active Testing 4.1 Data race detection for UPC                                                                    | . 30         |

| 5            | Implementation for Multi-threaded Programs 5.1 CalFuzzer                                                                            | <b>40</b>    |

|    | 5.2                                                     | Computing object abstractions                             | 41 |

|----|---------------------------------------------------------|-----------------------------------------------------------|----|

|    | 5.3                                                     | Yielding to avoid thrashing in reproducing deadlocks      | 45 |

| 6  | Eva                                                     | luation of Active Testing for Multi-threaded Programs     | 46 |

|    | 6.1                                                     | Summary of results                                        | 46 |

|    | 6.2                                                     | Deadlocks found                                           | 47 |

|    | 6.3                                                     | Atomicity violations found                                | 49 |

|    | 6.4                                                     | Evaluation of object abstractions and yielding            | 53 |

| 7  | Implementation for Distributed Memory Parallel Programs |                                                           |    |

|    | 7.1                                                     | Communication Avoiding Dynamic Analysis                   | 57 |

|    | 7.2                                                     | UPC-Thrille                                               | 61 |

|    | 7.3                                                     | Extensions to hybrid memory models                        | 68 |

| 8  | Eva                                                     | luation of Active Testing for Distributed Memory Programs | 74 |

|    | 8.1                                                     | Evaluation of UPC-Thrille for data race detection         | 74 |

|    | 8.2                                                     | Evaluation of techniques for hybrid memory models         | 80 |

| 9  | Rela                                                    | ated Work                                                 | 87 |

|    | 9.1                                                     | Concurrency bug analyses for multi-threaded programs      | 87 |

|    | 9.2                                                     | Concurrency bug analyses for other programming models     | 89 |

| 10 | Con                                                     | clusion                                                   | 91 |

|    | 10.1                                                    | Summary                                                   | 91 |

|    | 10.2                                                    | Discussion                                                | 92 |

| Bi | bliog                                                   | raphy                                                     | 94 |

# List of Figures

| 2.1 | Execution trace of Program 2.1                                                  | 7  |

|-----|---------------------------------------------------------------------------------|----|

| 2.2 | Erroneous execution trace of Program 2.1 when B and C are aliased               | 8  |

| 2.3 | Execution scenario and lock graph for Program 2.2                               | 10 |

| 2.4 | Execution scenario for Program 2.4                                              | 12 |

| 3.1 | Memory access events and potential data race pairs of execution in Figure 2.2 . | 16 |

| 3.2 | Steps to reproduce data race in Program 2.1                                     | 16 |

| 3.3 | Overview of the Active Testing framework                                        | 20 |

| 4.1 | The regions of other threads concurrent with a shared access                    | 28 |

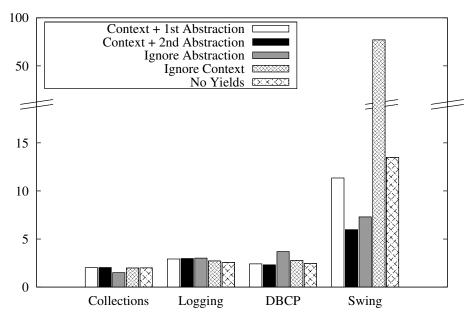

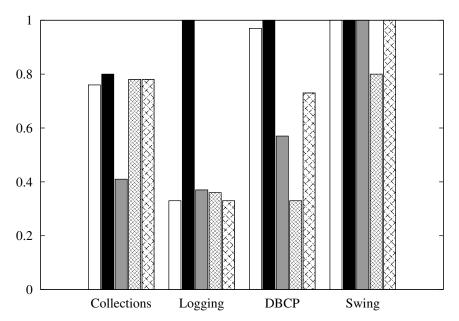

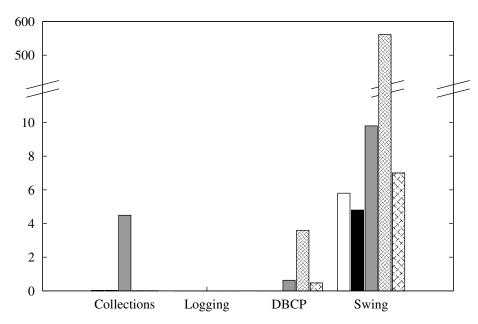

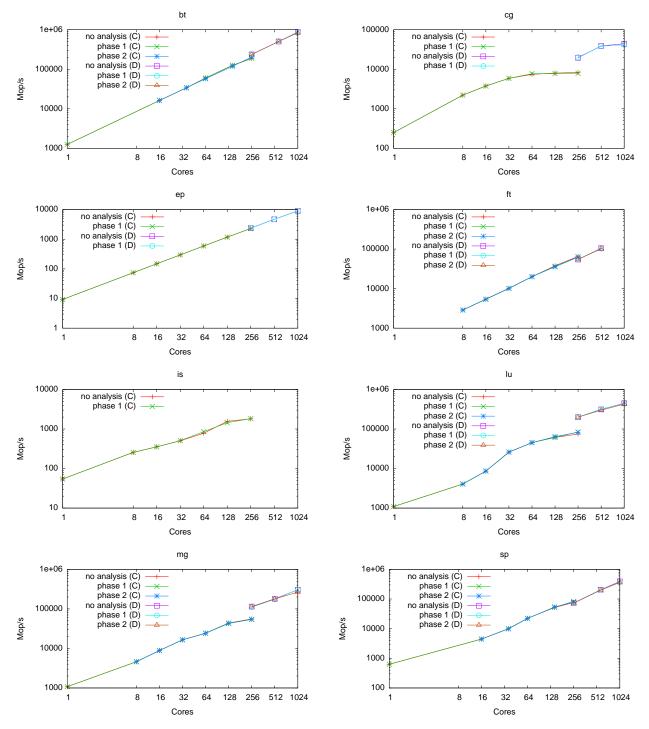

| 6.1 | Performance and effectiveness of DeadlockFuzzer variations                      | 55 |

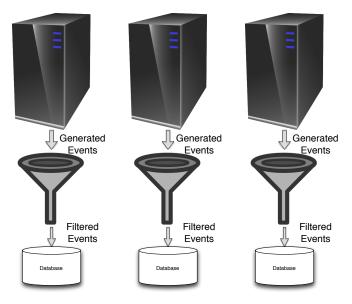

| 7.1 | The three operation modes of Communication Avoiding Dynamic Analysis            | 58 |

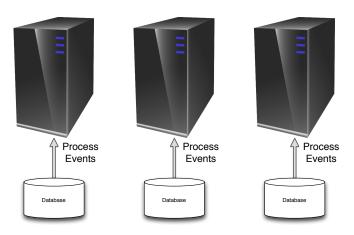

| 7.2 | Data structures used to efficiently represent memory accesses in UPC-Thrille    | 62 |

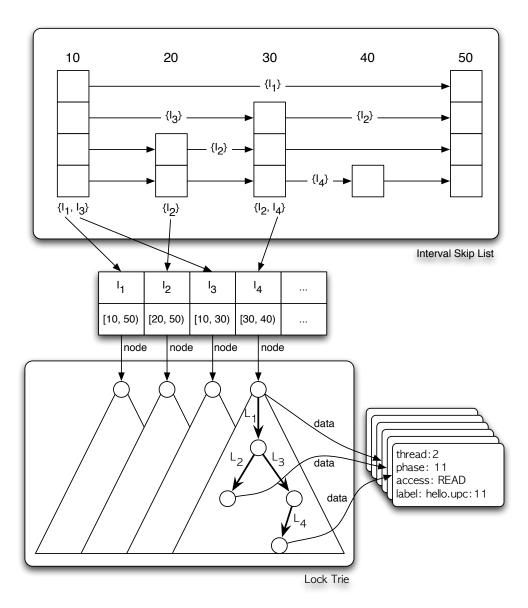

| 8.1 | Scalability of Active Testing up to 1024 cores                                  | 75 |

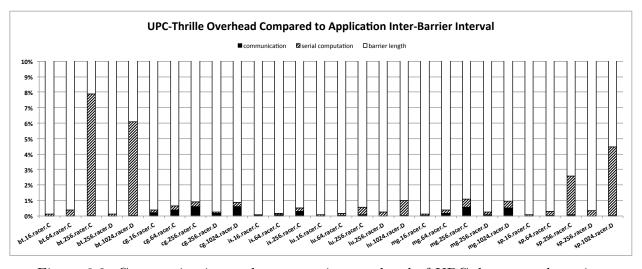

| 8.2 | Communication and computation overhead of UPC data race detection               | 76 |

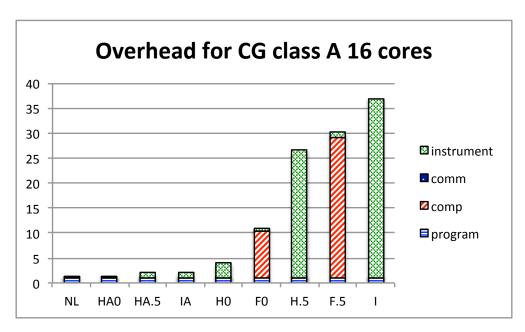

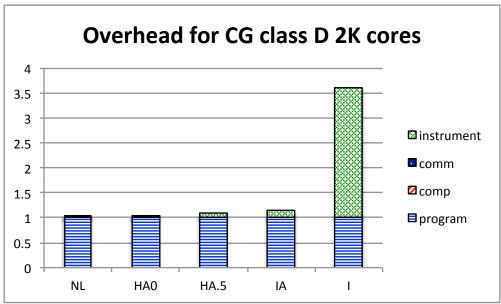

| 8.3 | Breakdown of data race detection overhead for hybrid memory models              | 83 |

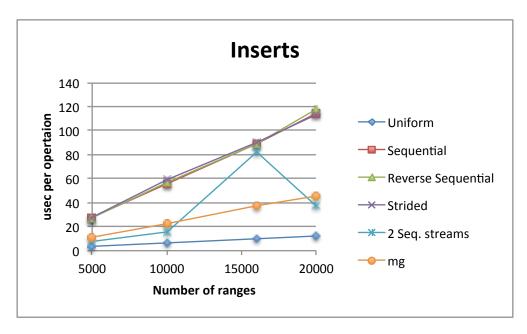

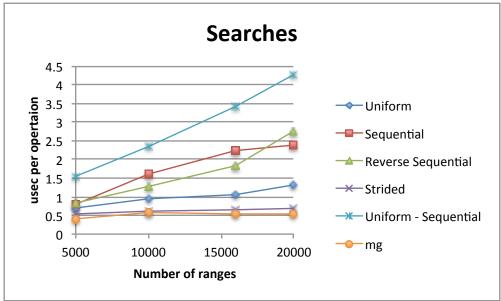

| 8.4 | Average time for the insert and search operations in Interval Skiplist          | 84 |

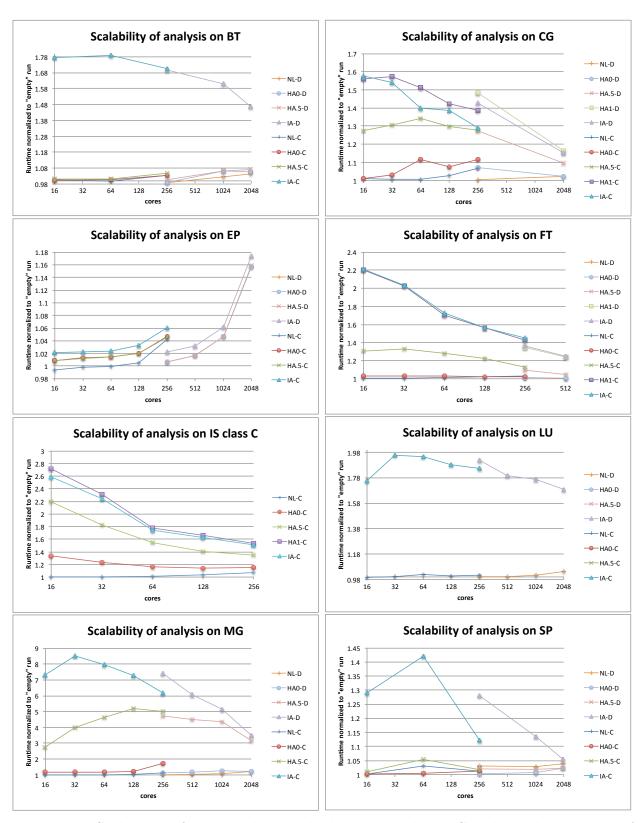

| 8.5 | Scalability of the different sampling methods of UPC-Thrille                    | 86 |

# List of Tables

| 6.1 | Results for each checker implemented in Calfuzzer         | 47 |

|-----|-----------------------------------------------------------|----|

| 8.1 | Results for race-directed Active Testing on a workstation | 76 |

| 8.2 | Statistics for UPC-Thrille with hierarchical sampling     | 79 |

| 8.3 | Key for labels of hierarchical sampling strategies        | 80 |

# List of Algorithms

| 3.1 | RandomScheduler $(c_0)$                                                                                                                                | 19 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Phase1Scheduler $(c_0)$                                                                                                                                | 20 |

| 3.3 | CheckBeforeLockset $(e)$                                                                                                                               | 21 |

| 3.4 | $CHECKAFTERLockSet(e)^{'}\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$                                                                             | 21 |

| 3.5 | Phase2Scheduler $(c_0, Abs)$                                                                                                                           |    |

| 3.6 | CheckPartialLockset $(e, Abs)$                                                                                                                         | 23 |

| 3.7 | $CHECkFullLockset(e, Paused, Abs) \qquad \dots $ | 24 |

| 4.1 | CheckBeforeUPCRace $(e)$                                                                                                                               | 29 |

| 4.2 | $CHECKAFTERUPCRACE(e)  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                                       |    |

| 4.3 | CheckBeforeDeadlock $(e)$                                                                                                                              |    |

| 4.4 | $\operatorname{IGOODLOCK}(D)$                                                                                                                          |    |

| 4.5 | CheckPartialDeadlock $(e, Cycle)$                                                                                                                      |    |

| 4.6 | CheckFullDeadlock $(e, Paused, Cycle)$                                                                                                                 | 35 |

| 4.7 | CheckPartialAtomViol $(e, Abs)$                                                                                                                        | 38 |

| 4.8 | CheckFullAtomViol $(e, Paused, Abs)$                                                                                                                   | 38 |

| 7.1 | FINDRACE(isl, e)                                                                                                                                       | 64 |

| 7.2 | $AddAccess(isl,e) \dots \dots$                   | 64 |

| 7.3 | THRILLERACERSCHEDULER()                                                                                                                                |    |

| 7.4 |                                                                                                                                                        |    |

# List of Programs

| 2.1 | Example of a data race in a UPC program                           | 7  |

|-----|-------------------------------------------------------------------|----|

| 2.2 | Example of a deadlock in Java                                     | 9  |

| 2.3 | Deadlock in Jigsaw                                                | 10 |

| 2.4 | Example of an atomicity violation                                 |    |

| 4.1 | Parallel knapsack implementation with data race                   | 26 |

| 5.1 | Example code that creates objects inside a loop                   | 43 |

| 5.2 | An example program that may thrash often during reproduction      | 45 |

| 6.1 | Atomicity violation in Java Collections                           | 50 |

| 6.2 | Initialization code causing spurious atomicity violation warnings | 51 |

| 6.3 |                                                                   | 52 |

|     | A benign atomicity violation                                      |    |

#### Acknowledgments

First, I would like to thank my Quals and dissertation committee—Professors Ras Bodik, Koushik Sen, David Wessel, and Kathy Yelick—for their insightful comments and feedback on my dissertation work. Special thanks goes to my advisor, Koushik Sen, for guiding me through my graduate school years for a successful completion. Without his motivation and energy, the deep intellectual discussions throughout the years, and invaluable advice for my research, I would not have made it this far.

I am grateful to my collaborators and co-authors—David Gay, Paul Hargrove, Costin Iancu, Pallavi Joshi, and Mayur Naik. Dr. Iancu, my mentor during my stay at Lawrence Berkeley National Labs, provided directions for research and technical insight for UPC-Thrille to reach the current level of maturity.

I would also like to thank Dimitra Giannakopoulou and Corina Pasareanu, my mentors at NASA Ames, for an enjoyable and stimulating internship; Jacob Burnim, Joel Galenson, Nick Jalbert, Gunho Lee, Yunsup Lee, Rhishikesh Limaye, Leo Meyerovich, Brad Miller, Daekyeong Moon, Christos Stergiou, my fellow graduate students for their feedback on my research, open-ended discussions, and collaboration on class projects; and last but not least, my family and friends for their emotional support during my long student years.

Parts of this dissertation are from previous papers [74, 49, 76] under copyright by ACM. This reuse follows the ACM Copyright Policy §2.5 Rights Retained by Authors and Original Copyright Holders. This research was supported in part by Microsoft (Award #024263) and Intel (Award #024894) funding and by matching funding by U.C. Discovery (Award #DIG07-10227). Additional support comes from Par Lab affiliates Nokia, NVIDIA, Oracle, and Samsung.

## Chapter 1

### Introduction

Since the semiconductor industry hit the power wall [7], processor speeds are no longer doubling every two years, but instead the number of processing elements, also called *cores*, on a single chip is increasing. To make use of the multiple cores and maintain performance gains with increasingly parallel hardware, it is necessary to run programs in *parallel*, i.e. making simultaneous computations on each core. A program with many threads can be readily executed in parallel and utilize the increasing number of cores.

For high performance computing (HPC), parallelism in not new. Supercomputers with thousands of cores appeared in the 1990s, hence the need for parallel programs existed in the past. Nowadays, the ubiquity of parallelism is found from the lower end of computing on dual- and quad-core processors on smartphones to supercomputers with more than a million total cores. Thus, the necessity of writing parallel programs has become ubiquitous as well.

Writing parallel programs is harder than writing their sequential counterparts. For parallel programs, resources such as memory are shared and there may be unintended interference among the threads when accessing shared resources. Due to such interference, a parallel program can have different results in different executions depending on how the threads are scheduled. This is called *non-determinism*. Non-determinism makes it harder for the programmer to ensure the correctness of a concurrent program.

Bugs due to non-determinism are called non-deterministic bugs or *concurrency bugs*. Some common classes of concurrency bugs are data races, deadlocks, and atomicity violations. Undetected during testing, these bugs can manifest while running in a production environment. In this thesis, we develop practical tools and techniques for finding concurrency bugs in parallel programs.

#### 1.1 Existing techniques to find concurrency bugs

There are many ways to help programmers write correct parallel programs. Model checking systematically explores all thread schedules for concurrency bugs. Programming languages for concurrency can have extended type systems and annotations that prevent writing erro-

neous code. Static analysis looks at the source code of a program and checks for bugs using various techniques such as data-flow analysis. Dynamic analysis examines an execution of a program to check for bugs in the execution or predict bugs that may happen in other executions. Testing runs the program with a given suite of inputs, usually with corresponding expected outputs to check against. These techniques mitigate the problem of writing incorrect concurrent programs with the following goals:

- Soundness: A technique is *sound* if it reports all bugs in the program, i.e. it does not have any false negatives.

- Completeness (Precision): A technique is *complete* or *precise* if it only reports real bugs, i.e. it does not have any false positives.

- Efficiency: A technique is *efficient* if it does not impose high overhead or have a prohibitively long analysis time.

- Scalability: A technique is *scalable* if it works for programs that have large code bases and/or run on large-scale systems.

- Automation: A technique is *automatic* if it requires little or no user intervention.

Model checking [26] verifies that a program follows its specification. By checking at each state exhaustively, model checking will either verify that the program is correct or report all violations of the specification, i.e. it is sound for bugs exhibiting behavior outside the specification. However, model checking fails to scale for large multi-threaded programs due to the exponential increase in the number of thread schedules with execution length (the state explosion problem).

Type and annotation based techniques [12, 34] help to avoid concurrency bugs at compile time by rejecting programs that do not type-check. They are sound, but they impose the burden of annotation on programmers. These annotations are often complex and/or tedious to write. Furthermore, these techniques are incomplete because some correct programs may be rejected if they cannot be well-typed in the system, requiring the programmer to rewrite the program or use workarounds.

Static analysis finds bugs in a program by reasoning about the code. Static program analyses often conservatively over-approximate bugs in the program such that bugs are not missed (sound), but they usually report many false positives (incomplete). Static analysis can be more precise using flow- and context-sensitive analysis, but this increases the computation and memory required for analysis and may not scale to large programs.

Dynamic analysis checks for bugs at run-time, by examining properties of a program during execution. Dynamic analyses are often precise, since bugs that they find are from real executions. However, dynamic analysis can add significant overhead to the program under analysis. Furthermore, dynamic analyses are unsound in nature, missing some bugs (false negatives), because it can only reason about code paths that are actually executed

during analysis. Predictive dynamic analysis tries to reduce false negatives by extrapolating from an execution to predict bugs that may happen in other executions with different thread interleavings to increase coverage. These predictive techniques give both false negatives and false positives, requiring manual inspection to see if a concurrency bug is real or not. Nevertheless, they are effective in finding concurrency bugs because they can predict bugs that could potentially happen during a real execution.

Testing techniques, such as random testing or stress testing, are often widely used to check correctness of parallel programs. In random testing, threads are scheduled randomly at runtime; in stress testing, a program is executed with thousands of threads and other heavy workloads to increase the probability of hitting buggy schedules. Testing techniques are complete, efficient, and automatable. However, random testing fails to find concurrency bugs with high probability as they appear for very specific thread interleavings. Stress testing done in a given environment often fails to come up with interleavings that could happen in other environments, such as under different system loads. Stress testing does not try to explicitly control the thread schedules, but rather depends on the underlying operating system or virtual machine for thread scheduling and often ends up executing the same interleaving repeatedly.

#### 1.2 Contributions

The main contribution of our work is that we make predictive dynamic analysis more precise and scalable while being efficient and automatic. We have developed a methodology called *Active Testing* which combines predictive dynamic analysis with testing. First, we take the predictive power of dynamic program analysis to find certain patterns during execution that may correspond to bugs. Then, like testing, we re-execute the program multiple times and observe failures and anomalous behavior. The main difference with traditional testing is that we actively control the thread schedules based on the information gathered from program analysis to direct testing towards the predicted bugs.

We have implemented a general framework for Active Testing which allows different dynamic analyses to be plugged in to find specific concurrency bugs. Existing dynamic analyses can be used to predict bugs; we have developed a few novel dynamic analyses of our own, such as a data race detector for distributed memory parallel programs because existing data race detection techniques do not scale well. A predictive dynamic analysis may generate a list of bugs with many false positives. Thus, we have also developed several *schedulers* for specific classes of concurrency bugs, which control the thread schedule to reproduce bugs. A scheduler tries to automatically reproduce the candidate bugs and report back to the programmer only the real bugs that it was able to reproduce. This removes the burden of the programmer to sift through all the reports and manually inspect if they are real bugs or not.

We have implemented Active Testing for Java, which uses threads and shared memory, and for UPC, a distributed memory parallel programming language. The implementation

of the Active Testing framework for Java is called CalFuzzer. CalFuzzer includes dynamic analyses to predict and confirm data races, atomicity violations, and deadlocks. In this thesis, we only present the algorithms in CalFuzzer for prediction and confirmation of atomicity violations and deadlocks. The Active Testing framework for UPC, is called UPC-Thrille. We present the first dynamic data race detector able to handle distributed memory parallel programs and demonstrate scalability to over a thousand cores.

To make Active Testing scale to large distributed memory parallel systems, we developed several novel techniques to form the Communication Avoiding Dynamic Analysis framework. Dynamic analysis for multi-threaded programs, which usually require a central monitoring thread to collect and analyze the execution of threads, does not work well at scale when directly ported to distributed memory parallel systems. A central analysis thread incurs a huge communication overhead; our initial experiments showed that such an implementation of a central analysis thread fails to scale beyond a few nodes. We avoid a central analysis thread by distributing the analysis. We reduce communication overhead by coalescing analysis traffic to synchronization boundaries and using filtering and sampling techniques to avoid redundant information.

#### 1.3 Outline

The rest of this thesis is organized as follows. Chapter 2 starts by introducing examples of common concurrency bugs in programs. We present definitions and examples of a data race, a deadlock, and an atomicity violation. We show how the bugs may affect the execution of a program and lead to errors.

As pointed out in the previous section, various techniques for uncovering concurrency bugs have limitations such as large overheads or too many false positives. Our technique aims to overcome these shortcomings for an efficient, scalable, and precise push-button tool for finding concurrency bugs. Chapter 3 lays down the background theories and formal definitions for Active Testing, our general dynamic analysis framework to predict and confirm real concurrency bugs. We explain the two phases of Active Testing, the prediction phase and confirmation phase, which is common to the bug detection algorithms for specific concurrency bugs such as data races, deadlocks, and atomicity violations. In Chapter 4, we describe instantiations of Active Testing for these classes of bugs on top of this general two-phase framework. For data races, we use a barrier-aware lockset based algorithm to predict data races in SPMD programs. We use an augmented Goodlock algorithm to predict deadlocks in multi-threaded programs. For atomicity, we target a particular locking pattern to predict and confirm real atomicity violations.

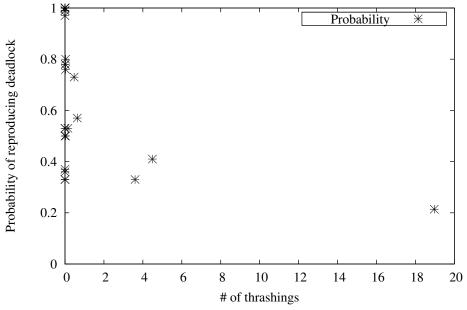

In Chapter 5, we describe in detail our Active Testing framework for Java, named Cal-Fuzzer. We also cover additional implementation details to increase the probability of reproducing concurrency bugs in phase II. We present two precise object abstraction techniques to pass contextual information from phase I to phase II to avoid *thrashing*, unnecessary pauses in execution. We also describe an optimization that uses *yields* to improve the reproduction of deadlocks. Chapter 6 summarizes the evaluation of our tool on multi-threaded benchmarks. We give detailed descriptions of the bugs that our tool found and the limitations of our tool. We also present evaluation of the object abstraction techniques and yielding optimization, showing how they affect the reproduction of deadlocks.

To make Active Testing scale to large distributed memory systems, we structured the analyses for better load distribution among the nodes and less communication over the network. Chapter 7 presents the Communication Avoiding Dynamic Analysis framework and our Active Testing implementation for UPC, named UPC-Thrille. We focus on the implementation details of a general framework for distributed memory parallel programs and a data race detector for UPC. We also extend UPC-Thrille to handle hybrid memory models that deal with multiple abstractions of the same memory space. We classify the three different overheads associated with finding data races on distributed memory systems—instrumentation, computation, and communication. We present a hierarchical sampling technique that significantly reduces the instrumentation and computation overheads. Chapter 8 shows the results for the evaluation of our tools on distributed memory parallel benchmarks, with a description of the bugs that we found. We present results that show Active Testing can efficiently and scalably find concurrency bugs for distributed memory systems. We also compare our hierarchical sampling technique with others to emphasize its effectiveness.

In Chapter 9, we discuss related work. Chapter 10 concludes the thesis with a brief summary and discusses future research directions.

## Chapter 2

## Common Concurrency Bugs

In this chapter, we go through a brief overview of the common concurrency bugs in programs through examples. A data race happens when two threads try to access the same memory location with an unspecified order. A deadlock occurs when a system cannot make progress because all threads are waiting for a resource held by some other thread. Atomicity violations are bugs that happen when a programmer's assumption about the indivisibility of an operation is broken.

#### 2.1 Data race through an example

One of the most common concurrency errors due to lack of synchronization is a data race. A parallel program has a data race if the program can reach a state during execution where two threads are about to access the same memory location and at least one of the accesses is a write. Depending on the order of access, i.e. read after write or write after read (or in case both of the accesses are writes, whichever one occurred last), the program may exhibit different behavior which in some cases may lead to erroneous executions. This non-deterministic behavior may result in bugs that happen only under very specific schedules, and thus hard to detect.

Data races are also harmful in that they may break sequential consistency [54] depending on the memory model of the underlying system. Sequential consistency is the notion that every execution of a program on multiple processors should be equivalent to some interleaved execution on a single processor, i.e. the operations have a single and total sequential order. If sequential consistency is violated, it may lead to unexpected and undefined behaviors of the program. [10]

Consider Program 2.1, a matrix-vector multiply routine written in Unified Parallel C (UPC). UPC [16] is an extension of the C language with a shared global address space and data parallel constructs. The shared keyword specifies pointers and arrays to shared memory (e.g. the input variables A, B, C are declared to be shared). Non-shared pointers and arrays, such as sum in line 4 are local and distinct to each thread. The upc\_forall

```

void matvec (shared [N] double A[N][N], shared double B[N],

2

shared double C[N])

{

3

4

double sum [N];

\mathbf{upc\_forall}(\mathbf{int} \ \mathbf{i} = 0; \ \mathbf{i} < \mathbf{N}; \ \mathbf{i++}; \&C[\mathbf{i}])

5

6

7

sum[i] = 0;

8

for (int j = 0; j < N; j++)

9

sum[i] += A[i][j] * B[j];

10

\mathbf{upc\_forall}(\mathbf{int} \ \mathbf{i} = 0; \ \mathbf{i} < N; \ \mathbf{i}++; \&C[\mathbf{i}])

11

C[i] = sum[i];

12

\} // assert(C == A * B)

13

```

Program 2.1: Example of a data race in a UPC program

```

Initially,

A = \begin{pmatrix} 1 & 2 \\ 3 & 4 \end{pmatrix} \text{ and } B = \begin{pmatrix} 1 \\ 1 \end{pmatrix}

\frac{\text{Thread 1}}{1 \cdot \text{sum}[0] = 0;} \qquad \text{a. sum}[1] = 0;

2 \cdot \text{sum}[0] += A[0][0] * B[0]; \qquad \text{b. sum}[1] += A[1][0] * B[0];

3 \cdot \text{sum}[0] += A[0][1] * B[1]; \qquad \text{c. sum}[1] += A[1][1] * B[1];

4 \cdot C[0] = \text{sum}[0]; \qquad \text{d. } C[1] = \text{sum}[1];

\frac{\text{Output}}{C = \begin{pmatrix} 3 \\ 7 \end{pmatrix}}

```

Figure 2.1: Execution trace of Program 2.1

statement is a parallel-for loop that runs the loop body in different threads. The fourth argument denotes where to run the loop body. For example, the upc\_forall loops in lines 5 and 11, run the loop body in the thread that owns the memory corresponding to the *i*th element of C. We give a more detailed description of UPC in Chapter 4.1.

If we run the example on two threads with N=2, the execution trace of all memory loads and stores with arithmetic operations would look like Figure 2.1. The two threads

```

\frac{\text{Initially,}}{A = \begin{pmatrix} 1 & 2 \\ 3 & 4 \end{pmatrix}} \quad \text{and} \quad B = \begin{pmatrix} 1 \\ 1 \end{pmatrix}

\frac{\text{Thread 1}}{1. \text{ sum}[0] = 0;}

2. \text{ sum}[0] += A[0][0] * B[0];

3. \text{ sum}[0] += A[0][1] * B[1];

4. \text{ B}[0] = \text{sum}[0];

b. \text{ sum}[1] += A[1][0] * B[0];

c. \text{ sum}[1] += A[1][1] * B[1];

d. \text{ B}[1] = \text{sum}[1];

\frac{\text{Output}}{C = \begin{pmatrix} 3 \\ 13 \end{pmatrix}}

```

Figure 2.2: Erroneous execution trace of Program 2.1 when B and C are aliased

execute in parallel, running their portion of the loop bodies. Since the writes made by the threads are to addresses distinct from each other, the result of the program is correct no matter how the shared memory accesses interleave with each other.

However, if the routine is called with B and C aliased (i.e., for an in-place multiplication), there are two data races:  $\langle$  3, d  $\rangle$  (because 3 is a read from Thread 1, d is a write from Thread 2, and &B[1] == &C[1]) and  $\langle$  4, b  $\rangle$  (similarly). One common misconception of the upc\_forall loop is that all the loop bodies must terminate to continue (i.e., there is an implicit barrier at the end of the upc\_forall statement), which is not true for UPC. Nothing prevents Thread 1 from executing 4 before Thread 2 finishes b or Thread 2 from executing d before Thread 1 finishes 3. Figure 2.2 is an execution trace where Thread 1 executes 4 then Thread 2 executes b. After Thread 1 makes the update to B (because it is aliased to C) at 4, Thread 2 reads the new value when computing the inner product at b, resulting in the wrong value.

This example illustrates several challenges for finding data races: 1) the number of possible interleavings can be very large; and 2) the number of memory access to analyze increases with the problem size. Even for such a small program with only two threads, there are 70 possible interleavings.<sup>1</sup> Five interleavings have 4 executing before b (e.g., Figure 2.2) and 10

<sup>&</sup>lt;sup>1</sup>There are 5 places where a through d can go: before 1, between 1 and 2, between 2 and 3, between 3 and 4, and after 4. Picking from the 5 locations 4 times with replacement corresponds to  $\binom{5+4-1}{4} = \binom{8}{4} = 70$ .

```

Initially,

Object 11 = new Object();

Object 12 = new Object();

Thread 2

Thread 1

synchronized(l1) {

synchronized(12) {

1

synchronized(12) {

synchronized(l1) {

2

3

8

9

4

5

10

```

Program 2.2: Example of a deadlock in Java

interleavings have d executing before 3. Thus, even though the program may be incorrect, 55 out of 70 interleavings (78.6%) execute the program computing the correct result. This illustrates why such bugs can be easily missed with stress testing or random testing, and why it requires a large amount of work to check all the interleavings exhaustively.

Instead of checking all interleavings, dynamic data race detectors like ours in Chapter 4.1 analyze the memory accesses to predict data races. However, if we run the program on many threads with a large data set, there may be an overwhelming number of memory accesses to analyze. We have developed novel sampling and filtering techniques to reduce the number of accesses to consider while retaining the ability to predict most or all data races in the program.

#### 2.2 Deadlock through an example

Data races and other concurrency errors can be prevented with synchronization. One common synchronization primitive is a lock (also called a mutex, for **mut**ual **ex**clusion). A lock is an object that can be held by only one thread at a time, which can be used for mutual exclusion of threads in critical regions of code.

However, locks must be used with care; certain locking patterns may run into a *deadlock*, where all threads are blocked waiting to acquire a lock which is already held by some other thread, thus no progress is made. Consider example Program 2.2. Here, a deadlock situation can arise in the scenario illustrated in Figure 2.3.

Jigsaw, shown in Program 2.3, is a webserver which has this locking pattern that could deadlock. The nested synchronization corresponds to the statements in lines 7 and 8 for the main httpd thread and lines 4 and 6 for a SocketClient thread. The SocketClientFactory object corresponds to lock 11 in Program 2.2 and the SocketClientState object in line 2 corresponds to lock 12. When the server shuts down, it calls cleanup code that shuts down the SocketClientFactory. The shutdown code holds a lock on the factory at line 7, and in turn attempts to acquire the lock on csList at line 8. On the other hand, when a

Thread 1

Thread 2

11

12

- 1. Thread 1 successfully acquires lock 11 (line 1).

- 2. Thread 2 successfully acquires lock 12 (line 6).

- 3. Thread 1 is waiting to acquire lock 12 (line 2).

- 4. Thread 2 is waiting to acquire lock 11 (line 7).

- 5. Both threads are blocked and cannot progress a deadlock has occurred.

Figure 2.3: Execution scenario and lock graph for Program 2.2

```

class SocketClientFactory {

2

SocketClientState csList;

boolean clientConnectionFinished (...) {

3

synchronized (csList) { decrIdleCount(); }

4

5

6

synchronized boolean decrIdleCount() {...}

7

synchronized void killClients (...) {

8

synchronized (csList) {...}

9

10

void shutdown() {

killClients (...);

11

}

12

}

13

14

Thread 1: httpd

Thread 2: SocketClient

15

SocketClientFactory pool;

SocketClientFactory factory;

16

pool.clientConnectionFinished (...);

factory.shutdown();

17

```

Program 2.3: Deadlock in Jigsaw

SocketClient is closing, it also calls into the factory to update a global count. In this situation, the locks are acquired in the opposite order: the lock on csList is acquired first at line 4, and then on the factory at line 6. Thus, when both events happen simultaneously, the webserver may deadlock and not shut down cleanly.

A deadlock can happen non-deterministically: in some cases, a programs runs to completion, and under some other thread schedule a deadlock occurs and can be detected by observing that a set of blocked threads are all waiting for a lock held by another thread in the set. In our running example (Program 2.2), a deadlock does not happen if the order of lock acquires is 1 2 6 7.

```

public class Consumer {

2

private LinkedList buffer;

public synchronized void consume() {

3

if (! buffer . isEmpty()) {

4

Object data = buffer.remove();

5

6

System.out.println(data.toString());

7

}

}

8

9

}

public class LinkedList ... {

10

public synchronized boolean isEmpty() { ... }

11

public synchronized Object remove() { ... }

12

13

}

14

```

Program 2.4: Example of an atomicity violation

Thus, we need tools that check if a program could deadlock or not. A static deadlock detector [66, 103] can predict deadlocks by inspecting the locking behavior in code. We can also detect deadlocks with runtime monitoring by creating lock graphs. A lock graph has locks as nodes and the lock ordering relation as edges. Whenever a thread t attempts to acquire  $lock_2$  when the last acquired lock still held is  $lock_1$ , an edge labeled t is added from node  $lock_1$  to  $lock_2$ . For example, the diagram on the right of Figure 2.3 is the lock graph for Program 2.2. If there is a cycle in the lock graph with distinct labels along the edges, there is a potential for a deadlock. In our example program, there is a cycle  $\langle 11, 12, 11 \rangle$  and corresponds to the deadlock in the scenario above.

Static and predictive dynamic deadlock detectors often report too many false positives, i.e. they are imprecise. Active Testing reports only the deadlocks that it reproduces, reducing the burden of the programmer to confirm whether each report is real or not. For example, out of the 283 deadlocks in Jigsaw predicted by a dynamic deadlock analysis, we report only 29 of those that Active Testing was able to reproduce.

One challenge for reproducing deadlocks from lock graphs is that it is hard to know at run-time which lock acquires lead to a deadlock, as locks can be acquired in many contexts. We present a dynamic deadlock prediction algorithm in Chapter 4.2 with precise object abstractions that provides contextual information to help reproduce deadlocks.

#### 2.3 Atomicity violation through an example

The absence of data races in a parallel program is not sufficient to ensure that it is free of non-deterministic bugs. *Atomicity* is a property of multi-threaded programs that enforces

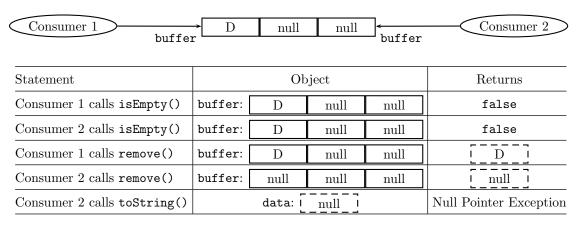

Figure 2.4: Execution scenario for Program 2.4 where Consumer 1 and Consumer 2 share the buffer and both call consume()

non-interference. A block of code in a multi-threaded program is atomic if for every possible interleaved execution of the program there exists an equivalent execution with the same overall behavior where the atomic block is executed serially. In other words, the execution of the atomic block behaves as if it is not interleaved with actions of other threads. Therefore, if a code block is atomic, the programmer can assume that the execution of the code block by a thread cannot be interfered by any other thread. This helps programmers reason about atomic code blocks sequentially.

Consider Program 2.4 as an example. A Consumer class has an associated buffer where objects are stored for processing. Before consuming a data object, the buffer is first checked to see if there are any elements to process (line 4). Only when the buffer is non-empty, an element is removed and printed. All methods of the LinkedList class are synchronized, thus even if multiple consumers share the same buffer, there is no data race involved.

However, there may still be a problem in this program for some interleavings. In the execution scenario in Figure 2.4, two Consumer objects share a common buffer and both are calling the consume() method when there is only one item in the buffer. If the statements are executed in the given order, both Consumer objects will check if the buffer is empty and get a negative answer. Thus, they both try to remove an object from the buffer, but only one of them will get a data object (Consumer 1 in this case) and the other gets a null pointer. When the null data object is dereferenced by Consumer 2, an exception occurs.

This scenario is an exemplar "time of check to time of use" (TOCTTOU) bug, which is caused by changes in the system between the check of a state and the use of that state [94]. What we intended was for the check and remove from the buffer to be one indivisible operation, i.e. an atomic operation. This atomicity property has been violated in this case.

In most modern multi-threaded programming languages, atomicity is indirectly achieved through the use of locks. However, the use of locks cannot always ensure a code block to be atomic. Program 2.4 is an example of this problem. Thus, many existing program analysis techniques use heuristics to infer atomic blocks from locks and predict atomicity

violations. This heuristic may lead to many false positives which increases the burden on the programmer to check each report manually. In Chapter 4.3, we present a dynamic atomicity violation analysis which reports only the real atomicity violations that actually happen in an execution, reducing this burden of confirming real atomicity violations.

## Chapter 3

## **Active Testing**

Numerous program analysis techniques [40, 72, 31] have been developed to *predict* concurrency bugs in multi-threaded programs by detecting violations of commonly used synchronization idioms. For instance, accesses to a memory location without holding a common lock are used to predict data races on the location, and cycles in the program's lock order graph are used to predict deadlocks. However, these techniques often report many false warnings because violations of commonly used synchronization idioms do not necessarily indicate concurrency bugs. Manually inspecting these warnings is often tedious and error-prone.

Active Testing [87, 74, 49] is a technique for finding real bugs in concurrent programs. Active Testing uses a randomized thread scheduler to verify if warnings reported by a predictive program analysis are real bugs. The technique works as follows. In the first phase, Active Testing uses an existing predictive off-the-shelf static or dynamic analysis, such as Lockset [84, 72], Atomizer [31], or Goodlock [40], to compute potential concurrency bugs. Each such potential bug is identified by an abstract state. For example, in the case of a data race, the abstract state consists of a pair of program statements that could potentially race with each other in some execution. In the second phase, for each potential concurrency bug, Active Testing runs the given concurrent program under random schedules. Further, Active Testing biases the random scheduling by pausing the execution of any thread when the thread partially satisfies the abstract state describing the potential concurrency bug. After pausing a thread, Active Testing also checks if a set of paused threads could exhibit a real concurrency bug. For example, in the case of a data race, Active Testing checks if two paused threads are about to access the same memory location and at least one of them is a write. Thus, Active Testing attempts to force the program to take a schedule in which the concurrency bug actually occurs.

In the following sections, we show informally how Active Testing works with a simple example. We also define the formal model of concurrent systems that we test. The model describes the minimal interface of concurrent systems used in our Active Testing algorithms. We describe in more detail the two phases of Active Testing and their generic schedulers.

#### 3.1 Active Testing through an example

Consider the execution trace from Figure 2.2 (page 8) again. This execution trace of Program 2.1 (page 7) with B and C aliased is of great interest to us for two reasons: 1) it clearly shows that there is a race, and 2) it also shows that the result computed is incorrect. There is a race between events 4 and b, because the write from Thread 1 and the read from Thread 2 to the same address B[0] are temporally next to each other. This is ideally the kind of trace we would like to obtain from testing, but a trace that a random scheduler can rarely produce.

Active Testing tries to automatically create such execution traces that exhibit a data race. First, we run an imprecise dynamic analysis on an execution of the program to find potential data races that are present in the program. The analysis is a variant of a lockset based algorithm [84, 18, 72, 100]. The analysis checks if two threads could potentially access a memory location without holding a common lock. Specifically, the analysis observes all memory accesses that happen during an execution of the program and records the locks held during each such access. If there exists two accesses to the same memory location by different threads, a common lock is not held during the accesses, and at least one of the accesses is a write, then the analysis reports a potential data race. The analysis reports the pairs of statements where the threads access the memory location, respectively. Formally, the set of potential data races pairs reported by the analysis is defined as follows:

**Definition 3.1** (Set of Potential Data Race Pairs:  $\mathcal{D}_{P,E}$ ). Given an execution E of a program P, let us denote a shared memory access event by a thread in the execution by e = (m, t, l, a, s), where

- 1. m is the memory address range that is being accessed,

- 2. t is the thread accessing the memory address range.

- 3. l is the set of locks held by t at the time of access,

- 4.  $a \in \{READ, WRITE\}$  is the access type, and

- 5. s is the label of the program statement that generates the memory access event.

Let  $A_{P,E}$  be the set of all shared memory access events in the execution E. Then the set of potential data race pairs reported by the analysis is

$$\mathcal{D}_{P,E} = \{(s_1, s_2) \mid \exists e_1, e_2 \in \mathcal{A}_{P,E} \text{ such that } e_1 = (m_1, t_1, l_1, a_1, s_1) \land e_2 = (m_2, t_2, l_2, a_2, s_2) \land m_1 \cap m_2 \neq \emptyset \land t_1 \neq t_2 \land l_1 \cap l_2 = \emptyset \land (a_1 = WRITE \lor a_2 = WRITE)\} .$$

In our example execution trace of Figure 2.2,  $\mathcal{A}_{P,E}$  and  $\mathcal{D}_{P,E}$  are shown in Figure 3.1. Note that a race pair in  $\mathcal{D}_{P,E}$  reported by the analysis can be a false warning because the analysis does not check if the two accesses are ordered by a synchronization operation. The analysis simply checks if the program adheres to the idiom that every memory access is consistently protected by a lock. As such, the analysis can report data races that did not actually happen in the execution E, but could happen in a different execution E' of the

```

\begin{split} \mathcal{A}_{P,E} = & \left\{ \; \left( \; [\text{A}, \, \text{A} + 8), \, \text{T1}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{A} + 8, \, \text{A} + 16), \, \text{T1}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{B}, \, \text{B} + 8), \, \text{T1}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{B} + 8, \, \text{B} + 16), \, \text{T1}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{A} + 16, \, \text{A} + 24), \, \text{T2}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{A} + 24, \, \text{A} + 32), \, \text{T2}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{B}, \, \text{B} + 8), \, \text{T2}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{B} + 8, \, \text{B} + 16), \, \text{T2}, \, \text{READ}, \, \left\{ \right\}, \, 9 \; \right), \\ & \left( \; [\text{B} + 8, \, \text{B} + 16), \, \text{T2}, \, \text{WRITE}, \, \left\{ \right\}, \, 12 \; \right) \; \right\} \\ \\ \mathcal{D}_{P,E} = & \left\{ \; \left( 9, \, 12 \right) \; \right\} \end{split}

```

Figure 3.1: Memory access events and potential data race pairs of execution in Figure 2.2

|                         | Statement of T1        | Statement of T2          | Paused | Scheduler action    |

|-------------------------|------------------------|--------------------------|--------|---------------------|

| a                       | 7:sum[0]=0             |                          | -      | pick T1 and execute |

| b                       |                        | 7:sum[1]=0               | -      | pick T2 and execute |

| $\overline{\mathrm{c}}$ |                        | (9:sum[1]+=A[1][0]*B[0]) | -      | pick T2 and pause   |

| $\overline{\mathbf{d}}$ | 9:sum[0]+=A[0][0]*B[0] |                          | T2     | pick T1 and execute |

| e                       | 9:sum[0]+=A[0][1]*B[1] |                          | T2     | pick T1 and execute |

| f                       | (12:B[0]=sum[0])       | (9:sum[1]+=A[1][0]*B[0]) | T2     | data race created   |

| g                       | 12:B[0]=sum[0]         |                          | -      | pick T1 and execute |

| h                       |                        | 9:sum[1]+=A[1][0]*B[0]   | -      | pick T2 and execute |

| i                       |                        | 9:sum[1]+=A[1][1]*B[1]   | -      | pick T2 and execute |

| j                       |                        | 12:B[1]=sum[1]           | -      | pick T2 and execute |

#### Statements 9 and 12 may race

Figure 3.2: Steps to reproduce data race in Program 2.1

program under a different thread schedule. This predictive power of the analysis is crucial for increasing the coverage of our Active Testing technique.

To confirm that this prediction is true, we re-execute the program with a random scheduler, but with knowledge that statements 9 and 12 may race. We use a scheduler that serializes the execution, i.e. it picks one thread at a time to execute. Figure 3.2 shows the steps of the scheduler. At step a, the scheduler randomly picks T1 and executes the statement normally. At step b, the scheduler randomly picks T2 and executes the statement. At step c, the scheduler picks T2, but since it is about to execute statement 9 which may race with statement 12, it pauses the thread so that some other thread can reach statement 12. At step d, the scheduler can only pick T1, because T2 is paused. It is also about to execute a statement that may race with statement 12, but pausing T1 would stall the system by

pausing all threads. Thus we execute the statement at T1, similarly at step e. At step f, T1 is about to execute statement 12. This is a statement that may race with statement 9, where T2 is paused. We check if the two threads are in race, and they are since T1 is about to write to B[0] and T2 is about to read from B[0]. Thus, we have created a real data race. From this point, we unpause all threads and continue to observe the remaining execution for any anomalies. After going through steps g–j, we have created an execution trace identical to Figure 2.2, showing the data race and the incorrect result.

The example illustrates the practical challenges of Active Testing. In phase I, 1) managing overhead of data collection at every memory access and synchronization operation; 2) managing overhead of exchanging the data collected between threads; and 3) efficiently reasoning about the information gathered to predict concurrency bugs. We address these challenges by presenting a hierarchical sampling technique for data race detection in Chapter 7.3; structuring scalable dynamic analyses to avoid communication in Chapter 7.1; and efficient algorithms for predicting concurrency bugs in Chapter 4.

In phase II, we need to strategically pick when to pause which thread. If done naively, we may incur large overheads by pausing threads unnecessarily at irrelevant points and reduce the probability of reproducing concurrency bugs. We developed techniques for precise object abstractions, discussed in Chapter 5.2, to help reproduce concurrency bugs by providing contextual information for when to pause threads.

#### 3.2 Concurrent system model

We use a simple and general model of a concurrent system to describe our Active Testing methodology. This model can be used for shared memory systems, distributed memory parallel systems, and others as well. We consider a concurrent system to be composed of a finite number of threads. Each thread executes a sequence of labeled statements. A thread communicates with other threads using shared memory. At any point of program execution, a concurrent system is in some state, which internally contains the contents of shared memory and bookkeeping information for threads. Starting at the initial state  $c_0$ , a concurrent system evolves from one state to another when a thread executes a statement. We leave the detailed operational semantics of statements unspecified; for analysis and testing purposes, we do require a few operations to query and control the system. We assume that at any state of the concurrent system, we can make the following queries and operations.

- ENABLED $(c) \to T$ : Returns the set of threads T that are enabled in state c. A thread is disabled if it is waiting to acquire a lock already held by some other thread or waiting at a barrier.

- ALIVE $(c) \to T$ : Returns the set of threads T that are alive (i.e., has not terminated) in state c. The state c is in a *stall state* when some threads are alive but none are enabled (i.e., ENABLED $(c) = \emptyset \land ALIVE(c) \neq \emptyset$ ).

- EVENT $(c,t) \to e$ : Returns the event e, which would be generated if thread t executes its next statement in state c.

- EXECUTE $(c,t) \to c'$ : Returns the new state c' after thread t executes its next statement in state c.

We consider the following events that are generated as statements are executed in the concurrent system. An event is generated as a state transitions into the next state.

**Definition 3.2** (Events). As a concurrent system evolves its state through execution of statements, the following externally observable transition events are generated.

- MEM(t, s, m, a): Thread t at statement labeled s (same for all other events below) accessed memory range m, consisting of the start and end addresses, where the access type a is either READ or WRITE.

- LOCK(t, s, l): Thread t acquired lock l.

- UNLOCK(t, s, l): Thread t released lock l.

- BARRIER\_NOTIFY(t, s): Thread t notified other threads that the barrier is ready to cross.

- BARRIER\_WAIT(t, s): Thread t finished waiting at a barrier for notifications from other threads.

- ATOMIC\_ENTER(t, s): Thread t entered an atomic section.

- ATOMIC\_EXIT(t, s): Thread t left an atomic section.

- $\tau$ : any other internal events that we do not handle.

Given the above model of concurrent programs, we define a *happens-before* [53] relation to formally describe our bug detection algorithms. The *happens-before* relation requires the notion of *independence* of transitions.

**Definition 3.3** (Independent Transitions). If two transitions in a concurrent system do not interact with each other, then we call them independent.

For example, a transition denoting the acquire of a lock  $l_1$  by a thread  $t_1$  is independent of a transition denoting the acquire of a lock  $l_2$  by another thread  $t_2$ , if  $l_1$  and  $l_2$  are different locks.

**Definition 3.4** (Dependent Transitions). Two transitions are said to be dependent, if they are not independent.

#### **Algorithm 3.1:** RANDOMSCHEDULER $(c_0)$

```

Input: the initial state c_0

1 c := c_0;

2 while Enabled(c) \neq \emptyset do

3 | t := a random thread in Enabled(c);

4 | c := Execute(c, t);

5 if Alive(c) \neq \emptyset then

6 | print "ERROR: system stall";

```

Transitions from the same thread are always dependent on each other. Similarly, the acquire or release of a lock by one thread is dependent on the acquire or release of the same lock by another thread. Two accesses (i.e. read or write) of a memory location are dependent if at least one of the accesses is a write.

A sequence of transitions represents the execution of a concurrent system. Specifically,  $\tau = t_1 t_2 \dots t_n$  is a transition sequence if there exists states  $c_0, c_1, \dots, c_n$  such that  $c_0$  is the initial state and

$$c_0 \xrightarrow{t_1} c_1 \xrightarrow{t_2} \dots \xrightarrow{t_n} c_n$$

.

**Definition 3.5** (Happens-before:  $\preceq$ ). The happens-before relation  $\preceq$  for a transition sequence  $\tau = t_1 t_2 \dots t_n$  is defined as the smallest relation such that

- 1. if  $t_i$  and  $t_j$  are dependent and  $1 \le i \le j \le n$ , then  $t_i \le t_j$ , and

- 2.  $\prec$  is transitively closed.

Thus  $\prec$  is a partial order relation.

We use a *scheduler* to get an execution trace of a concurrent system. Algorithm 3.1 is an example of a simple random scheduler which randomly selects an enabled thread and executes a single statement of that thread. The main loop in line 2 continues execution of a statement from a random thread that is enabled. When no thread is enabled, the scheduler makes the final check that all threads have terminated in line 5. If this is not the case, then the system is in a state that cannot make progress while some thread has not yet terminated. We call this error state a *system stall*.

Figure 3.3 shows an overview of the Active Testing framework. In the following sections, we describe generic schedulers for Phase I (Section 3.3) and Phase II (Section 3.4) of Active Testing. These schedulers require functions specific to predicting and confirming a class of concurrency bug. We use lockset-based data race detection as an example in the next sections. Chapter 4 describes these functions for predicting and confirming data races, deadlocks, and atomicity violations.

Figure 3.3: The Active Testing Framework takes a concurrent program under test and returns confirmed bugs. Internally, it finds potential bugs in the first phase and confirms and reports real bugs in the second phase.

```

Algorithm 3.2: Phase1Scheduler(c_0)

Input: the initial state c_0

Output: set of abstract states

1 \ c := c_0;

a \ Abs := \emptyset;

з while ENABLED(c) \neq \emptyset do

t := a \text{ random thread in ENABLED}(c);

e := \text{EVENT}(c, t);

Abs := Abs \cup CheckBeforeX(e);

6

c := \text{EXECUTE}(c, t);

7

Abs := Abs \cup CHECKAFTERX(e);

9 if ALIVE(c) \neq \emptyset then

print "ERROR: system stall";

11 return Abs:

```

#### 3.3 Phase I: Prediction

The Phase I scheduler shown in Algorithm 3.2 is a general way to dynamically observe and gather information about the execution of a program. Each dynamic analysis may have a variety of data structures and algorithms, but we generalize this problem as inserting two functions before and after each statement execution. The two function calls are at lines 6 and 8 in Phase1Scheduler. Each of these functions return abstract states which describe certain states of the program that potentially correspond to bugs. We collect these states

#### **Algorithm 3.3:** CheckBeforeLockset(e)

```

Initially: Acc = \emptyset, the set of all memory accesses in current execution,

\forall t \in T. L(t) = \emptyset, the set of locks held by thread t

Input: Event e the concurrent system is about to generate

1 switch e do

case MEM(t, s, m, a)

2

Acc := Acc \cup (m, t, L(t), a, s);

3

return \{(s,s') \mid \exists (m',t',l',a',s') \in Acc. \quad m \cap m' \neq \emptyset \land t \neq t' \}

4

\wedge L(t) \cap l' = \emptyset \wedge (a = WRITE \vee a' = WRITE)\};

case LOCK(t, s, l)

5

L(t) := L(t) \cup l;

7 return ∅:

```

#### **Algorithm 3.4:** CheckAfterLockset(e)

```

Initially: L is shared with CheckBeforeLockset

Input: Event e the concurrent system has just generated

1 switch e do

case \mathit{UNLOCK}(t, s, l)

L(t) := L(t) \setminus l;

4 return \emptyset:

```

until the end when we pass off the set of abstract states to the next phase, which confirms whether these states can occur in a real execution of the program and correspond to real concurrency bugs.

For example, let us consider the lockset-based predictive data race analysis from The analysis implemented in our framework works as follows. Phase1Scheduler (Algorithm 3.2) with the functions CheckBeforeLockset (Algorithm 3.3) and CHECKAFTERLOCKSET (Algorithm 3.4). This is an online analysis that checks for potential data races at every memory access and returns the statement pairs that may race as abstract states describing the bug. Before each memory access (lines 2–4 of CHECKBEFORELOCKSET), we add the access event into the set of all memory accesses so far. We check if there is a previous event in the set that accessed an overlapping memory address  $(m \cap m' \neq \emptyset)$ , from a different thread  $(t \neq t')$ , without a common lock held  $(L(t) \cap l' = \emptyset)$ , and either the previous or current access is a write ( $a = WRITE \lor a' = WRITE$ ). If such an access is found, we return the abstract state that describes the data race: the pair of statements that make the accesses. To keep track of the locks held during a memory access, we update the set of locks held by each thread before acquiring a lock (lines 5–6 of CHECK-BeforeLockset) and after releasing a lock (lines 2–3 of CheckAfterLockset). We need not consider any events other than memory accesses and locking related events.

We show in Chapter 4 other algorithms predicting concurrency bugs written in such manner: CheckBeforeUPCRACE and CheckAfterUPCRACE for finding data races and CheckBeforeDeadlock for finding deadlocks.

#### 3.4 Phase II: Confirmation

Once we obtain a set of abstract states from Phase I, we check one by one whether these abstract states can occur in an execution and correspond to a real concurrency bug. An abstract state tries to capture the essence of a concurrency bug: two or more threads that are in certain concrete states simultaneously. For example, in our lockset-based data race detection example, a pair of statements is an abstract state that represents racy accesses. Another example is a lock graph containing a cycle to represent a potential deadlock.

One reason why concurrency bugs non-deterministically occur only in certain executions is because of the simultaneity condition: only particular thread schedules allow these threads to be in their respective states at the same time. By controlling the scheduler, we make a best effort to recreate these buggy states by delaying certain threads to meet the simultaneity condition. However, recreating the abstract state is not always enough. We need to make sure that the abstract state created corresponds to a real concurrency bug. Once we have two threads about to execute the statements in the pair predicted as a race, we need to confirm that they are indeed in race by checking if the two accesses are to overlapping memory addresses.

The Phase II scheduler shown in Algorithm 3.5 is a general way to recreate a state corresponding to concurrency bugs. As in the Phase I scheduler, it requires functions particular to a class of concurrency bug that check states of an execution. CheckPartialX returns true when a thread is in a state which could potentially be part of a concurrency bug state. For example, CheckPartialLockset (Algorithm 3.6) returns true when the next event of a thread is a memory access predicted to be in a race. CheckFullX examines a set of threads to see if they are in a real concurrency bug state. In CheckFullLockset (Algorithm 3.7), we make sure that we are in a state where a real data race is about to happen by checking that the memory addresses overlap and the accesses each correspond to one of the statements in the pair.

Phase2Scheduler guides the execution of a concurrent system to reach a potential buggy state (Abs) reported from Phase I. We randomly pick and execute enabled threads that are not Paused by the analysis (line 7). Certain threads are paused to increase the chance of threads being in the abstract state simultaneously. Line 5 is a safeguard that prevents the scheduler from artificially stalling the system by pausing all enabled threads.

For the thread that was selected, we check whether the next event of the thread partially satisfies the abstract state (line 9). If this is true, we check if the current thread along with the paused threads correspond to a real concurrency bug (line 10). We report an error if we are in such a state. Since we have confirmed the bug, we unpause all threads and

#### **Algorithm 3.5:** Phase2Scheduler $(c_0, Abs)$

```

Input: the initial state c_0 and the abstract state Abs to check for

c := c_0;

2 Paused := \emptyset;

prob := 1.0;

4 while Enabled(c) \neq \emptyset do

if ENABLED(c) = Paused then

Remove a random thread from Paused;

// Prevents artificial stall

6

t := a \text{ random thread in ENABLED}(c) \setminus Paused;

7

e := \text{EVENT}(c, t);

if CheckPartialX(e, Abs) then

9

if CHECKFULLX(e, Paused, Abs) then

10

Report error;

11

Paused := \emptyset;

12

prob := 0;

13

else if RANDOM() < prob then

14

Paused := Paused \cup T;

15

prob := prob \times BACKOFF;

16

continue;

17

c := \text{EXECUTE}(c, t);

18

19 if ALIVE(c) \neq \emptyset then

print "ERROR: system stall";

20

```

#### **Algorithm 3.6:** CHECKPARTIALLOCKSET(e, Abs)

```

Input: Event e the concurrent system is about the generate and the abstract state Abs to confirm

1 (s_1, s_2) := Abs;

2 switch e do

3 | case MEM(t, s, m, a)

4 | return s = s_1 \lor s = s_2;

5 | otherwise

6 | return false;

```

prevent pausing threads hereafter such that we can observe the remaining execution for any anomalies.

If the event partially satisfies the abstract state but the full state does not correspond to a concurrency bug, it may be that all the threads required for the bug have not reached their certain states yet. Thus, we add the selected thread to the *Paused* set so that other threads may catch up. Since the constant pausing and unpausing of threads may reduce

#### Algorithm 3.7: CHECKFULLLOCKSET(e, Paused, Abs)

```

Input: Event e, the current set of Paused threads, and the abstract state Abs to confirm

1 (s_1, s_2) := Abs;

2 switch e do

3 | case MEM(t, s, m, a)

4 | return \exists t' \in Paused. Event(t') = MEM(t', s', m', a') \land (m \cap m' \neq \emptyset) \land ((s = s_1 \land s' = s_2) \lor (s = s_2 \land s' = s_1));

5 | otherwise

6 | return false;

```

execution speed drastically, we employ an *exponential backoff* scheme to randomly decide whether to delay the thread or not (line 14). Starting with a pause probability of 1, we gradually decrease this probability exponentially after each attempt to recreate the buggy state by delaying a thread.

In the next chapter, we describe two more bug reproduction algorithms using functions that fit Phase2Scheduler. CheckPartialDeadlock and CheckFullDeadlock reproduce deadlocks; CheckPartialAtomViol and CheckFullAtomViol detect and reproduce atomicity violations in a single phase.

## Chapter 4

## Instantiations of Active Testing

In this chapter, we present algorithms used in the two phase of Active Testing to detect and confirm concurrency bugs. First, we present a data race detection and confirmation algorithm for programs written in Unified Parallel C (UPC), an extension of C for writing parallel programs. Then, in section 4.2, we describe an algorithm to detect and confirm deadlocks in Java programs. Finally, in section 4.3, we introduce an algorithm to detect and confirm atomicity violations for Java programs in a single phase. This algorithm is different from the previous two in that it does not require the prediction phase to find abstract potential buggy states. It discovers and confirms these abstract states while running only the confirmation phase of Active Testing.

#### 4.1 Data race detection for UPC

#### Unified Parallel C

Unified Parallel C (UPC) is a parallel extension to ISO C 99 for high performance computing. UPC uses the Single Program Multiple Data (SPMD) parallelism model and provides a Partitioned Global Address Space: the memory is partitioned in a thread local heap and a global heap. All threads can access memory residing in the global heap, while access to the local heap is allowed only for the owner thread. The global heap is logically partitioned between threads and each thread is said to have local affinity with its sub-partition. The language extends the C type system with the shared qualifier to denote pointer accesses to the global address space. Global memory can be accessed either using shared pointer dereferences (load and store) or using bulk communication primitives (memget() and memput()). The language provides synchronization primitives, namely locks, barriers, and split-phase barriers.

Locks and semaphores are common synchronization constructs in shared memory programming models (e.g. pthreads), but SPMD programs also utilize barriers (and their split-phase versions) for bulk synchronization. When a thread reaches a barrier statement, it

```

int build_table(int nitems, int cap, shared int *T,

2

shared int *w, shared int *v) {

3

int wj, vj;

4

wj = w[0];

5

vj = v[0];

6

\mathbf{upc\_forall}(\mathbf{int} \ \mathbf{i} = 0; \ \mathbf{i} < \mathbf{wj}; \ \mathbf{i++}; \&T[\mathbf{i}])

7

T[i] = 0;

8

upc_{-}forall(int i = wj; i \le cap; i++; \&T[i])

9

T[i] = vi;

10

upc_barrier;

11

12

int main(int argc, char** argv) {

13

14

upc_forall(i = 0; i < nitems; i++; i)

15

weight [i] = 1 + (lrand48()\%max_weight);

16

value [i] = 1 + (lrand48()\%max_value);

17

18

best_value = build_table(nitems, capacity, total, weight, value);

19

20

21 }

```

Program 4.1: Parallel knapsack implementation with data race.

cannot proceed onto the next statement until all others threads have also reached the barrier. This effectively splits a program execution into multiple *phases* and all threads run in the same phase at a given time.

Utilizing the time while waiting for other threads in barriers, we can increase parallelism by doing some useful local work. UPC has *split-phase barriers*, in which a thread first *notifies* the other threads that they can continue through the barrier and then after doing some local work, if available, it *waits* for notification from the other threads. The events  $BARRIER_NOTIFY(\cdot)$  and  $BARRIER_WAIT(\cdot)$  in Definition 3.2 are generated respectively, when a thread notifies other threads and when a thread finished waiting for other threads at a barrier.

#### Phase I: Race Prediction Phase

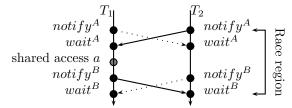

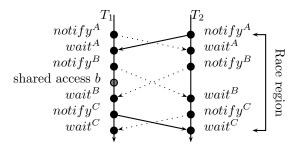

Data races happen when in an execution two threads are about to access the same memory location, at least one access is a write, and no ordering is imposed between these concurrent accesses. Figure 4.1 is a partial listing for a UPC program that computes the "0-1 knapsack

problem" in parallel using dynamic programming. Although not apparent at first look, there are two data races in this program that can lead to incorrect results. The first data race is between lines 4 and 16, and the second between lines 5 and 17. Since a upc\_forall statement is not a collective operation (i.e., there is no implicit synchronization at the beginning or end of the loop), there is no ordering enforced between the write to weight [0] in line 16 and the read from it in line 4. If the read happens before the write, the table is incorrectly initialized and result in an incorrect computation. The second race is similar to the first. Ironically, the program has been assigned for years as homework for graduate parallel programming courses at UC Berkeley. The bug has been reported by students, which was detected by our tools and independently confirmed by others.

To predict this bug in the example program, we can use the lockset-based predictive dynamic analysis from Chapter 3. However, in lieu of lock based synchronization, scientific programs tend to use barrier synchronization. A barrier partitions the program execution into different phases and prevents a thread from advancing to the next phase before all other threads have completed the phase. Due to this kind of synchronization, our phase I analysis reports a large number of false warnings. In order to eliminate these false warnings, we propose a modification to our analysis, called *Barrier Aware May-Happen-in-Parallel Analysis*.

#### Barrier Aware May-Happen-in-Parallel Analysis

In order to hide communication latency in clusters, split phase barriers are provided in the UPC language. Non-blocking collectives serve a similar purpose in other languages. A split phase barrier in UPC is implemented by a pair of calls upc\_notify and upc\_wait. As long as there are no data conflicts, threads can execute arbitrary code in between this pair of calls, also called the *local computation phase* as opposed to the *global computation phase* which is everywhere outside the pair of calls. In principle, only local work should be done in the local computation phase for proper synchronization but this is not enforced.