# From Poisson to Silicon - Advancing Compact SPICE Models for IC Design

Sriramkumar Venugopalan

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-166 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-166.html

October 8, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### From Poisson to Silicon - Advancing Compact SPICE Models for IC Design

by

Sriramkumar Venugopalan

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu, Chair Professor Ali M. Niknejad Professor Paul K. Wright

Fall 2013

#### From Poisson to Silicon - Advancing Compact SPICE Models for IC Design

$\begin{array}{c} {\rm Copyright~2013} \\ {\rm by} \\ {\rm Sriramkumar~Venugopalan} \end{array}$

#### Abstract

From Poisson to Silicon - Advancing Compact SPICE Models for IC Design

by

Sriramkumar Venugopalan

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Hu, Chair

The semiconductor industry has relied on accurate device models for analyzing, predicting and innovating integrated circuit design. Multi-gate MOSFET device architectures like FinFETs are beginning to replace their planar MOSFET counterparts at the 22 nm technology node to enable continued technology scaling. Vertical cylindrical gate (CG) MOSFET are touted to replace planar MOSFETs as the memory device for DRAM and NAND Flash offering increased area density. New device architectures together with relentless scaling of MOSFETs for performance mean increased complexity and new device physics that need to be comprehended. This new understanding needs to be translated into device models for technology progress. Newer device models also require newer methodologies for model creation process and usage for circuit design.

In this thesis we develop a comprehensive compact SPICE model for a CG MOSFET. Relying on fundamental physics based electrostatics description (Poisson Equation) of the device analytic equations for terminal current and capacitance are derived forming the core model. Including all requisite real device effects we validate this model to both numerical simulations (TCAD) and hardware silicon data showing < 1\% RMS error when the model is tuned to the data. For channel diameters < 20 nm quantum mechanical confinement effects tend to dominate. The complex bias and geometry dependence of the inversion charge centroid is captured through a phenomenological model. This model helps accurate prediction of the reduction in gate capacitance of a CG MOSFET. This model was also extended to carrier confinement in thin channels such as the double gate FET or FinFET. The vertical CG MOSFET exhibits asymmetry w.r.t. source and drain. With the aid of TCAD we propose that non-uniform vertical channel doping and structural differences in the top and bottom (source/drain) junction regions as the major contributors to the asymmetric behavior. We then create a mathematical framework to capture these asymmetries in the compact model developed above. We validate this approach by showing excellent agreement to hardware silicon data from a high voltage vertical CG MOSFET technology. All these models have been incorporated in BSIM-CMG the first industry standard multi-gate MOSFET model. Despite including many complex physical effects the resultant model can be executed in the order of few 10's of  $\mu secs$  (per operating point) enabling rapid very large scale integrated circuit design.

A compact SPICE model maintains a balance of predictive nature and flexibility with many sub-components describing various physics and tunable parameters in order to capture data from various sources accurately. This could quickly become unmanageable during a model creation process. For this we propose a RF model extraction procedure that does not require any additional sub-circuit elements and takes advantage of advances in parameter optimization tools available today in an efficient manner. We demonstrate this procedure on high frequency data from multiple planar MOSFET technologies discussing various use cases. Using BSIM6, a bulk planar MOSFET compact model the resultant procedure was able to capture silicon data even beyond the cut-off frequency of the MOSFET and predict various RF circuit design figure of merits with great accuracy.

To my Parents, Sis, extended family, and some wonderful Mentors.

# Contents

| C  | Contents List of Figures |                                                                       |           |

|----|--------------------------|-----------------------------------------------------------------------|-----------|

| Li |                          |                                                                       |           |

| 1  | Intr                     | roduction                                                             | 1         |

|    | 1.1                      | Industry Relevance                                                    | 1         |

|    | 1.2                      | Advanced MOSFET Device Architectures                                  | 2         |

|    |                          | 1.2.1 Symmetric Multi-Gate FET - FinFETs                              | 3         |

|    |                          | 1.2.2 Symmetric Multi-Gate FET - Surround Gate / Gate-All-Around FETs | 4         |

|    |                          | 1.2.3 Asymmetric Multi-Gate FETs                                      | 5         |

|    | 1.3                      | Compact SPICE Models                                                  | 6         |

|    |                          | 1.3.1 BSIM-CMG                                                        | 8         |

|    |                          | 1.3.2 BSIM6                                                           | 9         |

|    |                          | 1.3.3 BSIM-IMG                                                        | 9         |

|    | 1.4                      | Compact Models Usage                                                  | 9         |

|    | 1.5                      | Scope and Organization of Dissertation                                | 10        |

| 2  | $\operatorname{Cor}$     | e Models for Multi-Gate MOSFETs in BSIM-CMG                           | <b>12</b> |

|    | 2.1                      | Symmetric Multi-Gate Core Models - A Review                           | 13        |

|    | 2.2                      | Comprehensive Core model for Cylindrical/Surround Gate FET            | 17        |

|    |                          | 2.2.1 Poly-Depletion Effect                                           | 17        |

|    |                          | 2.2.2 Surface Potential / Charge Equation                             | 19        |

|    |                          | 2.2.3 Drain Current Equation                                          | 22        |

|    |                          | 2.2.4 Charge and Capacitance Models                                   | 24        |

|    | 2.3                      | Model Verification and Quality Assurance                              | 30        |

|    | 2.4                      | Summary                                                               | 32        |

| 3  | 3-D                      | Device Effects Models for Multi-Gate FETs                             | 39        |

|    | 3.1                      | Quantum mechanical effects in Fins and Pillars                        | 40        |

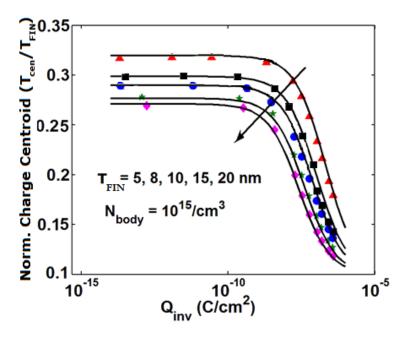

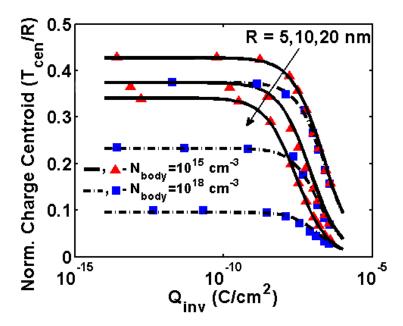

|    |                          | 3.1.1 Charge Centroid Model                                           | 41        |

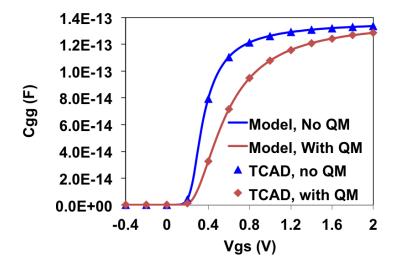

|    |                          | 3.1.2 Effective Gate Capacitance Model                                | 48        |

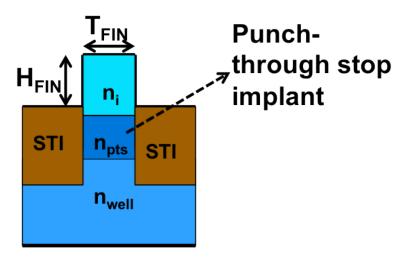

|    | 3.2                      | Double Junction capacitance modeling for Bulk FinFETs                 | 49        |

|    |               |                                                    | 51       |

|----|---------------|----------------------------------------------------|----------|

|    | 3.3           |                                                    | 52<br>55 |

|    | 0.0           | v                                                  |          |

| 4  | •             | 8                                                  | 56       |

|    | 4.1           |                                                    | 57       |

|    |               | 1 0                                                | 57       |

|    |               | · · · · · · · · · · · · · · · · · · ·              | 59       |

|    |               |                                                    | 61       |

|    | 4.2           |                                                    | 62       |

|    |               | v v                                                | 63       |

|    | 4.3           |                                                    | 66       |

|    | 4.4           |                                                    | 68       |

|    | 4.5           | Summary                                            | 69       |

| 5  | $\mathbf{RF}$ | CMOS Modeling - Art of Parameter Extraction        | 72       |

|    | 5.1           | RF relevant models in BSIM6                        | 73       |

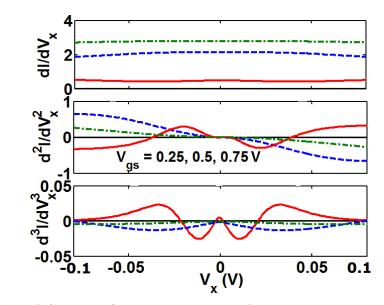

|    |               | 5.1.1 Drain Current and its derivatives            | 73       |

|    |               | 5.1.2 MOS Intrinsic and Parasitic Capacitance      | 75       |

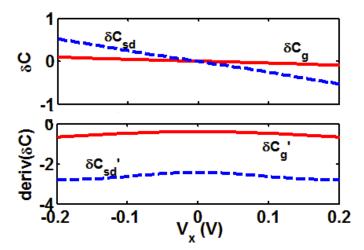

|    |               | 5.1.3 Junction Current and Capacitance             | 77       |

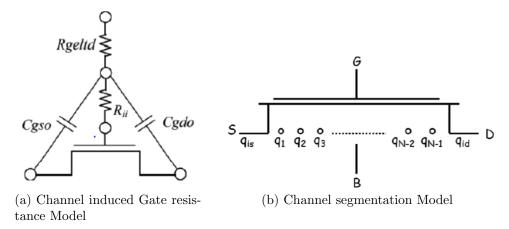

|    |               | 5.1.4 Gate Electrode Resistance                    | 78       |

|    |               |                                                    | 79       |

|    |               |                                                    | 80       |

|    | 5.2           | Parameter extraction flow - Theory                 | 82       |

|    |               | 5.2.1 Intrinsic and Extrinsic Capacitance          | 84       |

|    |               | 5.2.2 Drain Current and Higher order Derivatives   | 85       |

|    |               | 5.2.3 Junction Current and Capacitance             | 86       |

|    |               | 5.2.4 Substrate Effects                            | 87       |

|    |               | 5.2.5 Gate Resistance and Non Quasi Static effects | 88       |

|    |               | 5.2.6 Miscellaneous Parasitic Elements             | 89       |

|    | 5.3           | Validation                                         | 90       |

|    | 5.4           | Summary                                            | 92       |

| 6  | Con           | nclusions                                          | 98       |

|    | 6.1           |                                                    | 00       |

| Ri | hliog         | graphy 1                                           | 02       |

| וע | ν110E         | 5. up.i.y                                          | J 2      |

| A  | Fur           | ther Reading for Real Device Effects Models  1     | 10       |

| В  | MO            | 1                                                  | 14       |

|    | B.1           | Drain Current Derivation                           | 14       |

|    | B.2           | Terminal Charge Derivation                         | 16       |

| $\mathbf{C}$ | Rev | isiting Substrate Network Model for High Frequencies | 121 |

|--------------|-----|------------------------------------------------------|-----|

| $\mathbf{D}$ | Non | -Quasi Static Effect Models                          | 125 |

|              | D.1 | Relaxation Time Approximation Model                  | 126 |

|              | D.2 | Channel Induced Gate Resistance Model                | 127 |

|              | D.3 | Charge Segmentation Model                            | 128 |

# List of Figures

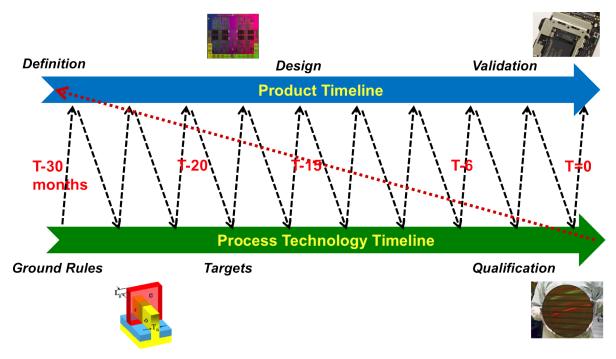

| 1.1 | Semiconductor technology-IC design interaction along the different phases of                                    |    |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

|     | product development. The dotted lines represent exchange of information in                                      |    |

|     | the form of Compact Models for SPICE                                                                            | 2  |

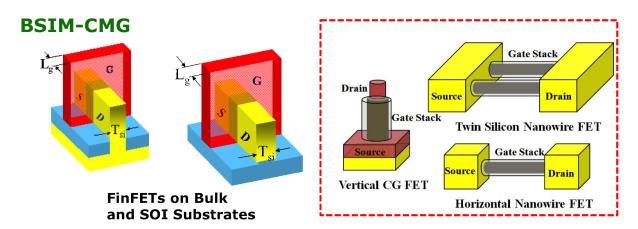

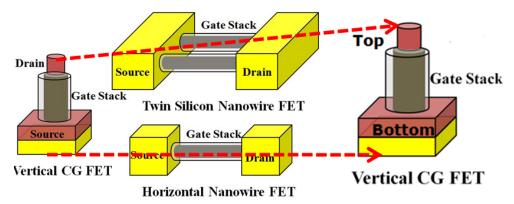

| 1.2 | Various Symmetric Multi-Gate Transistor architectures                                                           | 3  |

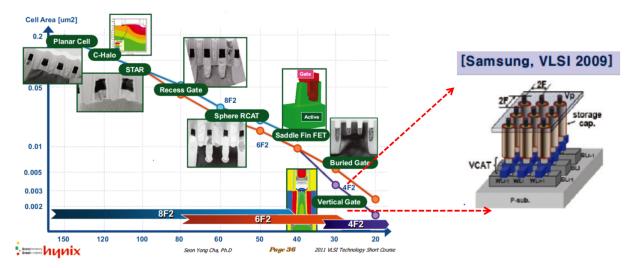

| 1.3 | DRAM transistor device technology progress over the years                                                       | 4  |

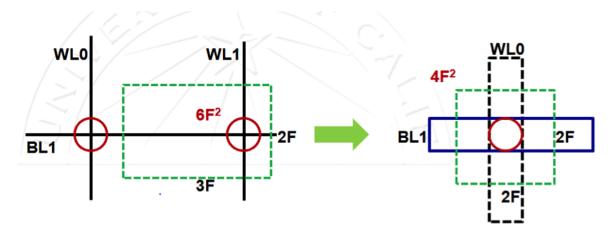

| 1.4 | Layout of an one-transistor one-capacitor DRAM technology demonstrating the                                     |    |

|     | move from a $6F^2$ to a more compact $4F^2$ per bit cell enhancing DRAM area density.                           | 5  |

| 1.5 | Various Asymmetric Multi-Gate Transistor architectures                                                          | Ę  |

| 1.6 | Timeline of the BSIM family of compact models. The models in gray (BSIM1-3                                      |    |

|     | and BSIM5) are not supported by the group any longer. The underlined model                                      |    |

|     | (BSIM-IMG) is under evaluation/standardization by CMC                                                           | 7  |

| 1.7 | The various components and structure of contemporary Compact SPICE transis-                                     |    |

|     | tor models                                                                                                      | 8  |

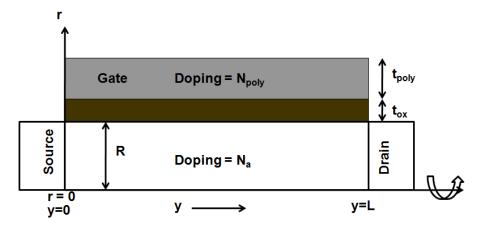

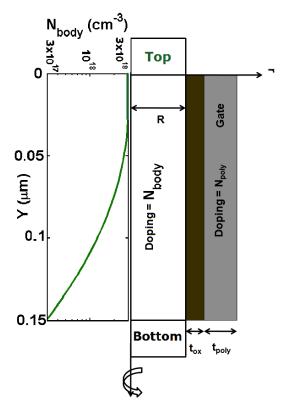

| 2.1 | Coordinate system convention and variables for the cylindrical gate FET                                         | 18 |

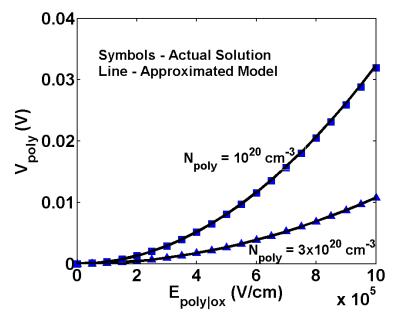

| 2.2 | Voltage drop in the polysilicon gate obtained from the iterative numerical solution                             |    |

|     | compared against approximate solution for a given electric field at the gate and                                |    |

|     | oxide interface                                                                                                 | 20 |

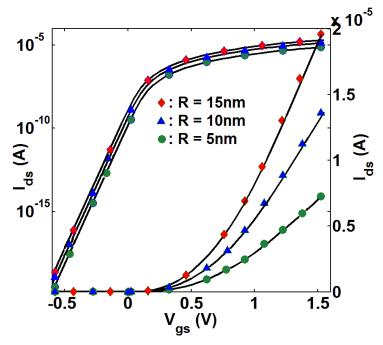

| 2.3 | Drain current for a long channel FET $(L = 10 \mu\text{m})$ with different channel radii                        |    |

|     | showing scalability of the model. (Symbols: TCAD, Lines: Model), $t_{ox} = 2 \text{ nm}$                        | 23 |

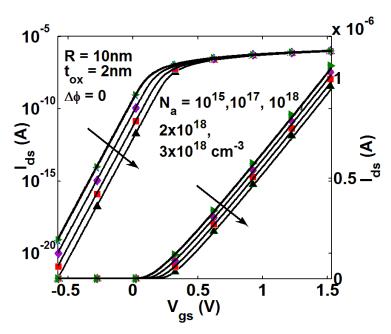

| 2.4 | Drain current characteristics for a lightly doped and a heavilly doped long channel                             |    |

|     | transistor. $(L = 10 \mu\text{m})$ with a 2 nm gate oxide. This model captures doping in                        |    |

|     | the channel as well. (Symbols: TCAD, Lines: Model)                                                              | 24 |

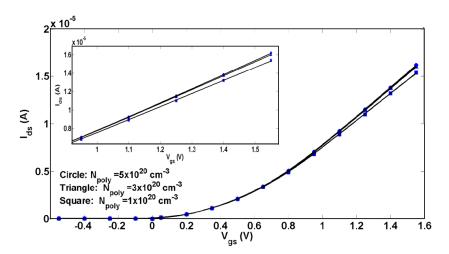

| 2.5 | $I_{ds}-V_{gs}$ characteristics for three different values of gate polysilicon doping. (Sym-                    |    |

|     | bols: TCAD, Lines: Model) with $L = 10 \mu\text{m}, R = 10 \text{nm}$ and $t_{ox} = 2 \text{nm}$                | 25 |

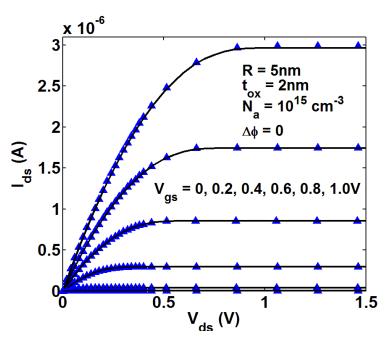

| 2.6 | $I_{ds} - V_{ds}$ characteristics for a long channel device with $L = 10 \mu \mathrm{m}, R = 5 \mathrm{nm}$ and |    |

|     | 2 nm oxide thickness. (Symbols : TCAD, Lines : Model)                                                           | 26 |

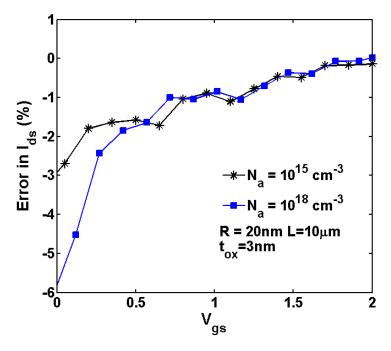

| 2.7 | Percentage error in drain current versus gate voltage is below 2% in the moderate                               |    |

|     | and strong inversion region for a wide range of channel radii and channel doping                                |    |

| •   | when compared to TCAD                                                                                           | 27 |

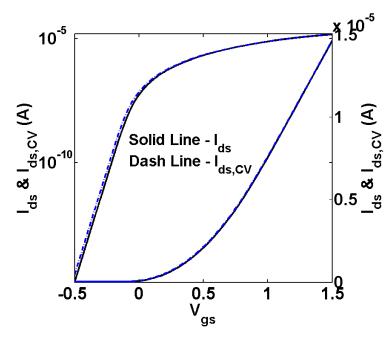

| 2.8 | Comparison of the actual drain current and the approximation used for charge                                    |    |

|     | model showing negligible error in inversion                                                                     | 28 |

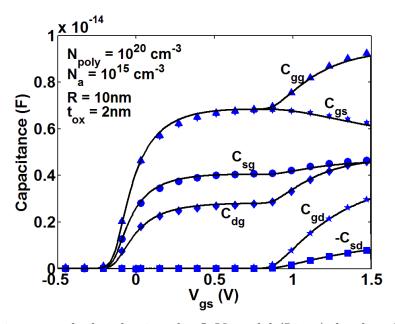

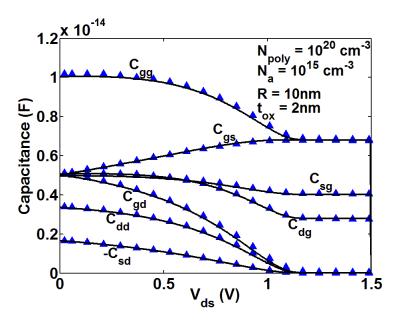

| 2.9  | Capacitances calculated using the Q-V model (Lines) developed including polydepletion as a function of gate voltage, $V_{ds} = 1 \mathrm{V}$ shown for a low polysilicon doping overlayed against those obtained from TCAD (Symbols) simulations. The |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.10 | model agrees well with simulated results                                                                                                                                                                                                              | 32       |

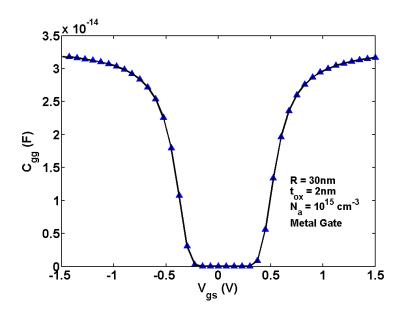

| 2.11 | (a) Gate capacitance as a function of gate voltage obtained for a device exhibiting accumulation capacitance. (Lines:Model, Symbols:TCAD), $V_{ds} = 0 \text{ V}$                                                                                     | 33       |

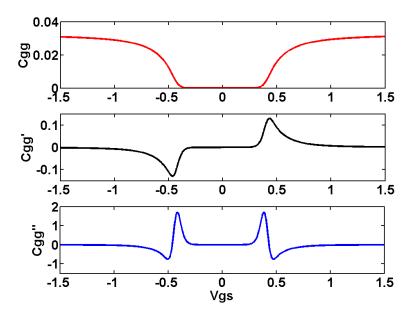

|      | Derivatives of gate capacitance exhibiting model smoothness                                                                                                                                                                                           | 34       |

| 2.14 |                                                                                                                                                                                                                                                       |          |

| 2.15 | : Model)                                                                                                                                                                                                                                              | 35       |

| 2.16 | Measurement data, Lines: Model)                                                                                                                                                                                                                       | 35       |

|      | predicted by the model (Lines) agrees well with the measurement data (Symbols) Drain current characteristics as a function of drain voltage for both NMOS and                                                                                         | 36       |

|      | PMOS.(Symbols: Measurement data, Lines: Model)                                                                                                                                                                                                        | 36       |

|      | : Measurement data, Lines : Model)                                                                                                                                                                                                                    | 37       |

| 2.19 | Gummel Test: $1^{st}$ , $2^{nd}$ and $3^{rd}$ derivatives of drain current are continuous and symmetric when a symmetric voltage is applied across the source and drain and                                                                           | 25       |

| 2.20 | a symmetric set of parameters is used in the model                                                                                                                                                                                                    | 37<br>38 |

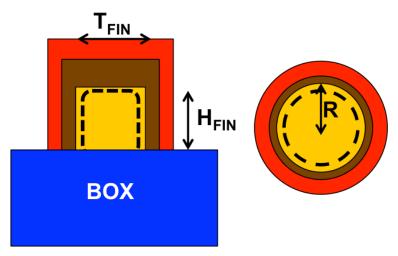

| 3.1  | Channel cross-section of a FinFET on SOI substrate and a Gate-All-Around FET.                                                                                                                                                                         | 00       |

| 3.2  | The dotted lines represent the presence of the charge centroid being away from the oxide-channel interface due to QM the carriers in the channel Simulated charge density distribution in the channel along the diameter of cylin-                    | 40       |

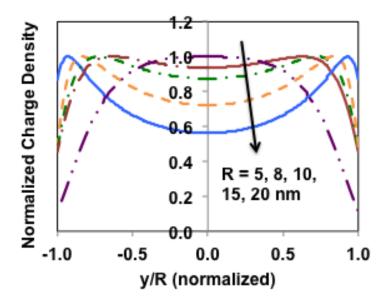

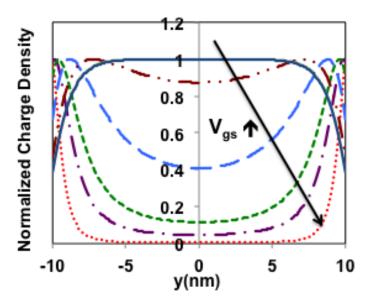

| J.=  | drial gate (CG) FET strucutre in sub-threshold region for different channel radii.  Lines: TCAD simulation                                                                                                                                            | 42       |

| 3.3  | Tracking the change in charge density distribution in the channel for a $R=10\mathrm{nm}$ CG FET for increasing gate bias from $0\mathrm{V}$ to $2\mathrm{V}$ . Lines: TCAD simulations                                                        | 43         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

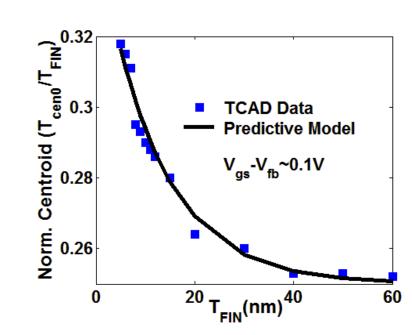

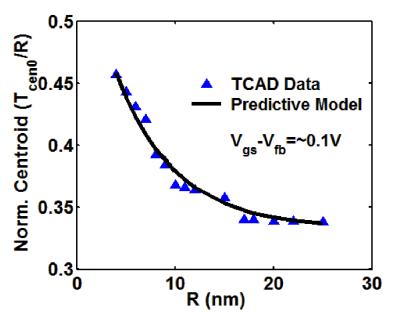

| 3.4  | Charge centroid for low gate bias has a geometric dependence and takes values in between the asymptotic values calculated in Eqn.(3.3) for a DG FET with                                                                                       |            |

|      | rectangular cross-section. Value extracted for $T_0 = 12 \mathrm{nm}$                                                                                                                                                                          | 44         |

| 3.5  | Charge centroid for low gate bias has a geometric dependence and takes values in between the asymptotic values calculated in Eqn.(3.6) for a CG FET with                                                                                       |            |

|      | circular cross-section. Value extracted for $R_0 = 6 \mathrm{nm}.$                                                                                                                                                                             | 45         |

| 3.6  | After a certain critical charge in the channel, the centroid shifts towards the gate-oxide channel interface with increasing gate bias. Symbols: TCAD simulations,                                                                             |            |

| 3.7  | Lines: Proposed compact model                                                                                                                                                                                                                  | 46         |

|      | inversion charge closer to the interface even for low gate bias. Inversion charge centroid for a CG FET structure for intrinsic and moderate channel doping.                                                                                   |            |

|      | Symbols: TCAD simulations, Lines: Proposed compact model                                                                                                                                                                                       | 47         |

| 3.8  | Small signal gate capacitance vs. gate terminal bias for a long channel double gate FET ( $T_{FIN} = 15  \text{nm}$ , $Tox = 1.5  \text{nm}$ ). Symbols: TCAD simulations, Lines:                                                              |            |

|      | Model in Eqn.(3.10) incorporated in BSIM-CMG                                                                                                                                                                                                   | 49         |

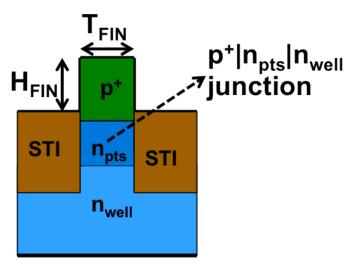

| 3.9  | Cross-section of a bulk p-FinFET showing (a) punch-through stop implant below                                                                                                                                                                  |            |

| 3.10 | the fin. Gate and oxide regions not shown                                                                                                                                                                                                      | 49         |

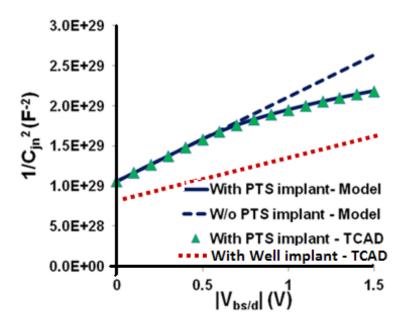

| 3.11 | shown                                                                                                                                                                                                                                          | 50         |

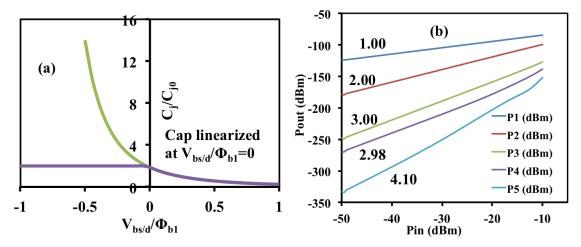

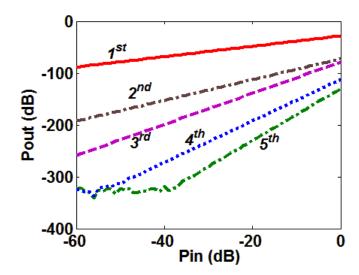

| 3.12 | TCAD)                                                                                                                                                                                                                                          | 51         |

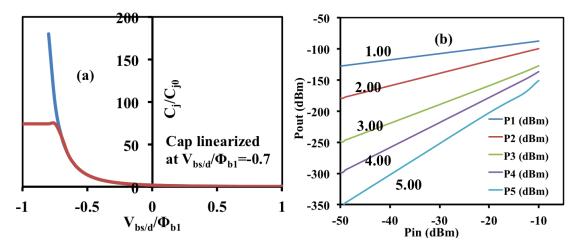

| 3.13 | showing wrong slopes for the $4^{th}$ and $5^{th}$ harmonic output power (a) The first derivative of junction capacitance using the linearization in Eqn.(3.18) with $k = 0.7$ . (b) Results of harmonic balance test for a PMOS passive mixer | 53         |

|      | configuration showing correct slopes for the $4^{th}$ and $5^{th}$ harmonic output power.                                                                                                                                                      | 54         |

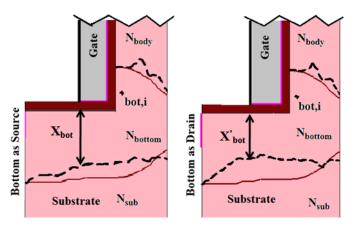

| 4.1  | Among the viable device architectures for a gate-all-around transistor, the vertical cylindrical gate (CG) FET displays both structural asymmetry and process induced asymmetry w.r.t. Top electrode being used as the Drain or the Source     |            |

| 4.2  | of the transistor                                                                                                                                                                                                                              | 57         |

|      | to Bottom. TCAD structure with a Gaussian doping profile and up to one decade                                                                                                                                                                  | <b>.</b> . |

|      | gradation between source and drain                                                                                                                                                                                                             | 58         |

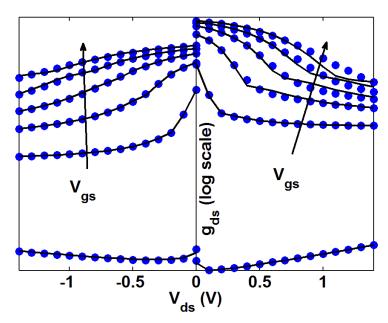

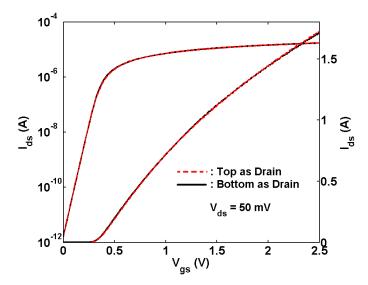

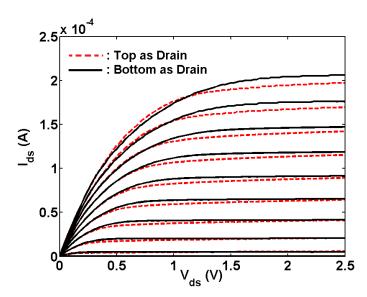

| 4.3  | Linear region drain current is oblivious to Top being Drain or Source for non-uniform channel doping. Lines: TCAD Results | 59  |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 4.4  | Top as Drain condition exhibits lower $V_{th}$ (lower source-side doping) as well as                                      |     |

|      | lower $I_{on}$ (higher drain side doping => lower $V_{dsat}$ ) in saturation region for a                                 |     |

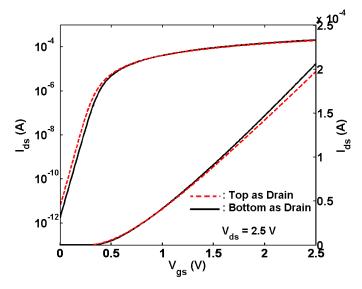

|      | non-uniform channel doping. Lines: TCAD Results                                                                           | 60  |

| 4.5  | The asymmetric DIBL induced $V_{th}$ shift also emphasizes itself as slightly different                                   |     |

|      | output conductance in $I_{ds} - Vds$ characteristics. Lines: TCAD Results                                                 | 61  |

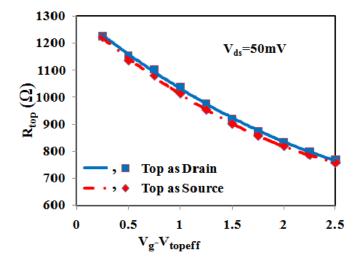

| 4.6  | Gate voltage dependence of source / drain region resistance. Increasing gate                                              |     |

|      | voltage leads to increasing accumulation of electrons leading to decrease in re-                                          |     |

|      | sistance. Symbols: Extracted resistance from TCAD using a floating electrode,                                             |     |

|      | Lines: Asymmetry aware resistance model                                                                                   | 62  |

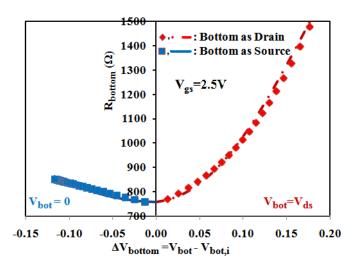

| 4.7  | Resistance for the bottom electrode drift region for bottom as drain and bottom                                           |     |

|      | as source configuration. Quasi-saturation of the drift region leads to apparent                                           |     |

|      | increase in the resistace of the region when operating as the drain of the vertical                                       |     |

|      | CG-FET. Symbols: Extracted resistance from TCAD using a floating electrode, Lines: Asymmetry aware resistance model       | 63  |

| 4.8  | Structurally different top and bottom junctions exhibit different resistances (R).                                        | 0.  |

| 4.0  | The bottom junction exhibits additional increase in R ( $\propto X_{bot}^{-1}$ ) when used as                             |     |

|      | drain due to reverse biased bottom-substrate junction depletion width fluctuation.                                        | 64  |

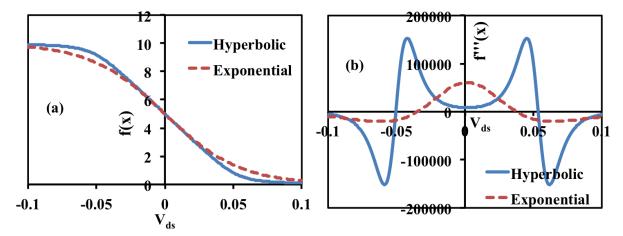

| 4.9  | (a) Hyperbolic and Exponential functions used to create a smooth transition                                               | 0.  |

|      | from 10 to 0 such that their first derivatives at $V_{ds} = 0 \text{ V}$ are equal. (b) The third                         |     |

|      | derivatives of the smoothing functions in (a) are markedly different                                                      | 65  |

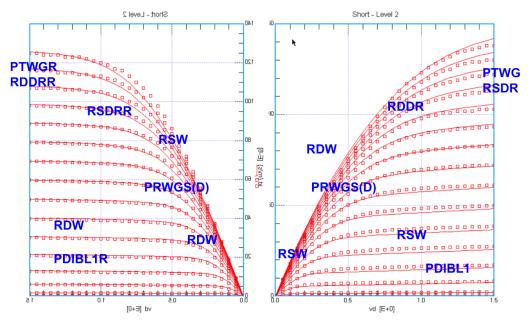

| 4.10 | Region of influence of asymmetric drift region resistance and asymmetric velocity                                         |     |

|      | saturation parameters on drain current curves for both top as drain and top as                                            |     |

|      | source configuration during the process of parameter extraction                                                           | 68  |

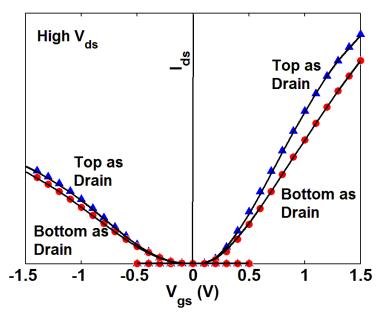

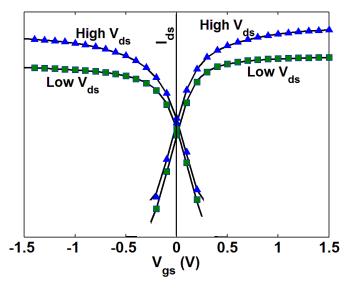

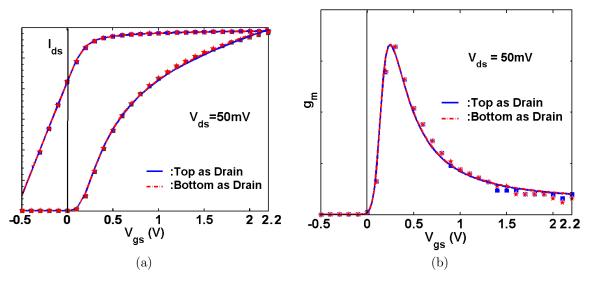

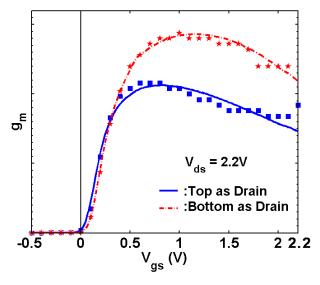

| 4.11 | (a) Linear region drain current for the top as drain and bottom as drain con-                                             |     |

|      | figurations shows no asymmetry. (b) Linear region transconductance, $(G_{m,lin})$                                         |     |

|      | indicates that there is no asymmetry arising from mobility degradation in the                                             |     |

|      | channel. $G_{m,lin}$ also depends on sum of the source and drain resistances which                                        |     |

|      | is independent of the configuration. Symbols: Hardware Silicon Data, Lines: BSIM-CMG Model enhanced for asymmetry         | 69  |

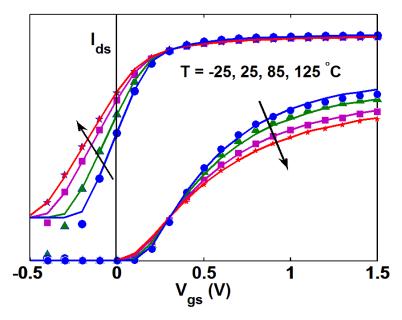

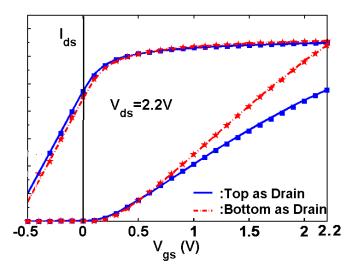

| 4 19 | Saturation region drain current exhibits asymmetry in off-current (due to asym-                                           | Uē  |

| 1.12 | metric DIBL) and asymmetry in on-current as well (due to asymmetric on-set                                                |     |

|      | of saturation) Symbols: Hardware Silicon Data, Lines: BSIM-CMG Model en-                                                  |     |

|      | hanced for asymmetry                                                                                                      | 70  |

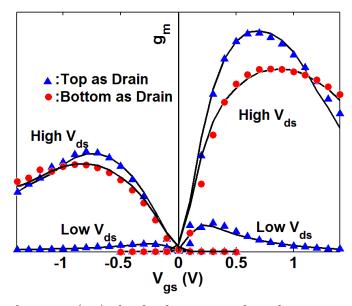

| 4.13 | Transconductance in saturation region, $G_{m,sat}$ , shows marked asymmetry in its                                        |     |

|      | characterisitics with different amount of degradation. Symbols: Hardware Silicon                                          |     |

|      | Data, Lines: BSIM-CMG Model enhanced for asymmetry                                                                        | 70  |

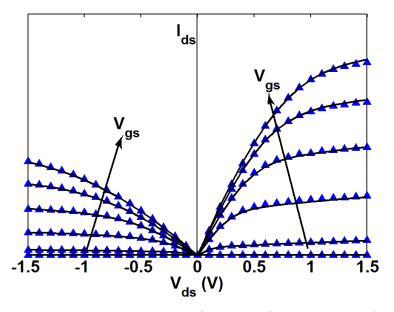

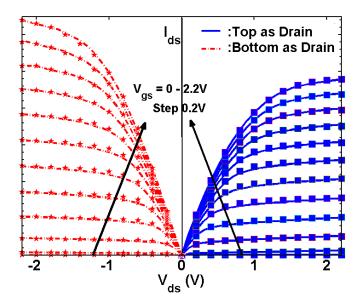

| 4.14 | Drain curent vs. drain voltage for various gate voltage for both the top as drain                                         |     |

|      | and bottom as drain configurations. Negative $V_{ds}$ is used to indicate the bottom                                      |     |

|      | as drain configuration to showcase both the configurations in one plot. Symbols:                                          | _ ~ |

|      | Hardware Silicon Data, Lines: BSIM-CMG Model enhanced for asymmetry                                                       | 71  |

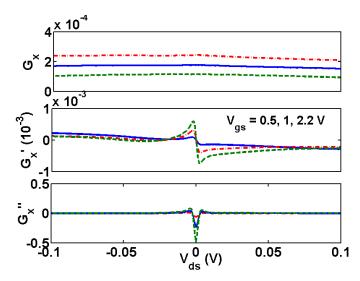

| 4.15       | Results from a drain current continuity test. First, second and third derivatives of current in response to a symmetric drain-source voltage source are continuous and smooth around $V_{ds} = 0 \text{ V}$ Symbols: Hardware Silicon Data, Lines: BSIM-CMG Model enhanced for asymmetry                                          | 71 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

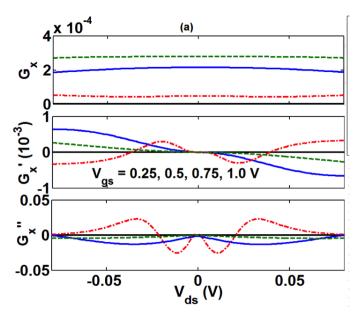

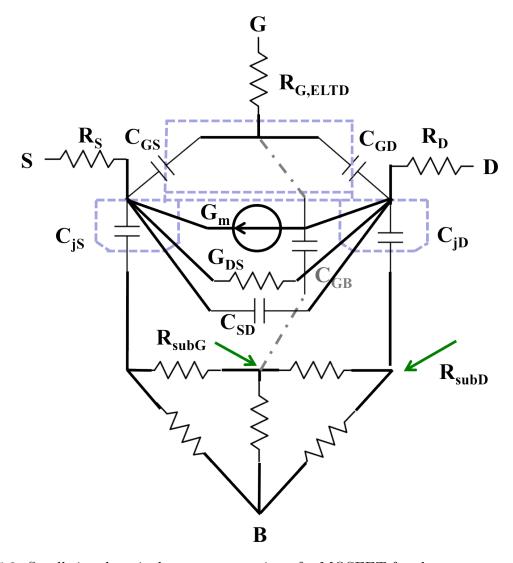

| 5.1<br>5.2 | Overlay of intrinsic MOSFET and it's high frequency relevant model components. Results of Gummel Symmetry Test verify the symmetry and continuity of the                                                                                                                                                                          | 74 |

| 5.3        | BSIM6 drain current and its higher order derivatives, [40]                                                                                                                                                                                                                                                                        | 75 |

| 5.4        | terminal with a single tone                                                                                                                                                                                                                                                                                                       | 76 |

| 5.4        | capacitance, trans-capacitance and its higher order derivatives, [40]                                                                                                                                                                                                                                                             | 76 |

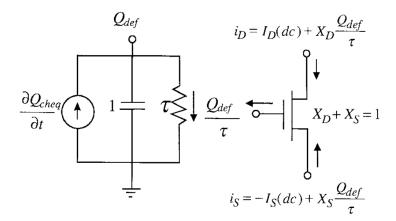

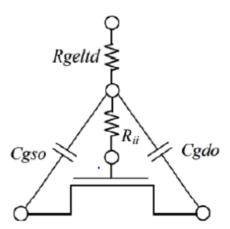

| 5.5        | Model options in BSIM6 for capturing non-quasi static effects. For this work NQSMOD=1 refers to (a) and NQSMOD=2 refers to (b)                                                                                                                                                                                                    | 80 |

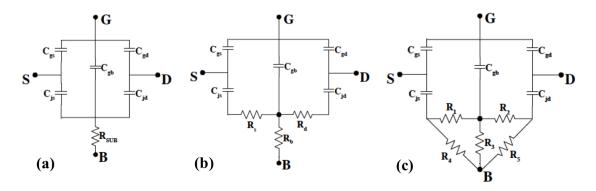

| 5.6        | Some possible substrate / well-region network models - (a) one resistor (1R), (b)                                                                                                                                                                                                                                                 | 80 |

|            | three resistor (3R) and (c) fice resistor (5R) networks                                                                                                                                                                                                                                                                           | 80 |

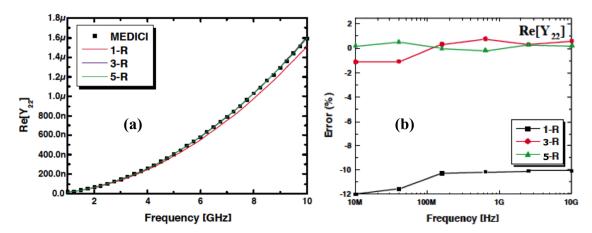

| 5.7        | (a) Output conductance, $Re(Y_{dd}) = Re(Y_{22})$ plot surveying the accuracy of various substrate network models in comparison to TCAD data (b) Error in the resultant fit shows that the five resistance substrate network best describes the                                                                                   |    |

|            | substrate for frequencies above 1 GHz, [66]                                                                                                                                                                                                                                                                                       | 81 |

| 5.8        | Small signal equivalent representation of a MOSFET                                                                                                                                                                                                                                                                                | 83 |

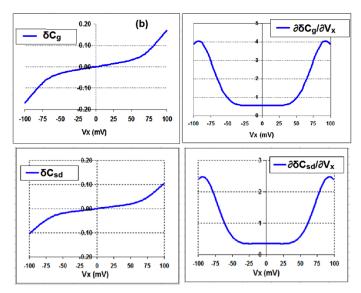

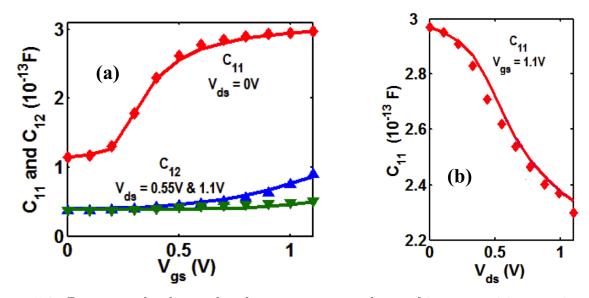

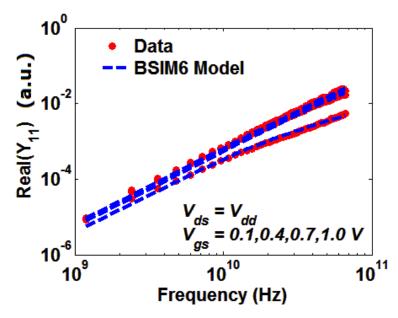

| 5.9        | Process technology related parameters, overlap + fringe parasitic capacitance,<br>short-channel capacitance parameters are extracted from $C_{gg} = C_{11}$ and $C_{gd} =$                                                                                                                                                        |    |

|            | $C_{12}$ . Symbols=Silicon Data, Lines=BSIM6 Model                                                                                                                                                                                                                                                                                | 84 |

| 5.10       | DC measurements from the same structure are used to extract parameters for mobility, series resistance, velocity saturation and output conductance. Accurate fit of not only the drain current but also the trans-conductance, output conductance (not shown here) and its derivatives are obtained in this step. Symbols=Silicon |    |

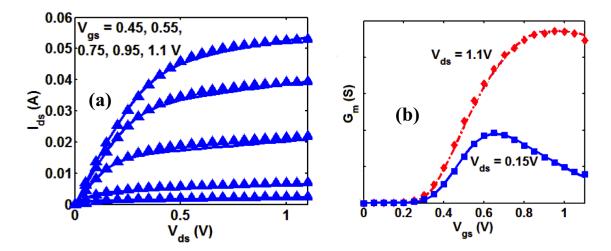

|            | Data, Lines=BSIM6 Model                                                                                                                                                                                                                                                                                                           | 85 |

| 5.11       | Junction capacitance parameters are extracted from $C_{jd} = C_{out}$ vs. $V_{ds}$ curve at off state condition of the device $(V_{gs} = 0 \text{ V})$ . Symbols=Silicon Data, Lines=BSIM6                                                                                                                                        |    |

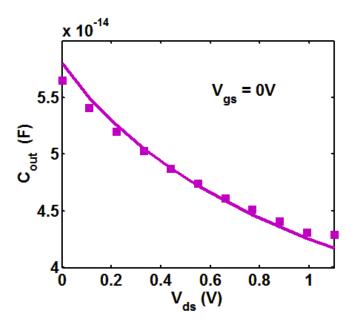

|            | Model                                                                                                                                                                                                                                                                                                                             | 86 |

| 5.12       | The resistance values of the substrate network are extracted from the $R_{sub,d} = R_{out}$ curve along frequency at off state condition of the device. Symbols=Hardware                                                                                                                                                          |    |

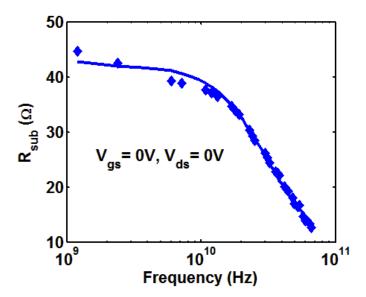

|            | Data, Lines=BSIM6 Model                                                                                                                                                                                                                                                                                                           | 87 |

| 5.13       | are extracted from the $R_{gg}$ vs. $V_{gs}$ curve. The channel-induced gate resistance                                                                                                                                                                                                                                           |    |

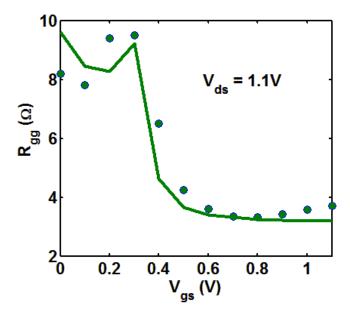

|            | component will already captured accurately if the segmentation based NQS model were used. Symbols=Hardware Data, Lines=BSIM6 Model                                                                                                                                                                                                | 88 |

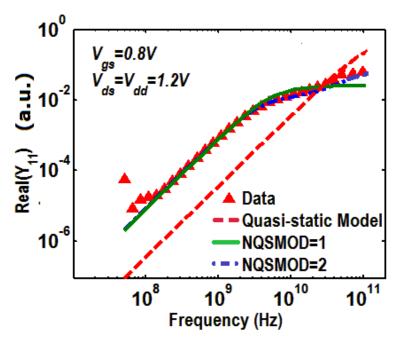

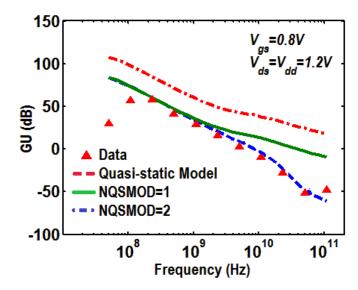

| 5.14     | The NQS models in BSIM6 help capture the high frequency behavior of the input admittance $(Re(Y_{gg}) = Re(Y_{11}))$ while the quasi-static model fails to capture the |     |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | same. Symbols=Silicon Data, Lines=BSIM6 Model                                                                                                                          | 91  |

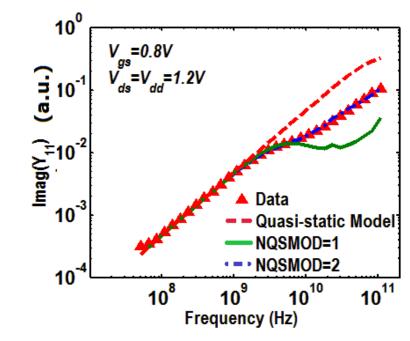

| 5.15     | The intrinsic and extrinsic capacitance model determine the behavior of the                                                                                            |     |

|          | $Im(Y_{gg}) = Im(Y_{11})$ curve. Symbols=Silicon Data, Lines=BSIM6 Model                                                                                               | 92  |

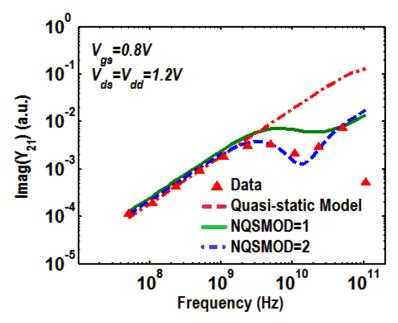

| 5.16     | Symbols=Silicon Data, Lines=BSIM6 Model                                                                                                                                | 93  |

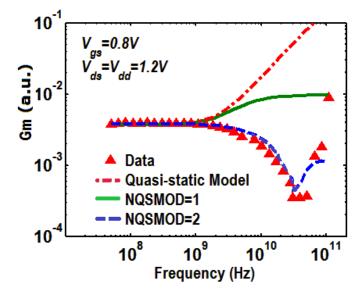

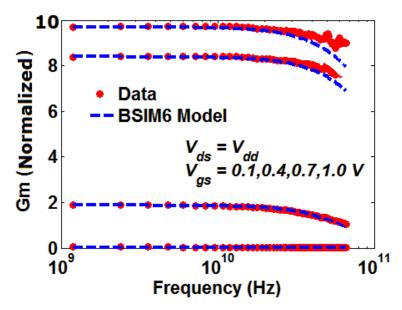

| 5.17     | The channel segementation model predicts the trans-conductance, $G_m$ roll off at high frequencies while the quasi-static model is in error while predicting the       |     |

|          | behavior of the device for frequencies approaching $F_t$ . Symbols=Silicon Data,                                                                                       |     |

|          | Lines=BSIM6 Model                                                                                                                                                      | 93  |

| 5.18     | The resultant model predicts the Mason's Gain, GU of the transistor (that is invariant under addition of lossless components around the FET) accurately up             |     |

|          | to 100 GHz. Symbols=Silicon Data, Lines=BSIM6 Model                                                                                                                    | 94  |

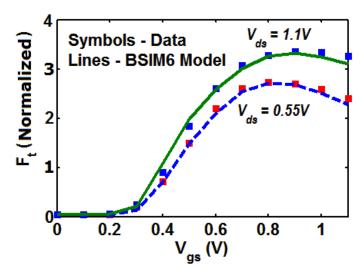

| 5.19     | The bias dependence of the cut-off frequency, $F_t$ relies on the model accuracy                                                                                       |     |

|          | in predicting the trans-conductance, output conductance and device capacitance.                                                                                        |     |

|          | Symbols=Silicon Data, Lines=BSIM6 Model                                                                                                                                | 94  |

| 5.20     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                  | 0.1 |

| 0.20     | capture the bias and frequency dependence of the input admittance, $Re(Y_{qq}) =$                                                                                      |     |

|          | $Re(Y_{11})$ . Symbols=Silicon Data, Lines=BSIM6 Model                                                                                                                 | 95  |

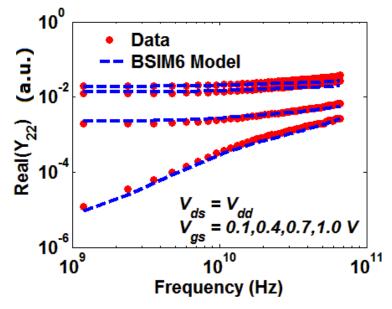

| 5.21     | Output conductance model (for low frequency) and substrate network model (for                                                                                          |     |

| J        | high frequency) have been extracted accurately to predict the hardware output                                                                                          |     |

|          | conductance $(Re(Y_{dd}) = Re(Y_{22}))$ data. Symbols=Silicon Data, Lines=BSIM6                                                                                        |     |

|          | Model                                                                                                                                                                  | 95  |

| 5 22     | The resultant model with the gate induced resistance non-quasi static model                                                                                            | 50  |

| 0.22     | predicts the low-frequency trans-conductance, $G_m$ across bias and as well as the                                                                                     |     |

|          | roll off when approaching frequencies close to the cut-off frequency, $F_t$ of the                                                                                     |     |

|          | device accurately. Symbols=Hardware Data, Lines=BSIM6 Model                                                                                                            | 96  |

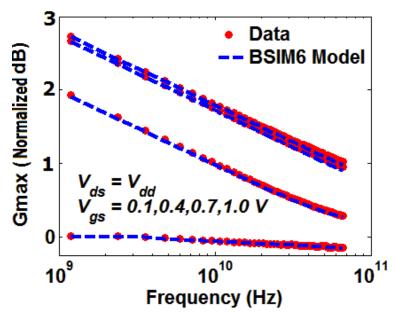

| 5.23     | The model predicts the maximum gain, $G_{max}$ of the device across bias up to $F_t$                                                                                   |     |

| 0.20     | of the device very well. Symbols=Hardware Data, Lines=BSIM6 Model                                                                                                      | 96  |

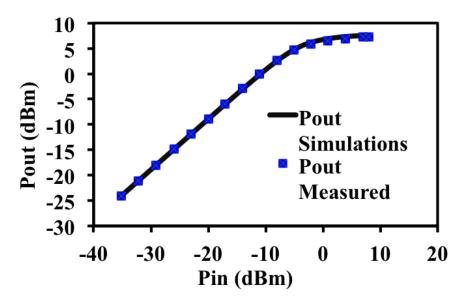

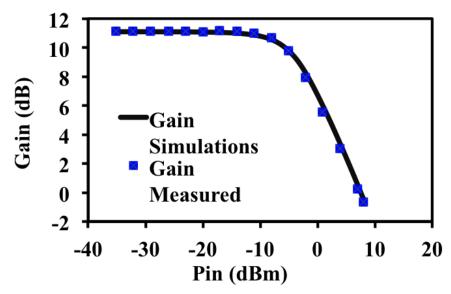

| 5 24     | Large signal response of the low-noise amplifier at 12 GHz. Symbols=Hardware                                                                                           | 50  |

| 0.21     | Data, Lines=BSIM6 Model                                                                                                                                                | 97  |

| 5.25     |                                                                                                                                                                        | 51  |

| 0.20     | Data, Lines=BSIM6 Model                                                                                                                                                | 97  |

|          | Data, Lilles—Balivio woder                                                                                                                                             | 91  |

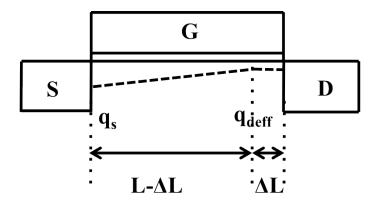

| B.1      | MOSFET cross-section showing the channel charge (dotted lines) along the chan-                                                                                         |     |

|          | nel. Channel gets pinched off at higher $V_{ds}$ at $L - \Delta L$ and the channel charge                                                                              |     |

|          |                                                                                                                                                                        | 119 |

| $C^{-1}$ | A simulfied lammed and all of the maket, at all as MOCEPTE 111 1 2 C                                                                                                   |     |

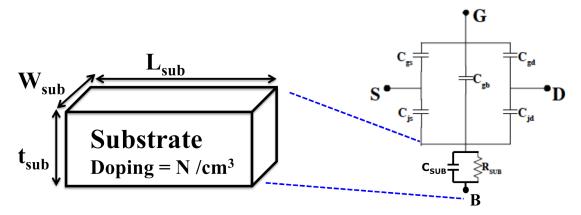

| C.1      | A simplified lumped model of the substrate below a MOSFET with doping of                                                                                               |     |

|          | $N \mathrm{cm}^{-3}$ . At high frequencies the substrate behaves both like a capacitor and a                                                                           | 100 |

|          | resistor                                                                                                                                                               | 122 |

| C.2 | Substrate cut-off frequency, $f_{sub}$ around and beyond which capacitive effects of the substrate dominate as a function of p-type Boron doping for a Silicon substrate | 2123 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

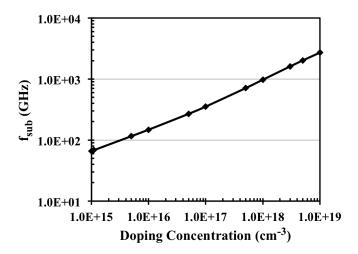

| D.1 | A relaxation time approach for capturing non-quasi static effects. R-C sub-circuit representation of Eqn.(D.3) for SPICE implementation and the corresponding            |      |

|     | terminal charges                                                                                                                                                         | 126  |

| D.2 | A channel induced gate resistance, $R_{ii}$ is added in series with the gate physical                                                                                    |      |

|     | electrode resistance to capture the non-quasi static effect for gate terminal excited                                                                                    |      |

|     | FETs                                                                                                                                                                     | 127  |

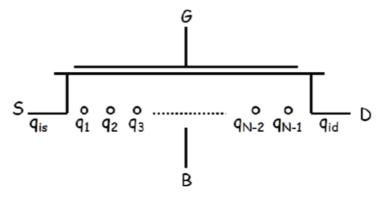

| D.3 | $N_{SEG} = N$ charge segments in a MOSFET channel for non-quasi static effects                                                                                           |      |

|     | simulation. $q_i$ represents the channel charge at the $i^{th}$ intermediate node                                                                                        | 128  |

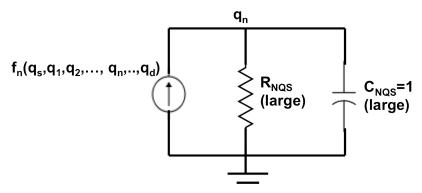

| D.4 | R-C sub-circuit representation of Eqn.(D.15). The node voltage here represents                                                                                           |      |

|     | the channel charge at the $n^{th}$ intermedite node                                                                                                                      | 130  |

#### Acknowledgments

This dissertation thesis stands on the shoulders of two people who made it possible for me - Prof. Chenming Hu and Prof. Ali Niknejad who both accepted me as a graduate student five years ago. I would like to thank them for allowing me to work on a high visibility project. I am indebted to them for the inculcating in me the art of innovation and in-depth analysis. Prof. Hu has been a very patient teacher in my formative years and provided me with endless support throughout my graduate school. Prof. Niknejad's thoughtful criticism and constant encouragement have helped me immensely in my research. He would often times amaze me by bringing up a view point I wouldn't have though about despite all the rigor of research I would have put in. I also thank UC Berkeley (for the Frank and Lucas Margaret Fellowship for my first year of graduate studies), Semiconductor Research Corporation and the Compact Model Council for funding my research and supporting me generously.

Thanks to the people that kept me going and made this dissertation possible.

I would like to thank Prof. Sayeef Salahuddin and Prof. Junqiao Wu for taking off time from their busy schedules to serve on my qualification exam committee. Their valuable suggestions on my on-going research was timely for mid-course corrections to my work. I would also like to thank Prof. Paul Wright for his feedback and help shaping this dissertation. Prof. Jaijeet's deep insights in design automation helped me understand how the models

interacted with the SPICE simulators and I am thankful to him to allow me to contribute to his research as well in this process.

Over the course of five years I was fortunate to have interacted with numerous members from semiconductor industry across the world who served as wonderful mentors with their critical feedback 24/7. Early morning telecons to late night email exchanges kept my determination consistent. My day begun with the rise of sun in Japan (not the US) with Peter Lee and moved on to interactions with the modeling group at TSMC Taiwan (Min-Chie Jeng, Ke Wei Su and Wai Kit Lee), the Mentor Graphics SPICE modeling team at Cairo, Egypt (Ahmed Ramadan, Selim Mohamed and Abo-Elhadid Ahmed), the EKV modeling team at EPFL Switzerland, our earliest adopters and well-wishers Chung-Hsun Lin and Richard Williams at IBM New York, Sagnik Dey at Texas Instruments Dallas, our supporters at Qualcomm San Diego, GLOBALFOUNDRIES Sunnyvale and Proplus at San Jose. At a certain period of time the BSIM-CMG implementation team, in my opinion consisted of Weidong Liu, Joddy Wang and Qingxue Wang at Synopsys, Fulong Zhao and Jushan Xie at Cadence and myself at Berkeley. We owe the code quality control to Brian Chen at Accelicon (now Agilent). Special thanks to all of them for showing the greater picture of the SPICE model ecosystem in the semiconductor industry. It was great interacting with you all and owe all my learning outside academia to you.

I would like to thank the Texas Instruments SPICE Modeling team (Xin Zhang, Krish Dandu, Sagnik Dey) for my internship experience that provided me a chance to apply the developed models to realistic scenarios. I am grateful to Sriram Balasubramanian for giving me an opportunity to work at GLOBALFOUNDRIES as an intern on leading edge CMOS technologies.

Thanks to my peers in Device Group and IC Group (BWRC) who made my experience at Berkeley most special - Darsen and Reinaldo for patiently spending a lot of time bringing me up to speed in my research in device physics and modeling, Jiashu, Siva and Steven for guiding me through my first IC tape-out process, Angada, Asif, Byron, Juan, Kartik, Khalid, Nattapol, Navid, Nuo, Rumi, Shijing, Sung and Tanvir for the invaluable and endless discussions on different research topics. Thanks to all my friends beyond Berkeley who kept my sanity levels in check and kept my life fun and interesting all through my graduate school - Ashwin, Krishna Teja, Shrey, Saaransh, Sudeep, Ruchi and Vikas. My stint at SPICMACAY wouldn't have been memorable if not for the good camaraderie with Aditya, Anuj, Debanjan, Sharanya, Venky and Yasaswini.

Thanks to my apartment-mates at Berkeley Chintan and Siva for their unconditional support through the ebbs and tides of graduate school and for being partners in kitchen crime (a.k.a. cooking).

Finally I would like to express my gratitude to my mom Usha and dad Venu for their immense sacrifices to ensure I received the best possible education. My aunts, uncles and grandma for their constant encouragement, guidance and support throughout my 25 years in school. They all played an important role in goal setting in my life. To my sister Sriranjani for always being there for me. Lastly I would like to thank my fiancèe Soundarya for being patient, supportive and for making sure I stayed on course while I write this thesis.

## Chapter 1

### Introduction

The semiconductor industry is one of the few engineering areas where *first time right* product design is expected. This creates the need for complete understanding of underlying physical phenomenon of the devices and process technology. Also, today the technology cadence of many consumer electronic products have rapid refresh rates that their shelf life seem to be approaching that of a banana. These rapid refresh rates require faster design cycles which in turn need speedy and accurate simulations to predict design performance improvements. Compact SPICE Models take a seat right in between these two paradigms. This dissertation will present some key advances created in the area of Compact SPICE Models and discuss their benefits for integrated circuit (IC) design.

#### 1.1 Industry Relevance

With increasing technology complexity and ever-decreasing time to market for electronic products from newer technology nodes, IC design and technology development cannot remain de-coupled. Unlike in the past where product development happened after process technology maturity to benefit from high yields, today IC design houses closely collaborate and engage with their foundry partners as much as 3 years prior. Product definition and intellectual property (IP) development begin even before the availability of first silicon hardware results. Compact SPICE models especially BSIM family of models are very fundamental to this transaction between the IC design houses and foundries. The exchange of information between the two parties happen at a number of stages from product definition to final product validation through a set of technology definitions called a process design kit (PDK), Fig. 1.1. Compact SPICE models are an integral part of this PDK enabling accurate IC design simulations.

Figure 1.1: Semiconductor technology-IC design interaction along the different phases of product development. The dotted lines represent exchange of information in the form of Compact Models for SPICE.

#### 1.2 Advanced MOSFET Device Architectures

The legacy bulk planar MOSFETs have hit the limits in terms of scaling, [1]. With ever shrinking scaling length for increasing MOSFET performance (speed) the gate terminal of the MOSFET was no longer in control of the channel yielding the control more to the drain terminal. This led to increasing sub-surface leakage current that determined the off-state / stand-by power consumption of the system which has become more important with the advent of always-on mobile devices. In order to stem this leakage current one could enhance the gate control over the channel by either increasing the gate capacitance or enhancing the doping in the channel. An increase in gate capacitance can be achieved either by thinning the gate oxide or by introducing materials with higher dielectric constant  $(\kappa)$ . As thinning the silicon oxide hit the limits (due to increased direct tunneling based gate leakage) around the 65 nm technology node, high- $\kappa$  materials were introduced in the 45 nm technology node, [2]. However even this solution begun to hit the limit when approaching sub-20 nm node. The limit for how much high a doping can be introduced in the channel is set by the mobility degradation due to scattering, [3]. Strained channel that was introduced 90 nm technology node as a mobility enhancement technique also ran out of steam as there is a limit to the amount of stress the channel can experience before material defects arise degrading the performance thereon. [4].

Figure 1.2: Various Symmetric Multi-Gate Transistor architectures

#### 1.2.1 Symmetric Multi-Gate FET - FinFETs

At this juncture there was a need for novel device architectures that help continue the device scaling. Three dimensional multi-gate device architectures were foreseen as the natural replacement to the two dimensional planar device counterparts, [5]. Symmetric multi-gate transistors comprise of multiple gate terminals on more than one side of the channel controlled by a single voltage, Fig.1.2. FinFETs (an extension of the double-gate FET) were first demonstrated in silicon a decade ago, [6]. They have been adopted by the industry as a solution for the sub-22 nm node recently for logic / digital circuit design technology where higher performance and lower power are of prime importance, [7]. These multi-gate devices present the following advantages for circuit design,

- No doping required in the channel due to better gate control of the channel. The threshold voltage,  $V_{th}$  is in-turn set by the metal gate work-function.

- Higher channel mobility due to lower scattering in the channel (no dopants in the channel). The mobility degradation due to vertical field is also lower for achieving the same amount of inversion level as a bulk-planar MOSFET.

- Better short channel control by the gate leads to  $\approx 60\,\mathrm{mV}$  per decade sub-threshold swing thereby making the transistor a better switch.

- Better short channel control also leads to lower drain-induced barrier lowering especially  $V_{th}$  shift due to drain bias.

- The optimal device design is achieved where there is a slight underlap of the gate terminal over the source-drain region leading to lower gate-induced drain leakage or lower off-current. The on-current due to increased access resistance is traded-off with off-current due to leakage.

Figure 1.3: DRAM transistor device technology progress over the years.

Due to very little doping in the channel these devices are fully-depleted unlike the bulkplanar MOSFETs that operate in the partially depleted regime. Strained channel and high- $\kappa$  materials as used in bulk planar devices can also be used here. In realistic FinFETs some amount of body-doping is required to be employed to cater to multiple- $V_{th}$  that are required for contemporary system-on-chip (SoC) technologies for better power-performancearea trade-off without affecting the device variability due to random dopant fluctuations [8]. The next-generation FinFETs with shorter channel lengths for better performance and short-channel control can be obtained by thinning the fin/channel which can be controlled by advances in lithography.

# 1.2.2 Symmetric Multi-Gate FET - Surround Gate / Gate-All-Around FETs

The ultimate architecture in terms of multi-gate devices would be the surround gate / gate-all-around / quadruple gate / nano-wire transistors where the gate surrounds the channel on all four sides, Fig.1.2. These devices have the same benefits as the FinFETs with even better short-channel control. Horizontal nanowire transistors though demonstrated in research could pose a challenge for large scale manufacturing mainly due to increasing complexity of having to undercut the channel in order to wrap the gate below and controlling the channel thickness uniformly across the wafer. The DRAM bit-cell transistor has been following its own course in terms of device architecture seeking a different set of trade-offs than what is required for logic technology devices, [9]. Bulk planar MOSFETs to recessed channel MOSFETs to saddle MOSFETs (similar to FinFETs) have all been used in an attempt to contain the transistor leakage that directly affects the bit retention rate of the DRAM bit cell. Vertical cylindrical gate (CG) FETs are seen as the replacement for the current generation transistors, Fig.1.2. A DRAM bit-cell consists of a capacitor where the memory

Figure 1.4: Layout of an one-transistor one-capacitor DRAM technology demonstrating the move from a  $6F^2$  to a more compact  $4F^2$  per bit cell enhancing DRAM area density.

Figure 1.5: Various Asymmetric Multi-Gate Transistor architectures

bit is stored and a transistor that behaves as a switch to control the read and write to the capacitor. The transistor together with the capacitor if placed beside each other would require about  $8F^2$  are where F is the minimum feature size of a technology determined by lithography patterning limits. In an attempt to increase the DRAM bit-cell area density a staggered bit-line word-line approach (as opposed to orthogonal bit-line and word-line in  $8F^2$  technology) reduced the per cell area to  $6F^2$ . The vertical CG-FET architecture provides the benefit of being able to reduce this area even further to  $4F^2$ , Fig.1.4. A cross-bar type of memory array architecture could now be employed where in the bit-cell capacitor can now be stacked over the transistor itself.

#### 1.2.3 Asymmetric Multi-Gate FETs

Another multi-gate architecture that is also currently being used in IC design is the asymmetric multi-gate transistor, Fig.1.5. The asymmetry could arise from either the device structure (different oxide thickness, different gate work-functions) or through application of

different gate voltages at the different gate terminals. Ultra-thin body transistors that have also been touted as a replacement for bulk-planar transistors is another form of an asymmetric multi-gate device, [10]. Here the second gate is present directly below the channel and could be controlled by a separate contact. These devices also address sub-surface leakage in a similar way as the FinFETs where in the channel is thinned down cutting off the leakage paths. The channel here is horizontal like the planar MOSFET, unlike the FinFET which is vertical. These devices have also seen the light of the day recently, [11]. FinFETs with the top gate etched away results in a channel that is controlled by two different gates on either sides. However for asymmetric multi-gate transistors there is a resultant area impact in having to contact both the gates separately. These devices have not yet been used to their fullest potential. Dynamic biasing of both the gates could have some interesting applications. For digital logic technology, the second gate could be used to dynamically control the  $V_{th}$  of the device in-order to achieve better control of power, performance and process variations in a SoC technology. One could also visualize a single device RF mixer where both the gates could be excited by two different frequency tones and the drain terminal current would then contain the various frequency modulated components.

#### 1.3 Compact SPICE Models

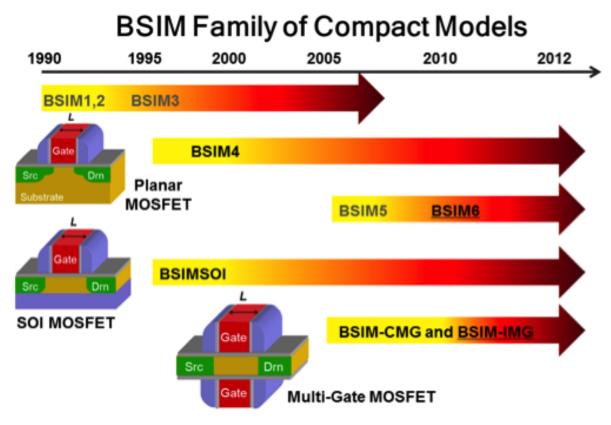

The maturity and wide acceptance of SPICE (an integrated circuit simulator tool) led to the need for compact device models. The initial research for advanced FET compact device models for SPICE began at Berkeley, [12, 13]. With better understanding of the MOSFET and increasing complexity the compact device models became an important area of research in itself leading to the Berkeley SPICE Igfet Model, BSIM. For more than two decades the BSIM group has been advancing the field with research and developments leading to introduction of various industry standard models, Fig.1.6, [14].

A compact model for a semiconductor device is a concise mathematical description of its complex behavior, and it is usually implemented in a computer programming language like C or Verilog-A. Despite the fact that the implementation might consist of thousands of lines of codes, it takes only a fraction of a millisecond for computer simulation tools like SPICE to run the code (for one transistor at a single bias point). In addition, the model's accuracy and quality is of very high importance. The speed and accuracy (1% RMS error after calibration to experimental data) enable simulation tools to verify the functionality and performance of ICs (containing millions of transistors) before an expensive fabrication process takes place. The models are also flexible enough to accommodate technology modifications from multiple foundries. The models undergo continuous innovation with fundamental contributions from universities and important incremental contributions from industry leading to their deployment. Compact Model Council is the industry consortium that proposes, approves and ensures the quality of today's industry standard compact models, [15].

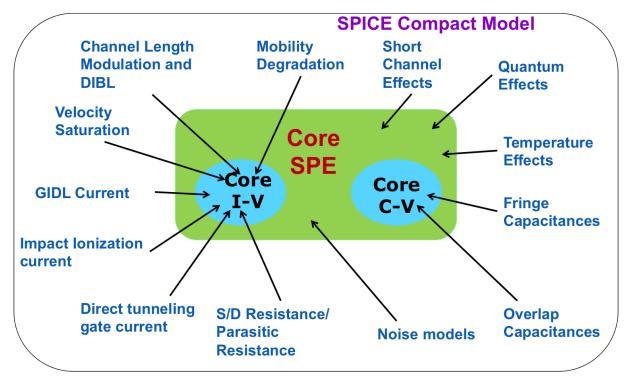

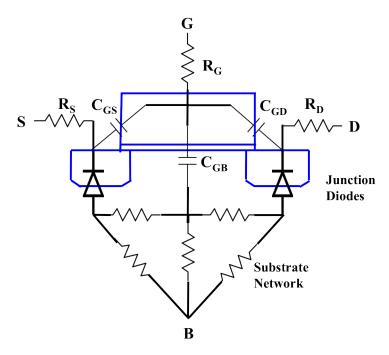

Contemporary MOSFET compact models constitute a core model that contains analytic equations for the terminal currents and charges for an ideal long channel MOSFET, Fig.1.7.

Figure 1.6: Timeline of the BSIM family of compact models. The models in gray (BSIM1-3 and BSIM5) are not supported by the group any longer. The underlined model (BSIM-IMG) is under evaluation/standardization by CMC.

Terminal charges are implemented rather than the device capacitance directly as it would help visualize and maintain charge neutrality in the device. The simulators convert the terminal charges to terminal capacitance. These currents and capacitance are obtained as a function of either the terminal voltages or the source and drain end charge / surface potentials. The currents and capacitance equations are further augmented by various submodels that capture the complex physics of the real device. Some of these sub-models are shown in Fig.1.7 (Also see Appendix A). Some examples of compact models for MOSFET include - BSIM, PSP, EKV and HiSIM for bulk planar MOSFETs, HiSIM-HV for highvoltage MOSFETs, BSIM-CMG for symmetric multi-gate MOSFETs, BSIM-SOI and HiSIM-SOI for MOSFETs built with Silicon on Insulator Technology, [15]. Most compact models have a certain degree of inherent scalability along important physical device parameters like length, width, gate oxide thickness and channel doping etc. All compact models contain many parameters to be tuned/extracted that render just enough flexibility to the model to be able to capture data from multiple foundries and industries. These parameters are estimated from a small set of hardware data and the so tuned compact model's inherent scalablility across geometry helps predict device performance beyond that of available data

Figure 1.7: The various components and structure of contemporary Compact SPICE transistor models.

by extrapolation.

#### 1.3.1 BSIM-CMG

BSIM-CMG (complete multi-gate) is a compact SPICE model developed for symmetric multi-gate FET architectures, Fig.1.2. The model is very versatile and supports a variety of multi-gate FET architectures including double-gate (or a FinFET with a hard-mask on the top), triple-gate (gate wrapped around on three sides), quadruple-gate (gate on all sides with a square or rectangular channel cross-section) and cylindrical gate (gate wrapped around a circular channel cross-section) devices. This dissertation concentrates on the development of a core model for cylindrical gate devices. The details of the core model for the other architectures can be found in [16]. All the core models are physical charge/surface potential based and capture the volume inversion phenomenon of fully-depleted channels. The short channel effects, quantum mechanical confinement effects (also developed in this dissertation), source/drain parasitic resistance and capacitance were all specially developed keeping in view the 3-D device geometry, [17]. Through work in this dissertation, BSIM-CMG also models asymmetric devices such as the vertical CG FET device. The model is continuous (drain current is a single piece analytic equation) and has no discontinuity in its higher order derivatives and is thus usable for analog/RF circuit design. As a result,

BSIM-CMG was voted the first industry standard multi-gate model by the Compact Model Council in 2012.

#### 1.3.2 BSIM6

BSIM6 is a RF relevant update to the legacy industry standard model for bulk-planar MOS-FETs, BSIM4, [18]. BSIM4, a threshold voltage based model and the industry work-horse for digital and analog circuit designs was known to have issues in predicting RF circuit blocks like passive mixers due to discontinuity in the model, [19]. BSIM6 rectifies all the issues and is able to satisfy all RF relevant quality tests. We will discuss more about this in this dissertation. At its core it consists of a physical charge based model adopted from the EKV MOSFET model, [20]. Other than the usual sub-models for capturing a real device (such as mobility degradation, velocity saturation, and output conductance etc.) BSIM6 also has all RF relevant components embedded within the model package itself. We will highlight all of them in this dissertation. BSIM6 shares many of its parameter names with BSIM4 to retain the familiarity. We will discuss a RF CMOS model development procedure in this dissertation using BSIM6 as an example. BSIM6 was accepted as an update by the Compact Model Council in 2013.

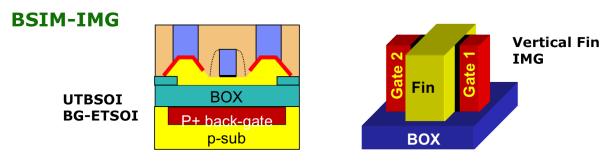

#### 1.3.3 **BSIM-IMG**

BSIM-IMG (independent multi-gate) model is being developed for asymmetric multi-gate devices, Fig.1.5. Similar to BSIM-CMG, BSIM-IMG is also a surface potential based model. The core model assumes a asymmetric double gate FET and supports asymmetry in both gate-oxide thickness and gate work-function, [17, 21]. Owing to its similarity to BSIM-CMG, BSIM-IMG can share all the real device effect models taking into account the back-gate bias dependence. Currently BSIM-IMG supports channel inversion on one side and treats the other gate as a threshold voltage tuning knob, i.e. it does not support inversion on both sides of the channel. Hence this model is more suited for Ultra-thin body transistor technology. Inclusion of dual side inversion has been dealt in [22, 23]. Advances to BSIM-IMG is beyond the goals set for this dissertation.

#### 1.4 Compact Models Usage

Compact MOSFET models are used in various ways. Models tuned to the current technology node are applied for predicting the performance of the next technology node through a process commonly known as technology targeting. Targets for the next generation node are set by performance extrapolation or TCAD device simulations. Compact models thus created are distributed to circuit designer for an early look-ahead of what lies in the next generation. For a digital designer, the MOSFET behaves as a non-ideal switch. The intrinsic delay in switching given by  $C_gV/I_d$ , where  $C_g$  is the gate capacitance, V is the operation

voltage and  $I_d$  is the drain current of the device is an important metric. Compact models are thus required to describe the terminal currents and terminal capacitance accurately in order for precise estimation of power and performance of digital circuits. For analog/mixed signal designers the trans-conductance efficiency - cut-off frequency product to minimize power and ensure adequate bandwidth given by  $G_m/I_d \times F_t$  is an important metric where  $G_m$  is the device trans-conductance. For this the compact model is required to predict not only the currents and capacitance but also the first derivatives accurately (the gain of an amplifier is given by  $G_m/G_ds$  where  $G_{ds}$  is the output conductance). In addition for some circuits device noise is also important and hence the compact models are required to capture all forms of device noise including thermal, channel, flicker and spot noise. RF wireless designs typically contain fewer transistors per chip and heavily rely on the compact models. Important complex metrics that affect the system behavior such as linearity, higher order distortion, frequency mixing and noise folding etc. are all expected to be predicted by the compact models very accurately. This entails the model be able to capture not only the drain currents and capacitance but also predict its derivatives up to third - fifth order. The model should also exhibit no discontinuity in these derivatives. The compact models are implemented and distributed as a part of commercially available SPICE simulators by the Electronic Design Automation (EDA) industry (such as HSPICE, Spectre, and SmartSPICE etc.).

#### 1.5 Scope and Organization of Dissertation

The goal of this dissertation is to advance compact SPICE MOSFET models in light of recent developments in multi-gate device architectures which have become a replacement for bulk planar MOSFETs. In addition there will be a special emphasis on RF CMOS compact models for Analog/RF circuit design.

After a brief review of progress in multi-gate MOSFET core models, in Chapter 2 we will develop a comprehensive core model for a cylindrical gate (CG) FET. The physical charge based core model will include effects of gate poly-depletion and channel doping as well. We will present analytic derivations for ideal long channel drain current and terminal charge / capacitance (the short channel equivalents will be discussed in light of a generic charge based model in Chapter 5). After incorporating the developed core model in BSIM-CMG along with other real device effects we will validate the CG-FET model to both TCAD and hardware data.

In Chapter 3 we will discuss two effects that arise due to the 3-D nature of the symmetric multi-gate devices. In particular we will first develop a simple phenomenological model for the complex geometry and bias dependence of charge centroid due to quantum confinement effects of the carriers in a fin/nano-wire channel. We will validate this model by demonstrating it's importance to predicting moderate inversion region gate capacitance. Next we will look into a subtle yet important double source/drain junction that arises in a FinFET on bulk substrate. We will extend the single junction model found in BSIM4 and validate it

with TCAD simulation results.

In Chapter 4 we will delve deeper into the vertical CG-FET architecture and understand the asymmetric device behavior. We will translate the understanding into compact models to be incorporated in BSIM-CMG. In addition, a mathematical framework to incorporate any source-drain asymmetry in a compact model while retaining the physical nature and continuity of higher order derivatives of the drain current is presented. We then validate this model to hardware data from a 2.2 V vertical CG-FET technology.

In view of the recently developed BSIM6, in Chapter 5 we will establish a generic RF CMOS Model development procedure. First we will critically review all the RF components of the BSIM6 model and understand their RF related effects and limitations. As a part of the critical review, we will also develop a short channel terminal charge / capacitance model applicable for any charge based MOSFET model and highlight its importance in predicting high-frequency behavior. We will also present a detailed discussion on the models that capture the non-quasi static effects of a MOSFET and discuss its correct usage. Finally, a physical model extraction procedure is developed that requires no additional sub-circuit elements. The procedure is validated using hardware S-parameter data from multiple technologies for a bulk planar MOSFET highlighting the benefits of the BSIM6 model components.

We finally summarize the key findings in Chapter 6 and present some suggestions for future work in this area.

## Chapter 2

# Core Models for Multi-Gate MOSFETs in BSIM-CMG

Contemporary SPICE compact models for FET contain a physical core model that describes the electrostatics and transport of the channel carriers for an ideal long channel transistor. They fall under two varieties -

- Threshold voltage based model like that in industry standard bulk planar transistor model BSIM3/4. Threshold voltage,  $V_{th}$  (the gate voltage at the onset of inversion) is the primary unknown for a FET device in this model. The charge in the channel is explicitly expressed as a function of the terminal voltages and  $V_{th}$ .

- Charge/Surface Potential based model like that in MOS11, EKV, PSP, HiSIM etc. An analytic solution of Poisson equation under boundary conditions set by the device architecture and suitable approximations leads to an implicit equation of the charge/surface potential in the channel as a function of terminal voltage and other physical device parameters. This implicit equation is solved for to obtain the charge/surface potential in the channel.