# Scalable Model Checking Beyond Safety - A Communication Fabric Perspective

Sayak Ray

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-181 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-181.html

November 4, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Scalable Model Checking Beyond Safety A Communication Fabric Perspective

by

Sayak Ray

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Robert K. Brayton, Chair Professor Sanjit A. Seshia Professor Lauren K. Williams

Fall 2013

## Scalable Model Checking Beyond Safety A Communication Fabric Perspective

Copyright 2013 by Sayak Ray

#### Abstract

Scalable Model Checking Beyond Safety A Communication Fabric Perspective

by

Sayak Ray

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert K. Brayton, Chair

In this research, we have developed symbolic algorithms and their open-source implementations that effectively solve liveness verification problem for industrially relevant hardware systems. In principle, our tool-suite works on any sequential hardware circuit and for the whole family of  $\omega$ -regular properties. Practicality and effectiveness of our tool-suite have been demonstrated in the context of proving response properties (a very common and important liveness property) of on-chip communication fabrics.

To Maa

## **Contents**

| Co | Contents                                                                                                                         |    |

|----|----------------------------------------------------------------------------------------------------------------------------------|----|

| Li | st of Figures                                                                                                                    | iv |

| Li | st of Tables                                                                                                                     | vi |

| 1  | Introduction1.1 Motivation1.2 Contributions1.3 Organization                                                                      | 3  |

| 2  | Algorithmics for Liveness  2.1 Safety vs. Liveness                                                                               | 6  |

| 3  | Formal Model for Communication Fabrics  3.1 Executable Micro-Architecture Specification (xMAS)                                   | 17 |

| 4  | Bug Hunting for Liveness4.1 Introduction4.2 Preliminaries4.3 L2S Conversion for Stabilization Properties4.4 Experimental Results | 26 |

| 5  | Efficient Proof Of Liveness 5.1 Introduction                                                                                     | 34 |

| •  | ٠ | ٠  |

|----|---|----|

|    | ı | 1  |

| п. | ι | ı. |

|    | 5.5<br>5.6<br>5.7 | Approach II: Well-founded Induction | 44<br>55<br>66 |

|----|-------------------|-------------------------------------|----------------|

| 6  | Stru              | ctural Invariant Generation         | 80             |

|    | 6.1               | Introduction                        | 80             |

|    | 6.2               | Related Works                       | 82             |

|    | 6.3               | Preliminaries                       | 83             |

|    | 6.4               | Invariant Mining For xMAS fabrics   | 86             |

|    | 6.5               | Experimental Results                | 92             |

|    | 6.6               | Conclusion                          | 95             |

| 7  | Con               | clusion and Future Work             | 96             |

|    | 7.1               | Conclusion                          | 96             |

|    | <b>7</b> .2       | Future Work                         | 96             |

| Bi | Bibliography      |                                     |                |

## List of Figures

| 2.1        | Taxonomy of SCC analysis algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

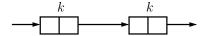

| 3.1 3.2    | xMAS symbols for structural components of communication fabrics A synchronous FIFO queue with a write port (on the left) and a read port (on the right). The queue can store $k$ data elements. In each clock cycle, if the queue is not full, a new element may be inserted; and if the queue is not empty, the oldest element may be removed. read_data exposes the oldest element if the queue is not empty. If the queue is empty, the incoming data appears at the output one cycle later. | 13<br>14 |

| 3.3        | cycle later                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14<br>14 |

| 3.4        | A succinct representation of two buffers connected back-to-back from Figure 3.3 .                                                                                                                                                                                                                                                                                                                                                                                                               | 15       |

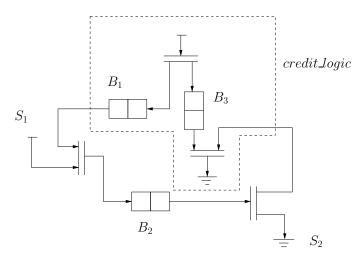

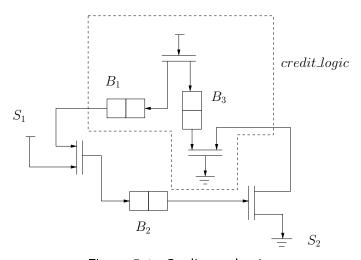

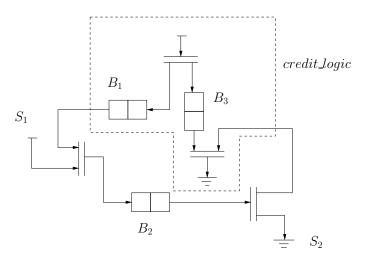

| 3.5        | Credit mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18       |

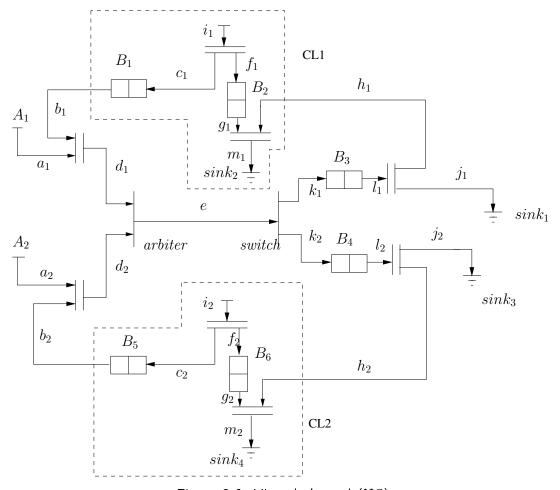

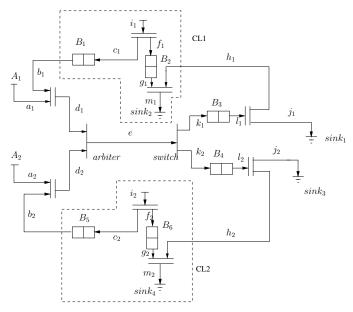

| 3.6        | Virtual channel (VC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19       |

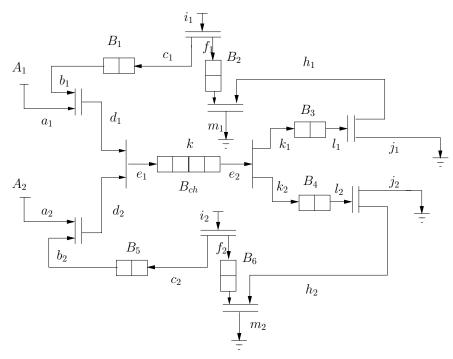

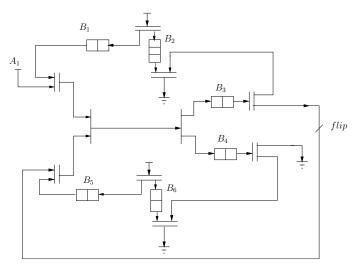

| 3.7<br>3.8 | Buffered virtual channel ( $\mathcal{VCB}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20<br>20 |

| 3.9        | A pair of agents communicating over a simple fabric ( $MS$ )                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21       |

| 3.10       | A two entry scoreboard (SB) $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22       |

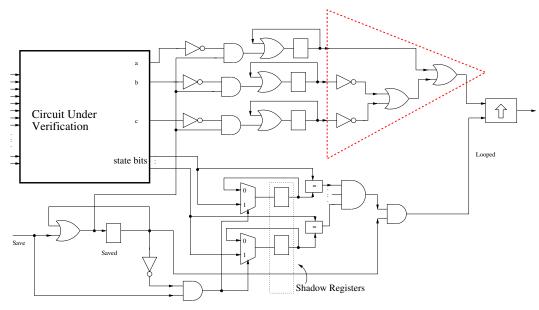

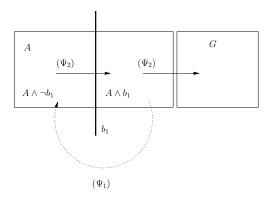

| 4.1        | Liveness-to-safety transformation for $Fp$                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29       |

| 4.2        | L2S for stabilization property $FGa \Rightarrow FGb + FGc \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                              | 31       |

| 5.1        | Credit mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35       |

| 5.2        | Virtual channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36       |

| 5.3        | A deadlocking virtual channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41       |

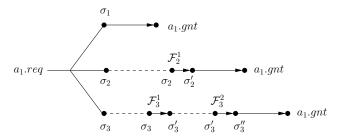

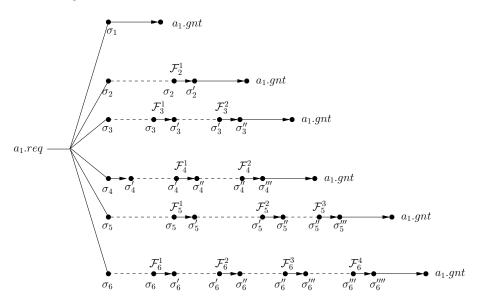

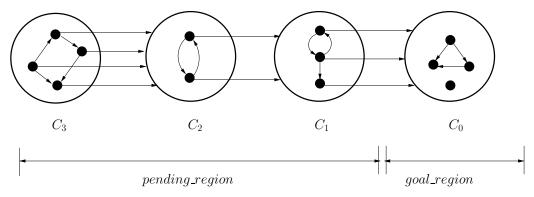

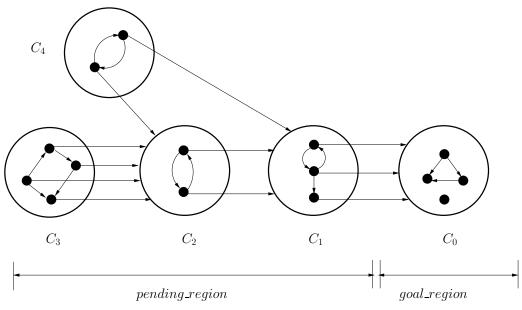

| 5.4<br>5.5 | Well-founded structure for virtual channel                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45<br>48 |

| 5.6        | A folded representation the same                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49       |

| 5.7        | Various configurations of $B_5$ (captured in predicates $\pi_1$ , $\pi_1$ , $\pi_2$ )                                                                                                                                                                                                                                                                                                                                                                                                           | 50       |

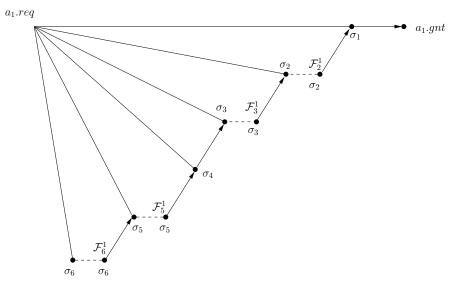

| 5.8        | Well-founded structure for Master/Slave design                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53       |

| 5.9        | Compositional structure for Master/Slave design                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54<br>58 |

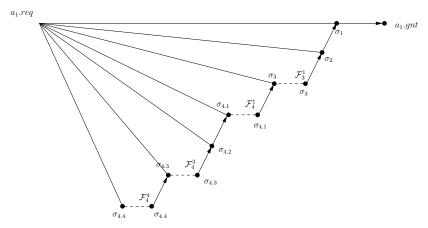

| 5 10       | Schomatic representation of a linearly graded needing graph                                                                                                                                                                                                                                                                                                                                                                                                                                     | าห       |

| 5.11 | Schematic representation of a topologically graded pending graph                     | 59 |

|------|--------------------------------------------------------------------------------------|----|

| 5.12 | Discovering linear gradation using Boolean signals                                   | 61 |

| 5.13 | Abstract state-space for virtual channel                                             | 64 |

| 5.14 | Abstract state-space (some transitions pruned) for virtual channel                   | 65 |

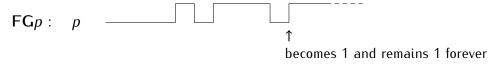

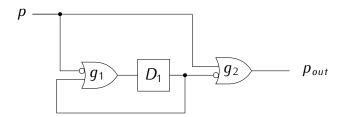

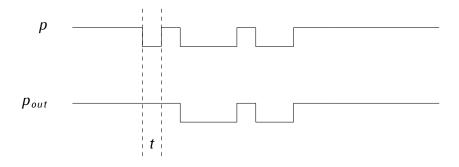

| 5.15 | A typical waveform for a signal $p$ that satisfies property $FGp$                    | 66 |

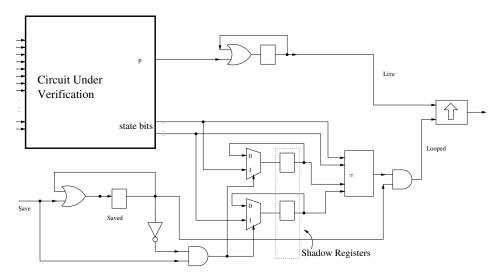

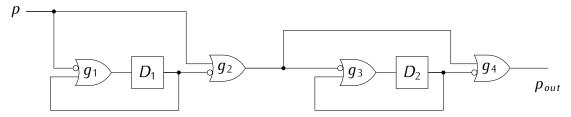

| 5.16 | Absorber Logic that absorbs one 'drop' on p                                          | 67 |

| 5.17 | A typical waveform for signal $p$ that enters the absorber logic of Figure 5.16 and  |    |

|      | the corresponding waveform for $p_{out}$                                             | 68 |

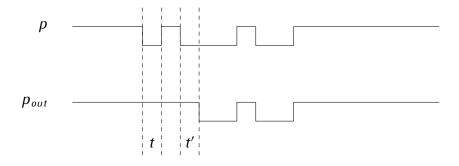

| 5.18 | Cascade of absorber logic for absorbing 2 'drops' on $p$                             | 68 |

| 5.19 | Waveform for $p$ and $p_{out}$ obtained from a two-level cascade of absorber circuit | 69 |

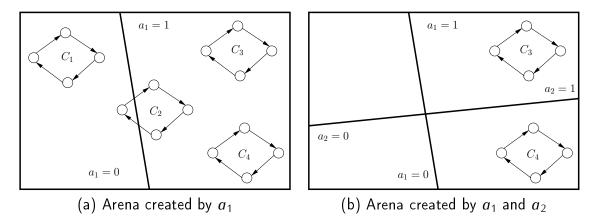

| 5.20 | Formation of arena with stabilizing constraints and their role in precluding un-     |    |

|      | reachable loops                                                                      | 70 |

| 6.1  | Credit mechanism                                                                     | 81 |

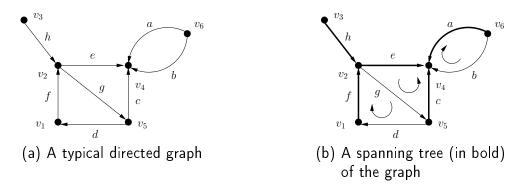

| 6.2  | A directed graph and one of its spanning tree                                        | 84 |

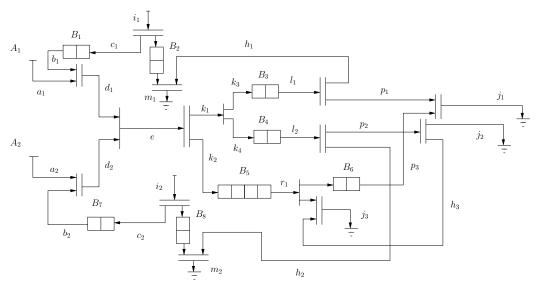

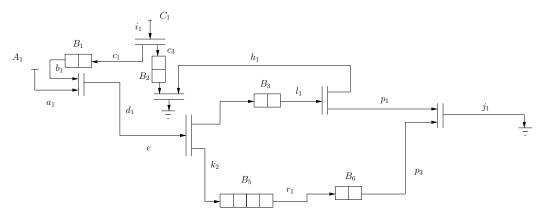

| 6.3  | VCO: A virtual channel with ordering                                                 | 88 |

| 6.4  | Sub-network that steers $type(A_1)$ -flit                                            | 88 |

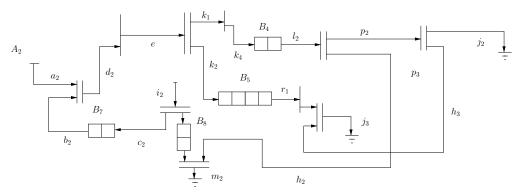

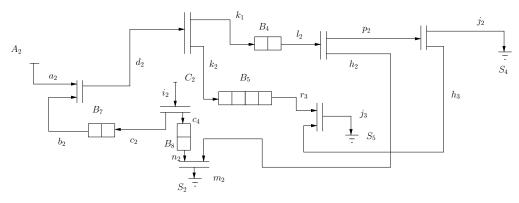

| 6.5  | Sub-network that steers $type(A_2)$ -flit                                            | 89 |

| 6.6  | Sub-network of Figure 6.4 simplified by 'shorting' arbiters and switches             | 89 |

| 6.7  | Sub-network of Figure 6.5 simplified by 'shorting' arbiters and switches             | 90 |

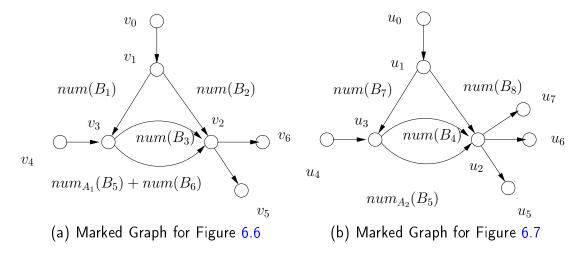

| 6.8  | Marked graphs for the sub-networks of $\mathcal{VCO}$                                | 91 |

|      |                                                                                      |    |

## List of Tables

| 4.1 | 220                                                                                                |    |

|-----|----------------------------------------------------------------------------------------------------|----|

| 4.2 | ve                                                                                                 |    |

| 4.3 | MS                                                                                                 | 32 |

| 5.1 | Auxiliary safety assertions                                                                        | 39 |

| 5.2 | Assumptions used in the proofs                                                                     | 42 |

| 5.3 | Experiment on various communication fabrics                                                        | 43 |

| 5.4 | Verification run-times for intermediate assertions on well-foundedness                             | 55 |

| 5.5 | Verification run-times for skeleton independent proof                                              | 65 |

| 5.6 | Liveness property verification run-time with liveness-to-safety transformation                     | 76 |

| 5.7 | Performance of k-LIVENESS with arena Violation                                                     | 77 |

| 5.8 | Performance of $k$ -LIVENESS without arenaViolation                                                | 77 |

| 6.1 | Correspondence between vertices of marked graph in Figure 6.8(a) and xMAS components of Figure 6.6 | 90 |

| 6.2 | Correspondence between vertices of marked graph in Figure 6.8(b) and xMAS components of Figure 6.7 | 90 |

| 6.3 | Edge identifiers for the marked graphs                                                             | 91 |

| 6.4 | Assumptions used in the proofs                                                                     | 93 |

| 6.5 | Experiment on various communication fabrics (1)                                                    | 94 |

| 6.6 | Experiment on various communication fabrics (2)                                                    | 94 |

## Acknowledgments

I thank Prof. Robert Brayton for advising me during my graduate study. His open and positive outlook has remained the principal guideline in my research. I hope this will continue to steer my way from now on. He will always remain a colossal figure of inspiration to me. Alan Mishchenko taught me the basic skills of research from the ground up. He showed me what it means to be passionate about research. He was my guide in almost every path that I explored in the past few years, be it an intricate research idea of AIG isomorphism or a fun hike in the Columbia River Gorge. I found him relentlessly enthusiastic whenever I approached him with a problem. I was fortunate to have Niklas Een, Baruch Sterin and Jiang Long as my colleagues in Bob's group. Working with them was an enriching experience. I thank to Mike Case for always responding to my queries and concerns.

Satrajit Chatterjee has deep influence in this dissertation. We had long hours of research discussions in Intel, and Satrajit made them productive and joyful with his own charisma. Some of the works presented in this dissertation began under his mentorship. I am indebted to him for being a caring mentor in my research projects and beyond. I thank Michael Kishinevsky for letting me and Satrajit work together under his watchful eyes. Timothy Kam, Qi Zhu, Emily Shriver, Umit Ogras, Murali Talupur and the full team of Strategic CAD Lab made my Intel internships fruitful and memorable during my formative years. I thank Prosenjit Chatterjee, Yogesh Mahajan and Vigyan Singhal for arranging another wonderful internship in Nvidia.

I thank Prof. Sanjit Seshia and Prof. Lauren Williams for being members of my dissertation committee. Prof. Seshia's comments and feedback on the initial draft of the dissertation were very helpful. I acknowledge Prof. Edward Lee for his feedback on my qualifier examination. I am deeply grateful to Prof. Koushik Sen and Prof. Jaijeet Roychowdhury for being my temporary advisers and funding my research efforts during the initial and final months of my study respectively. Stavros Tripakis was a great peer in the DOP Center with whom I had many stimulating research discussions. I gratefully acknowledge Prof. Christos Papadimitriou's support in the Fall 2010 semester. Shirley Salanio and Ruth Gjerde were tirelessly supportive in all of my graduate matters. This dissertation would not have been possible without this collaborative Cal community.

I thank Prof. P. P. Chakrabarti, Prof. Pallab Dasgupta and Prof. Dipankar Sarkar for motivating and preparing me for the graduate study. Without their inspiration and support, I could not have experienced the wonders of Berkeley. I sincerely acknowledge Prof. Goutam Biswas, Prof. Abhijit Das, Prof. Arijit Bishnu, Prof. Arobinda Gupta and Prof. Chandan Mazumdar for their encouragements.

I enjoyed few great years in the DOP Center with Mehdi Maasoumy, Susmit Jha, Rhishikesh Limaye, Daniel Holcomb, Wenchao Li, Dai Bui, Tobias Welp and Pierluigi Nuzzo. I had brief but quite memorable overlap with Xuening Sun, Shauki Elassaad, Aaron Hurst, Zile Wei, Shanna-Shaye Forbes, Bryan Brady, Alberto Puggelli, Antonio Iannopollo, Yen-Sheng Ho, Aaditya V. Karthik and Rohit Sinha. I thank James Cook, Anindya De, Kurt Miller and Siu

Man Chan for being my incredibly helpful GSI colleagues. My transition from India to United States would never have been a smooth one without Avishek Saha and Anirvan Duttagupta's help. I appreciate Partha Sarathi De, Arnab Sen, Subhroshekhar Ghosh, Koushik Pal, Sharmodeep Bhattacharya, Riddhipratim Basu, Sujayam Saha and Shubhankar Chaudhuri for creating a homely space around me that I left back in my home-town.

I thank the members of my family for their endless good wishes which have been instrumental to all my decisions and reflections. Their unconditional support during my times of difficulties can hardly be reciprocated.

## Chapter 1

## Introduction

This dissertation belongs to the broad area of formal methods for system design. Its overarching theme is to develop scalable algorithms and tools for liveness verification. Liveness is a type of formal specification used to specify certain behaviors of hardware and software systems. The other type, which is relatively simpler than liveness, is called *safety*. Safety properties specify that something bad will never happen. For example, the property of mutual exclusion, which specifies that two concurrent processes will never access a critical section simultaneously, is a safety property. Liveness properties, on the other hand, specify that something good will happen eventually. Scenarios like deadlock-freedom, livelock-freedom, stabilization etc. are modeled using liveness properties. In our research, we have developed various symbolic algorithms and their open-source implementations that are effective in solving liveness verification problems for industrially relevant hardware systems and outperform traditional algorithms. In principle, the tool-suite that we have developed in this thesis works on any sequential hardware circuit, and for the whole family of  $\omega$ -regular properties Thomas, 1990]. In particular, practicality and effectiveness of our tool-suite have been demonstrated in the context of proving response properties<sup>1</sup> of on-chip communication fabrics. This tool-suite consists of a proof engine and a bug-hunting engine. The proof engine extends the recent development of k-LIVENESS proposed by Claessen and Sörensson [Claessen and Sörensson, 2012]. The bug-finder is based on the liveness-to-safety conversion algorithm originally proposed by Biere et al. [Schuppan and Biere, 2004]. Following are the three main components of this dissertation:

**Proof Engine** The main thrust of our proof engine is scalability. In order to achieve this, we have deviated from the classic approaches like *nested fix-point formulation* or *strongly connected component enumeration* for reasoning about liveness, and resorted to a more scalable technique called *ranking oriented proof*. In general, automatically finding a ranking oriented proof is known to be a challenging task; there is no known mathematical theory for extracting ranking information from an arbitrary finite state machine

<sup>&</sup>lt;sup>1</sup>A response property is a common and important liveness property. See Section 5.3 for further details.

represented as a sequential circuit. To address this challenge, we devised a specialized constraint mining algorithm that discovers special kinds of Boolean relations from the target hardware. These relations can convey useful ranking information for various types of hardware of practical importance. In fact, these ranking constraints played an instrumental role in the scalability of our tool-suite for proving response properties of communication fabrics.

**Bug Finder** The core idea of k-LIVENESS is aimed at *proving* a liveness property, but it cannot disprove an incorrect property i.e. it cannot find a bug if one exists. Thus to complete our tool-suite, a separate bug-finder was developed. In principle, it can both prove or disprove a liveness property, but its underlying algorithm is more effective for finding bugs using bounded model checking or random simulation.

**Analysis of Invariants** In addition to advancing core techniques for liveness verification, this dissertation also emphasizes the impact of design invariants on scalable liveness verification. It is well-known that design invariants can be crucial ingredients for scalable safety verification. Because we leverage safety verification technology for liveness verification in our work, we demonstrate that the role of design invariants can be extended naturally to liveness verification. With the introduction of design invariants in our experiments, we achieve a speed-up in liveness verification for our target communication fabrics (see experimental results in Chapter 5). For these systems, Chatterjee and Kishinevsky presented an algorithm [Chatterjee and Kishinevsky, 2010a] that discovers a set of linear invariants automatically. These invariants were shown to be crucial for efficient safety verification. Our experiments show that these invariants are essential for efficient liveness verification as well. Additionally, we provide a novel and rigorous mathematical justification about the scope of the Chatterjee-Kishinevsky algorithm. We show that the classic notion of Kirchhoff's voltage law (more fundamentally, the nullspace analysis of the incidence matrix of a directed graph) offers a precise mathematical tool for mining this particular kind of invariants from communication fabrics.

## 1.1 Motivation

Theoretical foundations for safety and liveness verification (eg. theory of  $\omega$ -regular model checking) have been developed by researchers over the last four decades. Comprehensive books like [Clarke et al., 1999] and [Baier and Katoen, 2008] are available as authoritative expositions on this topic. Based on this rich body of foundational knowledge, significant effort is now being invested, both in academia and industry, in transforming this theory into useful software technology that engineers can use to solve their verification problems arising in industry. Safety verification, being the first hurdle in this direction, has received the lion's share of attention from researchers so far. As a result, today there exist extremely sophisticated symbolic algorithms for reachability analysis and their heavily engineered implementations

that can solve many industrially important safety verification problems. These were beyond the capacity of available technologies even five years ago. Liveness verification, being the second hurdle in this area, is yet to receive a comparable effort. This dissertation is a step in bridging this gap. It aims to leverage knowledge and techniques acquired from the many advances in safety verification and to develop successful technologies for liveness verification.

### 1.2 Contributions

This dissertation offers new capabilities of bit-level liveness verification in general and an in-depth formal analysis of communication fabrics with the objective of their scalable bit-level response verification. At the conceptual level, we make the following contributions:

Well-foundedness in Hardware Systems: We show that the operations of industrially relevant hardware systems (communication fabrics in our case studies) can naturally give rise to a well-founded ordering in their state spaces. We call such well-founded ordering a ranking structure. We show how we can use disjunctive stabilizing assertions to capture this ranking structure, and subsequently use them to speed up liveness verification. We propose an algorithm that discovers these stabilizing assertions automatically from the bit-level netlists. We demonstrate a few other heuristic techniques that can leverage these ranking structures implicitly to speed up liveness verification. These heuristic techniques improve on verification runtime at the expense of lesser automation.

Invariant Characterization: We provide an algebraic analysis of a set of industrially relevant communication fabrics. The analysis offers a rigorous mathematical justification of the Chatterjee-Kishinevsky invariants and their connection to the underlying network topology. Our analysis enhances our understanding about the Chatterjee-Kishinevsky invariants which are crucial for timely convergence of verification experiments on the target fabrics.

This dissertation involves significant experimental work. We have supported our conceptual claims and contributions with numerous experiments and benchmarking. Various prototypical tools have been developed and released as part of this research as described below:

Open Source Tool and Benchmark Development: Our proof and debug engines for liveness are developed in the ABC verification environment [Mishchenko, 2013]. ABC is an open-source hardware synthesis and verification tool that offers state-of-the-art safety verification capabilities. Mainly utilizing ABC's netlist manipulation functions and property directed reachability engine, we have developed our liveness verification engines which are now publicly available with the official distribution of ABC. The now available ABC

commands kcs, l2s and l3s correspond to our proof and debug engines. While command kcs offers the prototypical implementation of the k-LIVENESS algorithm extended with the notion of disjunctive stabilizing constraints, commands l2s and l3s offer two variants of liveness-to-safety conversion algorithm for stabilization properties. In order to perform verification experiments, we have developed our own implementation of component libraries for communication fabrics (see Chapter 3 for details). This includes Verilog implementation of libraries and a code generator for fabrics from high-level textual description of fabric connections. We have developed various benchmarks of industrially relevant, publicly available fabric designs using our framework. These benchmarks have been used extensively in all our experiments and are publicly available for further experimentation.

## 1.3 Organization

The remaining chapters of this dissertation are organized as follows:

#### Chapter 2, 3: Background Concepts

We recapitulate necessary background concepts in Chapter 2 and 3. Chapter 2 discusses the basics of model checking for *linear temporal logic* (LTL) properties and the traditional algorithms for solving the liveness verification problem. Chapter 3 discusses the xMAS framework xMAS (Executable Micro-Architecture Specification) is a high-level modeling framework suitable for design and formal analysis of communication fabrics. It was proposed by researchers at the Intel Strategic CAD Laboratory [Chatterjee *et al.*, 2010] and has gained popularity among practitioners in very short time. After describing the basic library primitives of xMAS, Chapter 3 discusses xMAS models for a collection of industrially relevant fabrics in detail. These models are used as benchmarks in our experiments.

#### Chapter 4: The Bug Finder

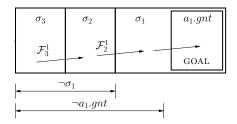

Our liveness-to-safety bug-hunting technique is described in Chapter 4. It first introduces stabilization properties, a syntactic subset of LTL which is semantically equivalent to the entire class of  $\omega$ -regular properties. Then it describes a simple construction for converting a stabilization verification problem into an equi-satisfiable safety verification problem. This construction enables bounded model checking and random simulation to be used for bug hunting for stabilization properties.

#### Chapter 5: Proof Techniques

Chapter 5 is devoted to *proof techniques* for liveness. While our main objective is to discuss our liveness proof engine that operates on the k-LIVENESS principle, we gradually build the

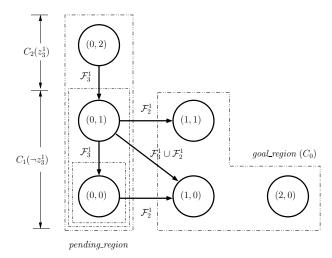

idea by illustrating how ranking structures are hidden in the state spaces of communication fabrics and how our techniques discover and leverage them. First we explain how the end-toend response property can be split into intermediate safety properties (Chapter 5.4). As proof obligations, these intermediate safety properties are easier than the end-to-end liveness one. This makes the scheme an attractive way to cope with the state explosion problem associated with liveness verification. However, this scheme requires significant manual intervention; a rigorous understanding of the design is required because there exists no automatic method for splitting an end-to-end liveness property into intermediate safety properties. Also, one needs to argue that satisfaction of the intermediate safety properties implies satisfaction of the liveness property. The nature of this argument is situation-specific and usually ad-hoc. One way of mitigating this issue is to use the notion of well-founded ordering. We demonstrate how this well-founded ordering information can be extracted from the design description of communication fabrics (Chapter 5.5). While the notion of well-founded ordering offers a systematic mathematical reasoning about liveness (contrary to the ad-hoc reasoning involved in the technique of intermediate safety properties), still the overall process is manual. In general, we do not know any algorithmic way of discovering a well-founded ordering from a design description. For our benchmarks, the ordering information is discovered manually. We increase the level of automation in the subsequent section (Chapter 5.6) by using a heuristic proof technique called skeleton independent proof proposed by Aaron Bradley et al. [Bradley et al., 2011]. Finally, we discuss our algorithmic proof technique based on k-LIVENESS at the end (Chapter 5.7). In principle, although it is a fully automatic algorithm, it can benefit from human quidance as well. A comparison among all these alternative techniques for proving liveness is discussed in detail in Chapter 5.

#### Chapter 6: Structural Invariant Generation

Our contribution to invariant generation for communication fabrics is discussed in Chapter 6. We summarize some necessary background on linear algebra and related works at the beginning of the chapter. Then we demonstrate how Kirchhoff's voltage law can be leveraged to generate invariants for communication fabrics.

#### Chapter 7 : Conclusion

Finally, Chapter 7 concludes the dissertation with a discussion on interesting possibilities of future investigations.

## Chapter 2

## Algorithmics for Liveness

## 2.1 Safety vs. Liveness

Safety and liveness are the main categories of temporal specification for reactive systems. Informally, safety properties specify that something 'bad' will never happen and liveness properties specify that something 'good' will happen eventually. The notions of safety and liveness was introduced first by Leslie Lamport in the 1970s in the context of the analysis of distributed systems [Lamport, 1980]. After this, numerous specification formalisms were proposed to capture these requirements in rigorous mathematical frameworks. These formalisms include *linear temporal logic* (LTL), *computation tree logic* (CTL),  $\omega$ -regular specification etc. In this dissertation, we adopt LTL for specification since it is the most widely used temporal logic and particularly appealing for liveness specification. We devote this chapter to outline syntax, semantics and model checking algorithms for LTL. Since an extensive literature is available on this topic, we focus only on the aspects that are most relevant to our work i.e. the algorithms for liveness verification.

The chapter is organized in two sections: Section 2.2 overviews the basics of LTL model checking and Section 2.3 discusses the taxonomy of the most prominent liveness verification algorithms.

## 2.2 LTL Model Checking

LTL is an extensively studied temporal logic and used widely for specifying behavior of reactive systems. LTL model checking is now an entry-level topic in formal methods with a plethora of literature available on specification and verification of LTL formulas. For completeness, we present a brief overview of syntax, semantics and basic model checking algorithm for LTL here. It is only a quick outline and does not attempt to reveal the full technical depth of the topic. We refer curious readers to comprehensive books like [Clarke *et al.*, 1999], [Baier and Katoen, 2008] for full details.

### 2.2.1 Syntax of LTL

Let AP be a set of atomic propositions and let  $p \in AP$  be some atomic proposition. LTL has the following syntax given in Backus-Naur form:

$$\phi := \top \mid \bot \mid p \mid \neg \phi \mid \phi \land \phi \mid X \phi \mid \phi \cup \phi$$

Here symbols  $\top$  and  $\bot$  stand for logical constants **true** and **false** respectively.  $\neg$  and  $\land$  are standard Boolean connectives denoting negation and conjunction respectively. X and U are temporal connectives that stand for **next** and **until** respectively. The above syntax is minimalistic in that it avoids many other (standard) Boolean and temporal connectives that can be expressed with the above connectives. For example, often we will use Boolean expressions  $\phi_1 \lor \phi_2$  (disjunction) and  $\phi_1 \Rightarrow \phi_2$  (implication) in place of  $\neg(\neg \phi_1 \land \neg \phi_2)$  and  $\neg \phi_1 \lor \phi_2$  respectively. Similarly, Fp and Gp are standard LTL expressions that are shorthands of  $\top Up$ , and  $\neg(\top U\neg p)$  respectively. F and G stand for **future** and **globally** respectively.

#### 2.2.2 Semantics of LTL

The semantics of LTL is defined over a formal model of transition systems called *Kripke structure*. A standard definition of Kripke Structure is given below:

**Definition 1** (Kripke Structure). A Kripke structure  $K = (S, S_0, R, L)$  is defined over a set of atomic propositions AP such that S is a set of states,  $S_0 \subseteq S$  is the set of initial states,  $R \subseteq S \times S$  is a *total* transition relation and  $L: S \to 2^{AP}$  is a labelling function.

A path  $\pi$  in a Kripke structure K is an infinite sequence of states  $s_0, s_1, s_2, \ldots$  such that  $(s_i, s_{i+1}) \in R$  for all possible  $i \geq 0$  and  $s_0 \in S_0$ . In our discussion, we consider only infinite paths in a Kripke structure unless stated otherwise. The i-th state on a path  $\pi$  is denoted as  $\pi(i)$ , for  $i \geq 0$  and the suffix sub-path of  $\pi$  that starts from  $\pi(i)$  is denoted as  $\pi^i$ . Using symbol  $\models$  to denote logical satisfaction relation, the semantics of LTL is defined as follows:

- $K, \pi \models p \Leftrightarrow p \in L(\pi^0)$

- $K, \pi \models \neg \phi \Leftrightarrow K, \pi \not\models \phi$

- K,  $\pi \models \phi_1 \land \phi_2 \Leftrightarrow K$ ,  $\pi \models \phi_1 \land K$ ,  $\pi \models \phi_2$

- K,  $\pi \models X\phi \Leftrightarrow K$ ,  $\pi^1 \models \phi$

- K,  $\pi \models \phi_1 \cup \phi_2 \Leftrightarrow$  there exists  $j \geq 0$  such that K,  $\pi^j \models \phi_2$  and K,  $\pi^i \models \phi_1$  for all i < j.

## 2.2.3 Model Checking Algorithm for LTL

We overview the basic LTL model checking algorithm based on *Büchi automaton* construction below. We first summarize the model checking algorithm, then recapitulate the notion of Büchi automaton.

### 2.2.3.1 The Basic LTL Model Checking Algorithm

Let K be a Kripke structure representation of some reactive system. Let  $\phi$  be an LTL formula over a set of atomic propositions AP that specifies all bad behaviors. We want to prove that  $K \models \neg \phi$  i.e. K does not admit any bad behavior specified by  $\phi$ . We build a Büchi automaton  $A_{\phi}$  that accepts all sequences over  $2^{AP}$  satisfying  $\phi$ . We then check whether  $\mathcal{L}(A_{\phi}) \cap \mathcal{L}(K) = \emptyset$  where  $\mathcal{L}(X)$  denotes the language accepted by automaton X. If  $\mathcal{L}(A_{\phi}) \cap \mathcal{L}(K) = \emptyset$ , then K satisfies  $\neg \phi$ ; otherwise we obtain a counterexample. Model checking of LTL is a PSPACE-complete problem in general. For details of the model checking procedure see [Clarke et al., 1999], [Vardi and Wolper, 1984].

#### 2.2.3.2 Büchi automaton

A Büchi automaton is a type of automaton on infinite strings and lies at the heart of LTL model checking. It has been studied extensively by automata theorists and logicians. Although in this dissertation we never construct a Büchi automaton explicitly, still it is an important background concept, particularly for Chapters 4 and 5. For completeness, we review the definition of a Büchi automaton and algorithm for its emptiness check. For further details see [Thomas, 1990]. Any LTL property can be translated into a Büchi automaton, but we omit details of this construction here and refer interested readers to [Kupferman and Vardi, 2005].

**Definition 2** (Büchi Automaton). A Büchi automaton is defined on an alphabet  $\Sigma$  as a quadruple  $\langle S, S_0, R, F \rangle$  where S is a (finite) set of states,  $S_0 \subseteq S$  is the set of initial state,  $R \subseteq S \times \Sigma \times S$  is a set of transitions (labeled with symbols from  $\Sigma$ ) and  $F \subseteq S$  is the set of accepting states.

Let  $\Sigma^{\omega}$  denote the set of all infinite strings of symbols from  $\Sigma$ . A Büchi automaton accepts strings from  $\Sigma^{\omega}$ . For a string  $a \in \Sigma^{\omega}$  where  $a = a_0, a_1, a_2, \ldots$  for  $a_i \in \Sigma$ , a run of a on a Büchi automaton  $B = \langle S, S_0, R, F \rangle$  is an infinite sequence of states  $\rho_a = s_0, s_1, s_2, \ldots$  such that all  $s_i \in S$ ,  $s_0 \in S_0$  and  $(s_i, a_i, s_{i+1}) \in R$  for all  $i \geq 0$ . Let  $Inf(\rho_a) \subseteq S$  denote the set of states in the run  $\rho_a$  that appear infinitely many times. Now, a run  $\rho_a$  is an accepting run if  $Inf(\rho_a) \cap F \neq \emptyset$ . A string  $a \in \Sigma^{\omega}$  is accepted by Büchi automaton B if it produces an accepting run. The set of all infinite strings accepted by B is called the *language* of B and is denoted by  $\mathcal{L}(B)$ .

## 2.2.4 Emptiness check of Büchi Automaton

The problem of emptiness check of a Büchi automaton is a fundamental concern in formal verification. It is not difficult to see that the product automaton  $A_{\phi} \times K$  is also a Büchi automaton and hence the model checking question for LTL i.e. if  $\mathcal{L}(A_{\phi}) \cap \mathcal{L}(K) = \emptyset$  reduces to the emptiness check of a Büchi automaton. Given a Büchi automaton  $B = \langle S, S_0, R, F \rangle$ ,  $\mathcal{L}(B)$  is empty if and only if B can not produce an infinite sequence of states obeying R starting from an initial state that visits at least one state in F infinitely often. Since the set of states S of B is finite, an infinite sequence of states that obeys R must form a lasso loop, a run of states that starts from an initial state and eventually enters and remains in a cycle of states. Moreover, if such an infinite sequence must visit at least one state in F infinitely many times, the loop part of the lasso loop must have at least one state in F. Therefore, a necessary and sufficient condition for  $\mathcal{L}(B) = \emptyset$  is that the underlying graph of B cannot have a cycle, reachable from an initial state, that contains a state in F. In other words, no reachable maximal strongly connected component (MSCC) of B can contain a state in F. An algorithm for finding strongly connected component (SCC) in a directed graph can, therefore, solve the emptiness checking problem of a Büchi automaton as well as the LTL model checking problem, at least in theory.

## 2.3 Algorithms for Liveness Verification

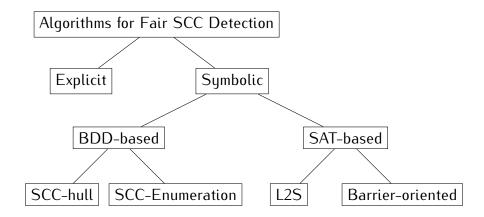

At the heart of any LTL liveness verification algorithm, there is a variant of SCC analysis routine. Over the last three decades, researchers came up with different techniques of SCC analysis to improve the scalability of LTL model checking. Early SCC analysis algorithms date back to Tarjan's work on depth first search and related linear-time graph traversal algorithms [Tarjan, 1972]. These algorithms, though have linear time-complexity, rely on explicit state traversal which makes them un-usable for model checking because explicit construction of graphs of transitions systems is infeasible in practice. Therefore, researchers proposed algorithms that perform state traversal implicitly a.k.a. symbolically. Thus there exist two broad categories of SCC analysis algorithms, explicit state traversal algorithms (i.e. the Tarjan-style classical algorithms) and symbolic state traversal algorithms. Because the explicit algorithms are rarely used for practical model checking, we omit further discussion about them and refer to algorithm text-books like [Cormen et al., 2009] for their description. Instead, we focus on the family of symbolic algorithms that are actively used for model checking in practice. The taxonomy of different SCC analysis algorithms is presented in Figure 2.1.

As shown in Figure 2.1, the class of symbolic algorithms is divided into *BDD-based algorithms* and *SAT-based algorithms*. *BDD* is the acronym for *binary decision diagram* [Bryant, 1992] – a data structure used for canonical representation of Boolean functions. *SAT*, on the other hand, stands for Boolean satisfiability solver [Eén and Sörensson, 2003].

Figure 2.1: Taxonomy of SCC analysis algorithms

Under BDD-based algorithms, there are *SCC hull-finding algorithms* and *SCC enumeration algorithms*. SAT-based algorithms are split into *liveness-to-safety conversion algorithms* (L2S) and *barrier-oriented algorithms*. Before describing them in detail, we make a remark on the nomenclature of the algorithms:

Remark 1. we use the terms 'BDD-based' and 'SAT-based' in order to emphasize the underlying verification technologies that are used with the corresponding algorithms. This attribute is not necessarily stringent because the algorithms that are designated as SAT-based can be solved with BDDs as well (if tractable). However, the formulations discussed under the BDD-based category are generally not SAT-solver friendly. A stronger distinguishing feature for these algorithms is the time period of their development. All algorithms discussed in the BDD-based category were developed in the late 1980s and the 1990s. SAT-based algorithms came after 2000 as SAT solvers began to outperform BDDs in solving large practical problems, thanks to successfully engineered SAT solvers like zCHAFF [Zhang and Malik, 2002] and MINISAT [Eén and Sörensson, 2003]. Liveness-to-safety conversion was proposed around 2002 mainly as a novel theoretical concept, without any special attachment to the use of SAT-solvers. Effective use of SAT-solvers with this formulation is an added plus. An alternative theme that may be identified among the SAT-based symbolic SCC analysis algorithms is 'looking at the liveness verification problem from a safety verification standpoint'. We expand more on this as we present the algorithms below.

## 2.3.1 BDD-based algorithms

BDD-based algorithms may be divided into two categories, viz. SCC hull-finding algorithms and SCC enumeration algorithms. Among the SCC hull-finding algorithms, the best-known is the Emerson-Lei algorithm [Emerson and Lei, 1986]. It works on the nested fixpoint formulation for finding MSCC hulls. Several variants have been proposed, for example see [Hojati

et al., 1993a], [Hojati et al., 1993b], [Kesten et al., 1998], [Hardin et al., 2001]. These variants achieve better speed-ups on certain types of state graphs. [Somenzi et al., 2002] provides a comprehensive comparison and a generalization of these ideas. [Xie and Beerel, 1999] proposed a BDD-based algorithm for explicit enumeration of the SCCs and improvements on this idea were proposed later in [Bloem et al., 2006]. However, these BDD-based algorithms, though elegant, do not scale in practice. [Ravi et al., 2000] provides a survey, and a comparative analysis of these algorithms.

## 2.3.2 SAT-based algorithms

As mentioned before, this family of algorithms works on formulations that are solvable by both BDD and SAT-solvers. But their ability of working with SAT-solvers makes them more attractive in practice. These algorithms have a deep connection to modern verification techniques for safety properties and their developments were inspired by the practical success of contemporary safety verification technologies. The liveness-to-safety conversion technique is such a method that converts a liveness problem into an equi-satisfiable safety problem [Schuppan and Biere, 2004]. This technique applies to LTL formulas as well as  $\omega$ -regular properties. This technique forms the core of our work on a BMC-based debugger for stabilization properties presented in Chapter 4. We defer an in-depth discussion of liveness-to-safety conversion until that chapter.

In the last few years, significant development has taken place in SAT-based algorithms for liveness verification. A liveness track was introduced in the hardware model checking competition and the top contending tools offered advanced SAT-based algorithms for liveness, the top two being IIMC and TIP. The algorithms behind these tools are known as FAIR [Bradley et al., 2011] and k-LIVENESS [Claessen and Sörensson, 2012] respectively. Algorithm FAIR introduced the idea of barriers in the context of symbolic SCC analysis. Barriers are inductive invariants that separate MSCCs of a directed graph. FAIR proves a liveness property by iteratively discovering barriers, thereby discovering SCC hulls in a symbolic and incremental way. Bradley et al. introduced a heuristic called skeleton independent proof in Bradley et al., 2011] which forms the foundation of Chapter 5.6 of this dissertation. k-LIVENESS, which was the winner in the liveness track of the recent-most hardware model checking competition [HWM, 2012] borrows the idea of barriers in a subtle way and offers a more scalable algorithm. This is the reason for putting these two algorithms together in the barrier-oriented category in (Figure 2.1). k-LIVENESS is the core of our Chapter 5.7. We will discuss these two algorithms in further detail in Chapter 5. In the particular context of liveness verification algorithms for communication fabrics, Holcomb et al. proposed a SAT-based algorithm for bounded liveness and performance analysis [Holcomb et al., 2012].

## Chapter 3

## Formal Model for Communication Fabrics

Communication fabrics are integral part of contemporary hardware systems. They are modules of logic that connect various computation units and I/O units within a large system and mediate data communication among them. The term 'communication fabric' encompasses a vast variety of logic whose generic responsibility is to transfer data from one point to another within a system. Enroute, it may change some data field(s) for the purpose of arbitration, scheduling, routing or other book-keeping, but involves no heavy computation. Examples of such logic range from local circuitry like a hardware scoreboard to system-wide circuit like a network-on-chip.

Design and analysis of communication fabrics have matured over decades of practice, but very little attention has been given to its formal modeling. Traditionally, there exist various formalisms like Petri nets [Murata, 1989] and data-flow networks [Arvind and Culler, 1986] for modeling communication-centric hardware systems, but they have witnessed only a modest adoption in the main-stream hardware industry. Recently, scientists from Intel's Strategic CAD Laboratory proposed a new formal model called Executable Micro-Architecture Specification, xMAS in short, which is particularly suitable for modeling communication fabrics and has promises for seamless adoption in the hardware engineering community [Chatterjee et al., 2010], [Chatterjee and Kishinevsky, 2010a], [Gotmanov et al., 2011]. It has a simple but rigorous formal semantics which makes it amenable to formal analysis and yet it is very close to the way the hardware engineers are trained to think. This is our choice of formal model for expressing and analyzing communication fabrics for their liveness properties. In this chapter, we present xMAS in detail. Readers already familiar with xMAS may skip this chapter, but a good understanding of the examples presented in Section 3.2 is necessary to grasp the subsequent chapters.

The chapter is organized as follows: we begin with a detailed discussion on the structural components of xMAS and their formal semantics (Section 3.1). We then illustrate a variety of example fabrics modeled in xMAS (Section 3.2). These examples are used as benchmarks in all our subsequent experiments. We conclude this chapter with Section 3.3 where we draw a critical comparison between xMAS and other prevailing formalisms like Petri nets

and data-flow networks.

## 3.1 Executable Micro-Architecture Specification (xMAS)

The core observation that Intel's researchers made while developing xMAS was that communication fabrics are essentially 'networks of finite FIFO buffers, with intervening glue logic'. In most of the cases, this glue logic can be described with a small number of characteristic primitives. xMAS is, therefore, simply described as a library of a small number of structural components <sup>1</sup> that includes **finite FIFO buffer**, **source** and **sink** of data items, synchronization primitives **fork** and **join**, **function**, **arbiter** and **switch**.

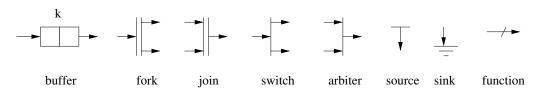

Each component of xMAS is defined as a synchronous Boolean circuit. FIFO buffer, source, sink and arbiter have sequential components while the rest are defined as combinational circuits. A communication fabric is constructed by stitching instances of different components together. A fabric thus constructed automatically becomes a synchronous, sequential Boolean circuit triggered by a single global clock. The timing model follows the synchronous model of time as in [Benveniste *et al.*, 2003]. For the ease of high-level modeling and informal exchange of designs, each component is represented with a visual symbol as shown in Figure 3.1. Logical definition of individual components are presented below. For further detail, see [Chatterjee *et al.*, 2010].

Figure 3.1: XMAS symbols for structural components of communication fabrics

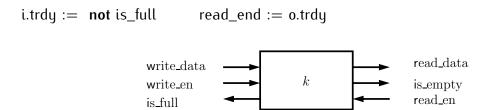

#### 3.1.1 FIFO buffer

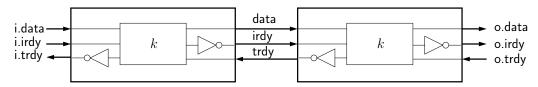

Consider a synchronous FIFO queue with a standard interface comprising a read port and a write port as shown in Figure 3.2. The queue has two parameters: size k (the number of elements it can contain) and a type  $\tau$  (the type of elements it can contain). To compose two instances of such a queue back-to-back without any extra glue logic, xMAS proposes slightly modified interface signals for each FIFO buffer as described below. Figure 3.3 shows composition of two FIFO buffers with such a modified interface definition.

<sup>&</sup>lt;sup>1</sup>we use terms *components*, *structural components* and *primitives* interchangeably in this dissertation

Figure 3.2: A synchronous FIFO queue with a write port (on the left) and a read port (on the right). The queue can store k data elements. In each clock cycle, if the queue is not full, a new element may be inserted; and if the queue is not empty, the oldest element may be removed. read\_data exposes the oldest element if the queue is not empty. If the queue is empty, the incoming data appears at the output one cycle later.

Figure 3.3: Back-to-back composition of two buffers with modified interface signals

#### 3.1.1.1 Channel

Note that input and output ports of FIFO buffers in Figure 3.3 comprises of three signals: data (a 'bit vector' signal), irdy (a single bit signal, for initiator ready) and trdy (another single bit signal, for target ready). This triplet of signals is called a channel. Channels are the only communication mechanism in the xMAS framework. A channel always connects two ports: an initiator, and a target. The data and irdy signals go from initiator to target and the trdy signal go from target to initiator. irdy indicates that the initiator is ready to send data and trdy indicates that the target is ready to accept data. Data are transferred exactly on those clock cycles when both irdy and trdy are true. Each channel has a type  $\tau$  which indicates the type of data it carries. Channels induce types on the ports they connect to. For example, both i and o ports of a queue have type  $\tau$  and this is denoted by i, o:  $\tau$ . In subsequent diagrams, we use only a single line to designate a channel which essentially encapsulates all the three signals associated with it. For example, Figure 3.4 is a simplified version of Figure 3.3 which captures all functional information about the system in a succinct way.

The labels k on the buffers in Figure 3.4 denote that the buffers are of size k. In the sequel, we will often drop this label from the diagrams when no ambiguity is ensued or when the buffer sizing information is not important for the context.

Figure 3.4: A succinct representation of two buffers connected back-to-back from Figure 3.3

#### 3.1.2 Sources and Sinks

A source is a primitive which is parameterized by a constant expression  $e:\alpha$ . At each cycle, it non-deterministically attempts to send a packet e through its output port. A source has a single output port  $o:\alpha$  and is governed by the following equations:

```

o.irdy := oracle or pre(o.irdy and not o.trdy)

o.data := e

```

where **pre** is the standard synchronous operator that returns the value of its argument in the previous cycle and the value 0 in the first cycle; and oracle is an unconstrained primary input that is used to model the non-determinism of the source in the synchronous model. o.irdy is persistent, i.e. once a source makes a value available on the channel, it preserves that value until a transfer.

A sink is a component which non-deterministically consumes a packet. It has one input port i and is characterized by the following equation:

```

i.trdy := oracle or pre(i.trdy and not i.irdy)

```

## 3.1.3 Synchronization

A fork is a primitive with one input port  $i:\alpha$  and two output ports  $a:\beta$  and  $b:\gamma$  parameterized by two functions  $f:\alpha\to\beta$ , and  $g:\alpha\to\gamma$ . Intuitively, a fork takes an input packet and creates a packet at each output. It coordinates the input and outputs so that a transfer only takes place when the input is ready to send and both the outputs are ready to receive. Formally,

```

a.irdy := i.irdy and b.trdy a.data := f(i.data)

b.irdy := i.irdy and a.trdy b.data := g(i.data)

i.trdy := a.trdy and b.trdy

```

A *join* is the dual of a fork. It has two input ports  $a:\alpha$  and  $b:\beta$  and one output port  $o:\gamma$ . It is parameterized by a single function  $h:\alpha\times\beta\to\gamma$ . Intuitively, a join takes two input packets (one at each input) and produces a single output packet. It coordinates the input and outputs so that a transfer only takes place when the inputs are ready to send and the output is ready to receive. Formally,

```

a.trdy := o.trdy and b.trdy

b.trdy := o.trdy and a.trdy

o.trdy := a.trdy and b.trdy o.data := h(a.data, b.data)

```

#### 3.1.4 Function

A function is an xMAS primitive that transforms data. It is parameterized by two types  $\alpha$  and  $\beta$  and a function  $f: \alpha \to \beta$ . It has an input port  $i: \alpha$  and an output port  $o: \beta$ . It is characterize by the following combinational equations:

```

o.irdy := i.irdy o.data := f(i.data)

i.trdy := o.trdy

```

## 3.1.5 Switching

A *switch* is a primitive to route packets in the network. It consists of one input port i and two output ports a and b, all of type  $\alpha$ . It is parameterized by a switching function  $s: \alpha \to Bool$ . Informally, the switch applies s to a packet x at its input, and if s(x) is true, it routes the packet to port a and otherwise it routes it to port b. Formally,

```

a.irdy := i.irdy and s(i.data) a.data := i.data

b.irdy := i.irdy and not s(t.data) b.data := i.data

i.trdy := (a.irdy and a.trdy) or (b.irdy and b.trdy)

```

#### 3.1.6 Arbitration

Arbitration is modeled by a *merge* primitive that selects one packet among multiple input ports and one output port. Requests for a shared resource are modeled by sending packets to a merge and a grant is modeled by the selected packet. A complete definition of a two-input merge that has two input ports  $a: \alpha$  and  $b: \alpha$  and one output  $o: \alpha$

```

o.irdy := a.irdy or b.irdy

o.data := a.data

a.trdy := u and o.trdy and a.irdy

b.trdy := not u and o.trdy and b.irdy

u := 1 if a.irdy and not b.irdy

0 if not a.irdy and b.irdy

not pre(u) if pre(o.irdy and o.trdy)

pre(u) otherwise

```

## 3.1.7 Persistence Property of xMAS Components

xMAS components are so defined that the associated channels hold a property called *persistence*. Informally, a signal is persistent means that once the signal is asserted by the

initiator agent, it remains asserted until it is properly served by the target agent. For any xMAS channel u, both its irdy and trdy signals are persistent. Persistence of these two signals of channel u is termed as forward persistence and backward persistence and denoted with FwdPersistence(u) and BwdPersistence(u) respectively. Formally, these two properties of channel u can be defined in LTL as follows:

FwdPersistence(

$$u$$

)  $\triangleq$   $G((u.irdy.\neg u.trdy) \Rightarrow Xu.irdy)$

BwdPersistence( $u$ )  $\triangleq$   $G((u.trdy.\neg u.irdy) \Rightarrow Xu.trdy)$

Persistence is an important property that every xMAS channel satisfies. It greatly simplifies behavior of xMAS fabrics, significantly limits potential deadlocks and allows for simpler definition of channel liveness. It helps in compositional analysis of fabric behaviors and their liveness analysis with intermediate safety properties.

### 3.2 Benchmarks

We illustrate how xMAS primitives are used to construct communication fabrics with the help of few examples. These examples are taken from industrially relevant applications and are used as benchmarks in our subsequent experiments. We discuss the following examples in order: credit logic, virtual channel, virtual channel with buffer, virtual channel with ordering, master/slave communication and hardware scoreboard.

## 3.2.1 Credit Logic

Credit-based flow-control is a popular technique of switch-level flow control, especially in wormhole routing systems. Figure 3.5 illustrates an xMAS implementation of the basic idea of credit-based flow-control mechanism where a source  $(S_1)$  wants to send flits  $^2$  to a sink  $(S_2)$  through a buffer  $(B_2)$ , and the flow of flits across  $B_2$  is controlled by the *credit\_logic* sub-circuit. Main purpose of *credit\_logic* is to allow only a restricted number of flits to enter the system which it is guarding (in this case, the buffer  $B_2$ ).

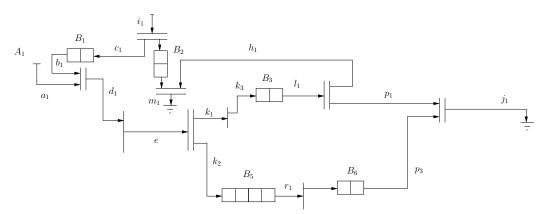

#### 3.2.2 Virtual Channel

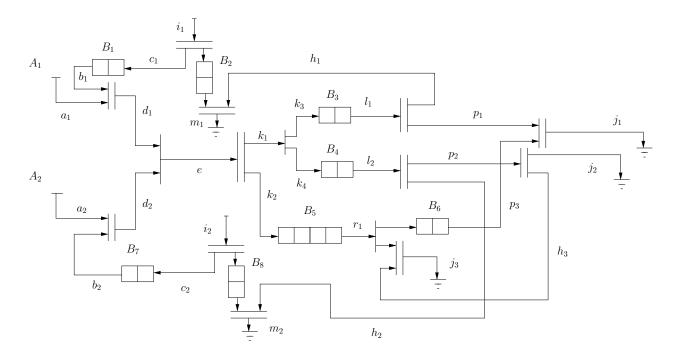

Consider the model shown in Figure 3.6. It is an implementation of *virtual channel* in xMAS. Here a single physical channel (channel e) is shared between two sources (sources  $A_1$  and  $A_2$ ). Virtual channel is a fundamental building block of on-chip communication networks which was invented to mitigate the head-of-line (HOL) blocking problem in wormhole switching. See texts like [Dally and Towles, 2003], [Duato  $et\ al.$ , 2002] for details. Figure 3.6 shows how two

$<sup>^2</sup>$ A flit (<u>fl</u>ow-control un<u>it</u>) is a unit of data transfer in communication fabrics, see [Dally and Towles, 2003] for details.

Figure 3.5: Credit mechanism

sources  $A_1$  and  $A_2$  share the virtual channel e to transfer flits to their respective sinks ( $sink_1$  and  $sink_3$  respectively) while credit logic blocks CL1 and CL2 control flow of flits from source  $A_1$  and  $A_2$  respectively. When source  $A_1$  wants to send a flit to  $sink_1$ , it makes a request on channel  $a_1$ . If buffer  $B_1$  has a token, this request is forwarded to channel  $d_1$ . Based on various conditions like whether channel  $d_2$  is also making a concurrent request or whether buffer  $B_3$  has an empty slot, the arbiter decides when to issue a grant against the request on channel  $d_2$ . This grant is transmitted to source  $A_1$  which allows  $A_1$  to complete the flit transmission. Similar steps take place when  $A_2$  wants to send a flit to  $sink_3$  and makes a request on channel  $a_2$ . We refer to the model of Figure 3.6 as  $\mathcal{VC}$  in the subsequent chapters.

#### 3.2.3 Virtual Channel with Buffer

In different applications, virtual channel needs to store flits temporarily before it forwards them to their respective destinations. This is implemented by putting a temporary buffer on the shared channel itself. An xMAS implementation is shown in Figure 3.7. We refer to this model as VCB. Structurally, it is same as VC with the only difference of the presence of buffer  $B_{ch}$  which splits channel e into two channels  $e_1$  and  $e_2$ .

#### 3.2.4 Virtual Channel with Order

Suppose we have the following ordering restriction on flits travelling in a virtual channel:

an  $A_1$ -flit can be sunk only if all  $A_2$ -flits that came before it on channel e have been sunk.

Figure 3.6: Virtual channel ( $\mathcal{VC}$ )

e is called an *ordering point*. Such one-way ordering restrictions are often needed to implement cache coherence protocols, or to guarantee producer-consumer ordering for software yet avoiding deadlock as would have been caused by total ordering. Figure 3.8 shows how this may be implemented using xMAS primitives. We call this model VCO. In this implementation, as shown in Figure 3.8, all buffers except  $B_5$  can hold two flits.  $B_5$  can hold four flits instead. Another speciality of  $B_5$  is that it can hold both  $type(A_1)$  and  $type(A_2)$ -flits, whereas each of the other buffers holds either  $type(A_1)$ , or  $type(A_2)$  flits, but not both. For further detail, see [Chatterjee  $et\ al.$ , 2010].

## 3.2.5 Master/Slave Communication

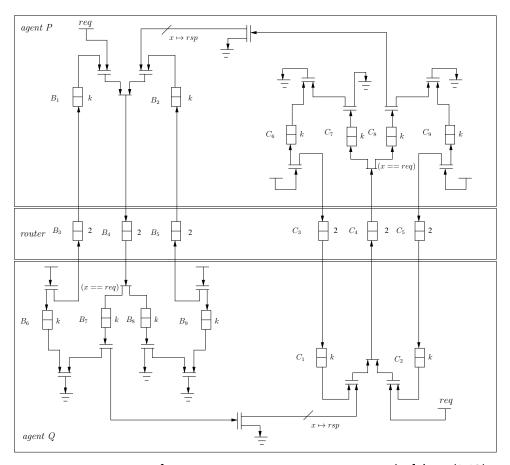

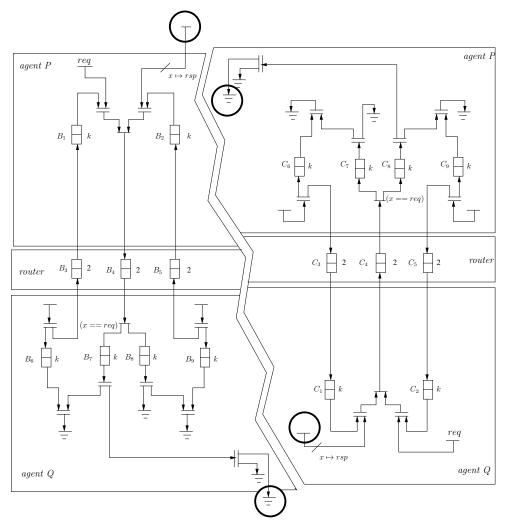

Figure 3.9 shows two agents P and Q communicating over a trivial fabric composed of six queues. Two types of flits are circulating in this fabric, viz. req (request type), and rsp

Figure 3.7: Buffered virtual channel (VCB)

Figure 3.8: Virtual channel with ordering (VCO)

(response type). Each agent creates new requests for the other agent. When an agent receives a request, it produces a response (by changing the packet type using a function  $x \mapsto rsp$ ) after a non-deterministic delay. The response is sent back to the original agent where it is sunk when the sink is ready to receive it. Thus each agent behaves like a master that produces requests, and responses, and a target that consumes responses, and requests. Communication between agents is done through the virtual channels. Consider agent P as example. It sends requests, and responses to agent Q through the shared channel, and the data transfer queue  $B_4$ , and then to two ingress queues  $B_7$ , and  $B_8$ , one per message type. An arbiter modeled by the merge primitive selects fairly between req and rsp messages that are exposed to arbitration only if they have credit tokens inside the corresponding credit queues  $B_1$ , and  $B_2$ . Credits are initialized inside the credit counters  $B_6$ , and  $B_9$  to the values equal to the sizes of the ingress queues  $B_7$ , and  $B_8$ , i.e. to k. Credits are returned through fabric credit queues  $B_3$ , and  $B_5$ . We call this model MS.

Figure 3.9: A pair of agents communicating over a simple fabric (MS)

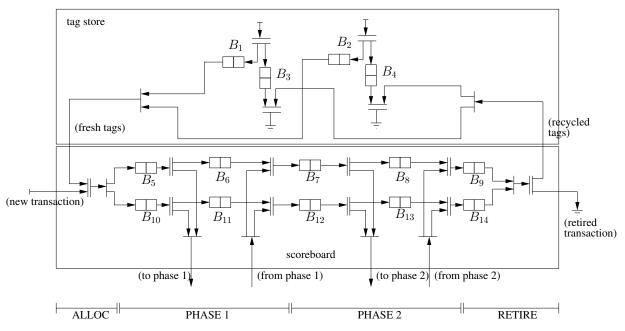

#### 3.2.6 Hardware Scoreboard

Figure 3.10 shows how a two-entry scoreboard may be modeled using the xMAS primitives. An incoming transaction on the left needs to obtain a tag before it can enter the scoreboard. Different tags are used to distinguish different in-flight transactions in the scoreboard. In this example, the scoreboard supports two simultaneous in-flight transactions, and hence there are two tag sources. These tag sources are modeled using credit logic. Once the transaction enters the scoreboard it competes with the other transaction (if there is one) to enter the first phase of processing. The results of this phase may return out of order: tags are used to match a result with the corresponding transaction in the scoreboard. Once the result of the first phase is returned, the transaction moves on to the second phase. After the second phase is done, the transaction becomes eligible for retirement. When it wins arbitration, it retires and releases its tag which is then recycled for use by a future transaction. For details, see [Chatterjee et al., 2010]. We call this model SB.

Figure 3.10: A two entry scoreboard (SB)

## 3.3 xMAS in Perspective

#### 3.3.1 From xMAS to bit-level netlist

As we mentioned before, an xMAS fabric is constructed by stitching various instances of the primitives together. This connection scheme can be represented textually, as well as

diagrammatically. Thanks to the precise logical semantics of the primitives, such a connection scheme can easily be translated into Verilog or VHDL or any other hardware description language (HDL) and from there, a bit-level netlist can easily be generated using any existing compiler. This quick-and-easy translation of a micro-architectural description into a bit-level netlist enables us to use state-of-the-art SAT solvers and bit-level verification tools for verifying architecture level properties. We have developed our own Verilog implementation of xMAS library closely following the semantics defined in [Chatterjee et al., 2010]. We have also developed a compiler that can read plain textual descriptions of connection schemes and generate Verilog descriptions. In our framework, we convert these Verilog descriptions into bit-level netlists by invoking our in-house tool veriABC. It uses Verific, a commercial Verilog front-end analyzer, for translation and elaboration into netlists. Finally, we use our bit-level verification tool ABC to perform verification experiments on them. This seamless integration of micro-architecture level modeling with the main-stream hardware verification flow is the major strength of xMAS formalism and this makes xMAS more attractive than some of the prevailing formalisms as discussed below.

### 3.3.2 Comparison with Petri nets

Petri net is an extensively studied model of computation, suitable for modeling and analysis of concurrent, and distributed systems, both in software and hardware. A huge volume of literature is available on this topic. [Murata, 1989] is an excellent introduction to Petri nets and their applications. Over the past few decades, different variations of the basic Petri net have been proposed and used in modeling various complex scenarios in hardware design. However, in spite of extensive study in academia, this formalism is hardly used in practice for developing large, complex systems. We may identify the following reasons for poor adoption of Petri nets in the industry:

- first, most hardware engineers feel comfortable thinking about a design in terms of the operational semantics of their choice of HDL Verilog or VHDL most of the time. Expressing a design in a different formal model like Petri net and then bit-blasting it often seem counter-productive to them.

- second, legacy designs and codes play a significant role in this mind-set. Design houses have huge repertoire of designs already coded in HDL's like Verilog or VHDL. It is practically impossible to re-model them in some other formalism that share little syntactic similarity with the HDL's.

- third, the most successful analysis tools for Petri nets are developed mainly for the simplest class of nets. For effective modeling of real-life hardware systems, we need more expressive families of Petri nets, like *colored Petri net*. Unfortunately, mathematical properties of these advanced families are rather weak, less studied and/or not

so well-known. There is not much of tool support and human expertise available for analysis of systems modeled in such advanced formalisms.

On the contrary, xMAS is a trivial syntactic extension over the basic HDLs that a hardware engineer is acquainted with. Adapting xMAS requires no extra learning, analysis or tool development.

#### 3.3.3 Comparison with Data-flow networks

Data-flow networks are widely used models of computation for design of embedded systems. However, they are not so popular in the main-stream hardware industry. While the design automation tools for data-flow networks meet the needs of embedded system designers, they hardly provide any extra benefit to the general-purpose hardware engineers. The most 'practically effective' data-flow models, viz. synchronous data-flow (SDF) [Lee and Messerschmitt, 1987] or cyclo-static data-flow (CSDF) [Bilsen et al., 1995], do not capture all the modeling needs for general-purpose hardware. Boolean data-flow (BDF) [Buck, 1993], which is capable of modeling Boolean conditions, switching, merging etc., is perhaps the most expressive variation of data-flow models that suites the purpose of general-purpose hardware design.

xMAS models do have syntactic similarities with BDF models, but there are several semantic differences that make BDF more expressive than xMAS. Some differences are outlined below:

- xMAS has finite memory, whereas in the standard dataflow models, queues are a-priori

unbounded. Some models like BDF can simulate Turing machines using this unbounded

memory capability. On the other hand, finite FIFOs can easily be simulated in dataflow

models by adding backward queues to control writing to a forward queue (so the number

of initial tokens in the backward queue represents and controls the size of the forward

queue).

- xMAS is a synchronous model, whereas dataflow models are asynchronous: each process proceeds at its own pace, and only needs to wait/synchronize with other processes when it needs to wait for data on input queues or when output queues are full (which is simulated by waiting for data on the backward queue). These synchronization features are also part of xMAS, but still the latter is a fundamentally synchronous model.

- xMAS has non-deterministic components (eg. sources, sinks) whereas in Kahn Process Networks and their subclasses like BDF, SDF, etc, processes are deterministic.

In spite of being more expressive than xMAS, however, BDF does not possess any particularly useful mathematical property that the other variations of data-flow models possess. For hardware communication fabric design, BDF's extra expressive power does not offer any extra benefit over xMAS. Analysis of hardware modeled as BDF rely on the same Boolean

techniques (like model checking) as xMAS models do. The latter, on the other hand, provides neat modeling primitives for finite FIFO networks compared to the cumbersome 'backward queue techniques' of BDF models. This offers xMAS a competitive advantage over BDF in practice. It might be interesting to perform a rigorous comparative analysis between Boolean data-flow and xMAS as models of computation, but we leave this discourse outside the scope of this dissertation.

# Chapter 4

# **Bug Hunting for Liveness**

#### 4.1 Introduction