## **Secure Virtualization with Formal Methods**

Cynthia Sturton

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-224 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-224.html

December 18, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Secure Virtualization with Formal Methods

by

Cynthia Koren Levine Sturton

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor David Wagner, Chair Associate Professor Sanjit A. Seshia Assistant Professor Brian Carver

Fall 2013

## Secure Virtualization with Formal Methods

Copyright 2013 by

Cynthia Koren Levine Sturton

#### Abstract

Secure Virtualization with Formal Methods

by

Cynthia Koren Levine Sturton

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor David Wagner, Chair

Virtualization software is increasingly a part of the infrastructure behind our online activities. Companies and institutions that produce online content are taking advantage of the "infrastructure as a service" cloud computing model to obtain cheap and reliable computing power. Cloud providers are able to provide this service by letting multiple client operating systems share a single physical machine, and they use virtualization technology to do that. The virtualization layer also provides isolation between guests, protecting each from unwanted access by the co-tenants. Beyond cloud computing, virtualization software has a variety of security-critical applications, including intrusion detection systems, malware analysis, and providing a secure execution environment in end-users' personal machines.

In this work, we investigate the verification of isolation properties for virtualization software. Large data structures, such as page tables and caches, are often used to keep track of emulated state and are central to providing correct isolation. We identify these large data structures as one of the biggest challenges in applying traditional formal methods to the verification of isolation properties in virtualization software.

We present a new semi-automatic procedure,  $S^2W$ , to tackle this challenge. Our approach uses a combination of abstraction and bounded model checking and allows for the verification of safety properties of large or unbounded arrays. The key new ideas are a set of heuristics for creating an abstract model and computing a bound on the reachability diameter of its state space. We evaluate this methodology using six case studies, including verification of the address translation logic in the Bochs x86 emulator, and verification of security properties of several hypervisor models. In all of our case studies, we show that our heuristics are effective: we are able to prove the safety property of interest in a reasonable amount of time (the longest verification takes 70 minutes to complete), and our abstraction-based model checking returns no spurious counter-examples.

One weakness of using model checking is that the verification result is only as good as the model; if the model does not accurately represent the system under consideration, properties proven true of the model may or may not be true of the system. We present a theoretical framework for describing how to validate a model against the corresponding source code, and an implementation of the framework using symbolic execution and satisfiability modulo theories (SMT) solving. We evaluate our procedure on a number of case studies, including the Bochs address translation logic, a component of the Berkeley Packet Filter, the TCAS suite, the FTP server from GNU Inetutils, and a component of the XMHF hypervisor. Our results show that even for small, well understood code bases, a hand-written model is likely to have errors. For example, in the model for the Bochs address translation logic – a small model of only 300 lines of code that was vigorously used and tested as part of our work on  $S^2W$ — our model validation engine found seven errors, none of which affected the results of the earlier effort.

To my husband, with love and gratitude.

# Contents

| Contents       |                                                                                                                                                                                 |                                      |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|

| $\mathbf{Li}$  | st of Figures                                                                                                                                                                   | iii                                  |  |  |  |

| List of Tables |                                                                                                                                                                                 |                                      |  |  |  |

| 1              | Introduction                                                                                                                                                                    | 1                                    |  |  |  |

| 2              | Background 2.1 Virtualization Software                                                                                                                                          | . 8                                  |  |  |  |

| 3              | Verifying Large Data Structures using Small and Short Worlds3.1 Running Example3.2 Formal Description of the Problem3.3 Methodology3.4 Evaluation3.5 Related Work3.6 Conclusion | . 19<br>. 22<br>. 28<br>. 38         |  |  |  |

| 4              | Model Validation  4.1 Running Example                                                                                                                                           | . 43<br>. 50<br>. 55<br>. 59<br>. 66 |  |  |  |

| 5              | Conclusion                                                                                                                                                                      | 68                                   |  |  |  |

| Bi             | Bibliography 69                                                                                                                                                                 |                                      |  |  |  |

# List of Figures

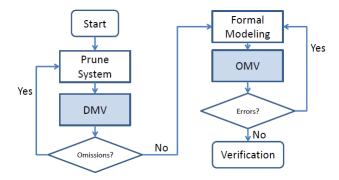

| 2.1 | An overview of the model checking work flow           |

|-----|-------------------------------------------------------|

| 3.1 | An illustration of memory with a simple cache         |

| 3.2 | The UCLID expression syntax                           |

| 3.3 | An illustration of a page table walk                  |

| 3.4 | An illustration of memory with a CAM-based cache      |

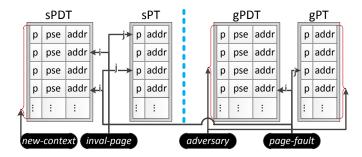

| 3.5 | An illustration of shadow page tables                 |

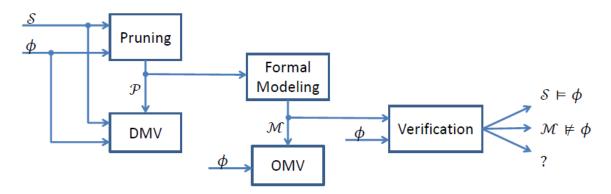

| 4.1 | An overview of the model validation work flow         |

| 4.2 | Example code and corresponding model                  |

| 4.3 | The five steps in our model validation process        |

| 4.4 | Example code with a dynamically determined loop bound |

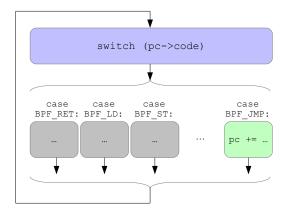

| 4.5 | Simplified code from the BPF program                  |

| 4.6 | An illustration of the BPF program                    |

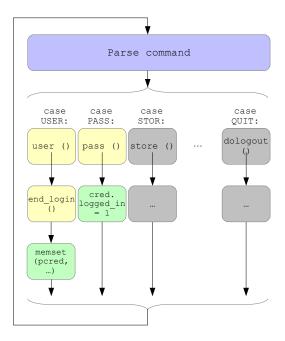

| 4.7 | Simplified code from the ftpd software                |

| 4.8 | An illustration of the ftpd program                   |

| 4.9 | Simplified code from the XMHF software                |

# List of Tables

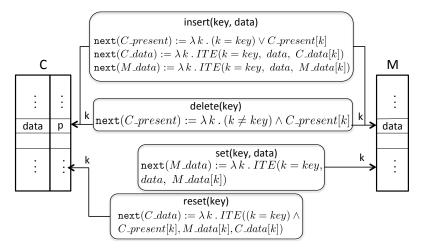

| 3.1 | The model of the Bochs TLB                         | 30 |

|-----|----------------------------------------------------|----|

| 3.2 | Next-state assignments for the shadow paging model | 35 |

| 4.1 | Bochs modeling bugs (6 of 7)                       | 62 |

| 4.2 | Code and path coverage for model validation.       | 65 |

| 4.3 | Types of modeling bugs found                       | 65 |

#### Acknowledgments

I thank my advisor, David Wagner, for his support and guidance throughout my graduate studies. His keen insights and deep understanding of all things security strengthened my research, and I learned a tremendous amount from working with him. I am also grateful to him for helping me to develop collaborations with folks outside of Berkeley's computer science division. They have been integral to my growth and development as a researcher. Any success I have had is due in large part to those collaborations.

I thank my committee members, Brian Carver and Sanjit Seshia, and my collaborators on the work appearing in this thesis: Rohit Sinha, Michael McCoyd, Sakshi Jain, Thurston Dang, and Petros Maniatis. I would especially like to thank Sanjit. Through collaborations with him on this and other work, I have learned to appreciate the power, and limitations, of using formal verification in a security context. His encouragement and advice throughout the years has made him a valuable mentor and greatly enriched my graduate school experience.

Although our work together is not a part of this thesis, I would like to thank Sam King and Matthew Hicks for fun, and fruitful, collaborations over the years. I am particularly grateful to Sam for his interest in, and encouragement of my studies and future career.

I am grateful to Colleen Lewis for her friendship. We have spent hours together laughing, stressing, and working, and it has all made for a wonderful graduate school experience.

I am grateful to my family for their ongoing love and encouragement. And I am deeply grateful to my husband. He has supported me with love, kindness, generosity, and delicious food throughout the long and circuitous path that led to this point.

# Chapter 1

# Introduction

Virtualization software, such as CPU emulators, virtual machine monitors (VMM), or hypervisors (HV), provides many practical benefits. It typically sits below the operating system and adds a layer of indirection between the operating system and the hardware platform. This is useful for a variety of applications. It can be used to present an instruction set architecture different than that of the actual hardware platform, which is useful for the development of operating systems and applications for new platforms. It can be used to multiplex hardware resources to allow multiple operating systems to co-exist on one platform. And it provides a vantage point below the operating system for more complete monitoring and analysis of the system, which is useful in the development and testing of new operating systems, and for malware analysis.

Virtualization is useful; however, virtualization software is typically complex and executes with high privilege levels, making it especially vulnerable to attack. In this work, we seek to verify the correctness of security-critical components of virtualization software. We investigate the use of formal verification techniques to prove properties about the security of system virtualization software in order to increase the overall security of the systems that rely on it.

Virtualization software is well known for its role in cloud computing, and in particular for infrastructure-as-a-service (IaaS) style cloud computing. With IaaS, the cloud provider maintains a large data center with many servers and rents out compute time to its customers. A customer can execute their entire software stack for as long as necessary on one of the provider's servers, and they pay only for the compute time they use. IaaS services allow customers to grow and shrink their infrastructure on demand. For example, an online shopping site can increase their capacity to handle high demand during peak shopping times without the overhead of purchasing, configuring, and maintaining new hardware. During off-peak hours, the customer can easily reduce their capacity and their costs. Customers of IaaS include well known online shopping sites, news media organizations, universities, and social media sites. IaaS style cloud computing is the fastest growing segment of the cloud

computing market and is expected to reach \$9 billion in 2013, up from \$6.1 billion in 2012 [1].

Cloud providers are able to take advantage of economies of scale to provide cheap compute capacity by using virtualization software. Hypervisors and virtual machine monitors allow multiple operating systems to execute on a single hardware platform, and give each guest operating system the illusion that it is running alone on the hardware. Since the different guest operating systems may belong to different customers, possibly even adversarial customers, customers and cloud providers rely on virtualization software to maintain strict isolation between guest OSes. In addition to providing a multiplexed hardware platform, virtualization software enables other tools that make data centers efficient and practical for cloud providers. For example, live migration of running operating systems allow for efficient resource allocation [2], and verifiable accounting of resource use allows for efficient billing [3].

Beyond cloud computing, researchers have proposed using system virtualization software as a platform to increase the security of end-user machines [4,5]. The isolation properties provided by hypervisors and virtual machine monitors can be used to implement red—green configurations on client desktops [6–9]. A red-green system allows the user to maintain a separation between their trusted and untrusted activities. One guest OS, the "green" one, is locked-down, trusted, has access to private data and a secure network, but has little access to the public Internet. A second, "red" guest OS has full access to the Internet, but not the secure network or private data.

Because the virtualization software sits beneath the OS layer in the system stack, it is well situated for OS introspection: it has a complete view of OS activity, and it protects itself from access by any code executing within the guest. A wide variety of malware detection and analysis systems based on virtual machine monitors, hypervisors, and emulators have been developed to take advantage of this property. Intrusion Detection Systems (IDS) usually have to choose between existing as a kernel module in the end system or sitting in the network, entirely outside the system. In the former case, the IDS has a complete view of the system, but it exists inside the system and so is vulnerable to attack from the very malware it aims to detect, rendering the IDS ineffective. In the latter case the IDS is inaccessible to the end system and therefore is protected from compromise, but it has an incomplete view of an end system's activity. With virtualization software, the IDS can exist in the virtualization layer below the OS. In this layer it has a complete view of the system it aims to protect, but is kept isolated and unreachable by the potentially compromised OS [10,11]. This property makes virtualization software especially powerful for the detection of rootkits [12–14], which traditionally have controlled the lowest level of software, making them difficult to detect from within the infected OS.

Its powerful vantage point also makes virtualization software useful for malware analysis [15–23]. Malware can be allowed to run in the guest OS, while its behavior is inspected by the virtualization software. The virtualization software protects itself from any activity in the guest OS, preventing the malware from shutting down the analysis. Similar techniques have also been shown to be useful for auditing and debugging operating systems [24, 25]. In

addition to detection and analysis, virtualization software has also been used to prevent compromise of the guest OS by preventing any unauthorized code from executing while the guest is in kernel mode [26–32].

Rather than focus on protecting the guest operating system from infection, a number of researchers have taken the view that it is better not to trust the OS at all, and tools based on hypervisors, emulators and virtual machine monitors have been developed to protect user-level code and data from a malicious OS [33–36]. There has even been work done on using nested virtualization to increase the security of the hypervisor or virtual machine monitor itself [37,38].

In all of these systems, the strength of the tool depends on the strong isolation and containment properties provided by the virtualization software. Because it sits below the operating system, and because it tends to have a considerably smaller code base than a commodity operating system, some researchers have suggested that virtualization software makes an ideal platform for building secure systems [4]. However, virtualization software is not necessarily immune from vulnerabilities. Although smaller than an operating system, the implementation of virtualization software can still be quite large. The popular Xen hypervisor is roughly 150 KLOC [39], and the KVM kernel module is roughly 42 KLOC. The code is complex and previous research has found errors in popular virtualization software [40,41]. Vulnerabilities that allow a guest to access the host's memory space have also been discovered [42–45].

The goal of this work is to prove the correctness of the isolation and containment properties that are fundamental to the security of so many tools and systems based on virtualization software. To do this, we focus on virtualization software's management of memory resources. The memory management components are responsible for providing to the guest the correct virtual-to-physical memory translation, which is usually provided by hardware. They must also provide the correct mapping from a guest operating system's view of physical memory to the machine's physical memory. The memory management code typically includes sets of page tables and caches. Proving safety properties about these large data structures presents a challenge to formal verification techniques. In this work, we focus on the verification of existing systems, rather than the development of a new hypervisor or emulator, and we use model checking to perform the verification.

In the first half of this thesis (Chapter 3), we consider the verification of safety properties in systems with large arrays and data structures, such as address-translation tables and other caches. These large data structures make automated verification based on straightforward state-space exploration infeasible. We present  $S^2W$ , a new abstraction-based model-checking methodology to facilitate automated verification of such systems. As a first step, inductive invariant checking is performed. If that fails, we compute an abstraction of the original system by precisely modeling only a subset of state variables. This subset of the state constitutes a "small world" hypothesis, and is extracted from the property. Finally, we verify the safety property on the abstract model using bounded model checking. We ensure

<sup>&</sup>lt;sup>1</sup>Generated using David A. Wheeler's 'SLOCCount' http://sourceforge.net/projects/sloccount/.

the verification is sound by first computing a bound on the reachability diameter of the abstract model. For this computation, we developed a set of heuristics that we term the "short world" approach. We present several case studies, including verification of the address translation logic in the Bochs x86 emulator, and verification of security properties of several hypervisor models. Through our case studies we demonstrate that with our approach, model checking can be successfully applied to large table-like data structures; this removes one key barrier to automated verification of system virtualization software. The material in this chapter is based on joint work with R. Sinha, P. Maniatis, S. A. Seshia, and D. Wagner [46].

One limitation of this approach is that the verification is done on a model and not on the code directly. As a consequence, the result of verification is only as valid as the model; if the model does not accurately capture the behavior of the system, a property proven true of the model may or may not be true of the actual system. Therefore, it is essential to validate the model against the source code from which it is constructed. In the second half of this thesis (Chapter 4), we present a framework for validating the manually-built model against the code. The framework consists of two components. The first, data-centric model validation, checks that, for data structures relevant to the property being verified, all operations that update these data structures are captured in the model. The second, operation-centric model validation, checks that each operation is correctly simulated by the model. Both components are based on a combination of symbolic execution and satisfiability modulo theories (SMT) solving. We demonstrate the application of our methods on several case studies, including the model of the address translation logic in the Bochs x86 emulator that we verify in Chapter 3, the Berkeley Packet Filter, a TCAS benchmark suite, the FTP server from GNU Inetutils, and a component of the XMHF hypervisor. This demonstrates that it is possible to validate the model against the code and gain increased confidence that modeling errors have not affected our ability to find bugs in the code – making formal verification of system virtualization software all the more compelling. The material presented in this chapter is based on work done jointly with R. Sinha, T. H. Y. Dang, S. Jain, M. McCoyd, T. W. Yang, P. Maniatis, S. A. Seshia, and D. Wagner [47].

In summary, the thesis of this work is:

Abstraction-based model checking techniques enable verification of large, symmetric data structures in software. In addition, the results of model checking can be strengthened through model validation techniques based on symbolic execution and SMT solving. These two results combine to provide an automated or semi-automated program verification technique suitable for proving security-critical isolation properties in virtualization systems.

We expect our results may have applications beyond the security of system virtualization software. Our work on  $S^2W$  is applicable to any system with large, table-driven data structures and gives us a new tool for dealing with the state space explosion problem in that

setting. And, model validation is a fundamental issue for all users of formal verification; our techniques may be broadly applicable to many applications of formal methods.

# Chapter 2

# Background

#### 2.1 Virtualization Software

Virtualization software is a thin layer that sits below an operating system. It presents a virtualized hardware interface to the operating system above, introducing a level of indirection for the hardware–software interface. This intermediate layer can be used for many purposes: It can multiplex hardware resources, allowing multiple operating systems to run on a single platform. It can present to the operating system an instruction set architecture (ISA) that is different from the actual hardware ISA, allowing an OS and software compiled for one platform to be run on a different platform. And, this intermediate layer can provide an isolated execution environment in which it mediates all accesses to physical system resources. CPU emulators, virtual machine monitors (VMM), and hypervisors (HV) are all examples of virtualization software, and in this work we use "virtualization software" to refer to any of these software systems.

## Virtual Machine Monitors and Hypervisors

Popek and Goldberg first formalized the definition of a VMM in 1974 [48]. They define a virtual machine (VM) as "an efficient, isolated duplicate of the real machine," and a VMM as the software that provides the VM environment. The VM is not any particular piece of software, rather it is the operating environment within which operating systems and applications may run. For example, the VM will include a virtual processor. To any software running in the VM, this processor will behave like a physical CPU. In reality, the virtual processor is a combination of the VMM software and the physical CPU hardware. Most instructions executed on the virtual processor are likely executed directly on the underlying physical CPU, but some are emulated by the VMM. The VMM can take advantage of the trapping mechanism provided by the physical CPU in order to intervene and emulate some

instructions when needed. All of this is done in a way that is transparent to software executing in the VM; the software executes on the virtual processor without being aware that it is virtual, and actually comprises both hardware and software.

Popek and Goldberg prescribe three properties that a VMM must provide: equivalence, resource control, and efficiency. Software running in the VM must produce the same effect as it would if it ran directly on the hardware, and not in the virtualized environment. The VMM must have control over hardware resources: the VM should not be able to access resources that have not been allocated to it and the VMM should be able to regain control of any resource already allocated to a VM. Software running in the VM environment must run efficiently. More specifically, a majority of the instructions executed must run directly on hardware without the intervention of the VMM. This last requirement differentiates VMMs from CPU emulators.

VMMs can be classified into two types [49]. A Type I VMM runs directly on the hardware platform without an underlying operating system. It has the highest level of privilege on the machine. Type II VMMs run on top of the host operating system, rather than on the bare metal. In both cases, the guest operating systems run in a layer above the VMM. Originally, "hypervisor" was another name for a Type I VMM. However, the lines between Type I and Type II VMMs are easily blurred and today the terms "hypervisor" and "VMM" are often used interchangeably, regardless of type. Some examples of well-known VMMs include VMware [50], Xen [51], KVM [52], and VirtualBox [53].

#### CPU Emulators

A CPU emulator is software that allows code compiled for one hardware platform to run on a different platform. For example, an application compiled for the PowerPC processor could be run on an x86 processor with the help of a CPU emulator. Emulators are not limited to use by applications; an entire operating system compiled for one architecture may be run on a different architecture with the help of a CPU emulator.

At its heart, an emulator works by translating the instructions of the guest binary code from the target (emulated) architecture to that of the host architecture. One way to manage the translation is by interpreting each instruction as it comes up. In this case, all CPU state, flags and control registers are implemented as variables in the emulation software and each instruction is implemented as a software function. Bochs is an example of a CPU emulator that uses interpretation [54]. A second type of translation works by recompiling the target binary code to the host architecture; recompilation is usually done one basic block of code at a time. QEMU is an example of a CPU emulator that uses recompilation [55].

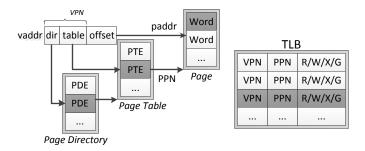

Virtual machine monitors, hypervisors, and CPU emulators all work slightly differently, but they have in common the need to manage the often complex virtualization of system resources. In this work, we focus on memory and how virtualization software manages the mapping from a guest operating system's view of memory to the machine's physical memory. The correct management of physical memory is key to providing the isolation between guest operating systems, or between the guest operating system and the host's execution that the virtualization software is often trusted to do. Virtualizing memory typically involves managing both page tables for address translation and caches of previously translated addresses. For example, Bochs will allow the OS to set up page tables with up to four levels of indirection, and it uses a translation lookaside buffer (TLB) with 1024 entries, each 160 bits wide, to cache previously translated addresses. It is the verification of these large data structures that we focus on in this work.

## 2.2 Model Checking

Throughout this work we use model checking-based techniques for our program verification. Model checking is a mature area of research, and there exist many variants. However, all model checking techniques have in common an approach to verification based on an exploration of the program's state space. A benefit of this approach is that if a property is disproven, the model checking engine can usually provide a counter-example showing the state, or series of states, that led to the failure.

Model checking was first introduced in the early 1980's [56–59] as a method for program verification that could be mostly automated. The original model checking algorithm is a graph-theoretic approach to program verification. The core idea is to represent the program to be verified as a directed graph, with nodes representing program states and edges representing transitions between states. Using a temporal logic such as Linear Temporal Logic [60] or Computational Tree Logic [56], properties about the program can be stated as properties about a path through the graph, or as properties about a sub-tree of the graph rooted at a particular node. Efficient graph exploration algorithms can then be used to prove or disprove the property.

While these early model checking algorithms can efficiently explore the state graph of a system, problems still arise for systems with large state spaces. The state space of a program is roughly exponential in the number of state variables. In software systems especially, the size and number of state variables can be large in the presence of large data structures. This "state space explosion" tends to limit the usefulness of so-called explicit state model checking, and various techniques have been developed to overcome it. One optimization is symbolic model checking. Rather than reasoning about individual states and transitions, symbolic model checking operates over sets of states and transitions. The sets, represented by Boolean formulas, represent the state space of the program symbolically. One way to store the Boolean formulas is as a Binary Decision Diagram (BDD). A BDD is a directed, acyclic graph that can efficiently represent many states; it is essentially a finite state automaton that takes as input a system state, represented as a sequence of binary digits, and accepts only those states that are reachable in the system. This type of symbolic model checking

can handle programs with a couple hundred variables, and state spaces ranging from  $10^{30}$  to  $10^{90}$  [61], whereas an explicit state model checking algorithm is restricted to state spaces that are small enough to be fully enumerated.

While BDD-based symbolic model checking can handle vastly larger designs than explicit state model checking, it still often can not scale to the sizes necessary for model checking software. Another symbolic model checking approach, bounded model checking [62], can handle much larger designs. In bounded model checking, the state space and property to verify are expressed as satisfiability problems and given to a SAT solver to either prove or disprove the property. SAT-based bounded model checking can scale to handle large designs. However, the drawback is that the state space of the program is explored only up to a certain depth. The behavior of the system past that depth is unknown.

Another approach for managing the large state space of software systems is to introduce some abstraction into the model of the program. In an abstraction, multiple program states are elided into one, and information about the program is lost. In a *sound abstraction*, a property proven true of the abstract model is true of the original program. However, the reverse may not be true: in a sound abstraction a safety property may be disproven for the abstract model even though it is actually true of the original program. Abstractions can be introduced by omitting some details of the original program from the model. For example, state variables deemed irrelevant for the verification task at hand may be left out of the model, reducing the total number of program states. Abstractions may also be introduced for systems with multiple, symmetric variables, processes, or data structures. In these cases a single instance might be modeled precisely, while the state and transitions of all other instances are conservatively over-approximated. For example, a single entry in a large array may be modeled precisely, while all other entries are modeled abstractly. In Chapter 3, we present a new technique for model checking systems with large data structures using a form of symmetry-based abstraction.

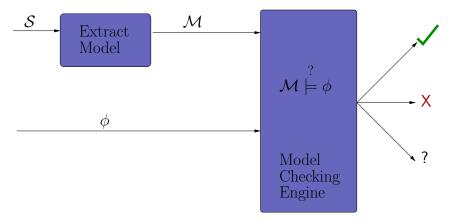

Although originally developed for the verification of hardware designs and other finite state systems, model checking techniques have successfully been applied to verifying software systems [63, 64]. Software model checking tools typically comprise an input or modeling language, a language for formalizing the properties, and the model checking engine. A typical work flow for model checking is shown in Figure 2.1. Given a program  $\mathcal{S}$ , the first step is to build a model  $\mathcal{M}$  of the program using the input language of the model checking engine. At the same time the property to be proven,  $\Phi$ , must be formalized using the specification language of the model checking engine. In our work, we focus on verifying safety properties, properties that state an invariant of the system. In this case, the model checking engine checks that  $\Phi$  holds at all system states, or equivalently, that no bad state, in which  $\Phi$  does not hold, is ever reachable. The model checking engine can output one of three results. The first is that the property is proven: the engine explored the entire state graph of the model and found no bad state. The second possible outcome is that the property does not hold. In this case, the model checking engine was able to find a reachable state in which  $\Phi$

was false, and typically, the model checking tool will return a counter-example. The third possible outcome is that the model checking engine was not able to prove the property holds, but neither was it able to find a bad state and corresponding counter-example. This result essentially means the model checking engine either timed out or ran out of memory before finding a counter-example or successfully proving the property.

Model checking is an automated technique that allows us to prove properties about software systems relatively quickly and without requiring significant expertise in formal methods. However, it does have its drawbacks. One concern is that verification is done on a model of the program, not on the program itself. Typically, the model is built manually and it is always possible for human error to introduce discrepancies between the model and the program. Even when a model checking tool operates directly on source code, it will internally construct a model of the code, and the verification often relies on manual pruning of the code plus manually created environment models. If a model does not correctly represent its program, any subsequent verification results do not accurately reflect the correctness of the program. In Chapter 4 we present a framework for validating a model against its program to address this weakness. A similar issue arises during code maintenance. Any updates to a verified software system will require updating and reverifying the model. Keeping the code and model synchronized throughout the lifetime of the system represents a serious engineering challenge. We do not address this issue directly, but rather point it out as evidence of the broad need for model validation research in general. Another consequence of manually built models is that the modeling effort involved in the verification of large system software, such as a hypervisor or CPU emulator, can be monumental. Techniques to automatically derive the model from the program would be useful and would mitigate that concern. In our work, we manage this limitation by focusing our verification efforts on one component of the system that is critical to security: the memory management subsystem.

A second concern is that the formal property  $\Phi$  may not be the right property. That is, it may not accurately reflect the high level system property that we wish to verify. This is a concern with any formal verification technique, including model checking. Typically, verification is done with some high-level English language property in mind. However, the verification tool, in this case, the model checking engine, requires the property be formalized. Correctly capturing the intended property in a mathematical formalism can be difficult. One way to protect against this type of error is to clearly define the high level properties of interest at the beginning of the verification effort and spend some time developing the corresponding mathematical statement. We do this in Chapter 3, where we discuss the high level security goals for this verification effort and spend some time developing the related formal properties.

Figure 2.1: Model checking work flow.

Given a system S, a model M is derived; M, along with the property to verify,  $\phi$ , are given to the model checking engine. The model checking engine can output one of three results: the property is proven to hold for the model, the property is proven not to hold, or the property can not be proven to hold, but neither has a counter-example been found before the engine times out.

#### 2.3 Related Work

#### Formal Verification of Systems Software

Verifying the security of virtualization software has its roots in a long history of work verifying the security of operating systems. Dating back to the late 1970's, early verification efforts concentrated on proving properties related to process or data isolation [65]. Typically, the operating system was designed from the ground up, alongside the verification effort, and was based on a capability mechanism in order to make verification of isolation properties more tenable [66]. Formalizing the desired property was a large part of the research effort. The properties were then proven for an abstract, high-level specification of the system, and then as the specification was refined and details were added, each new, lower-level specification was formally shown to refine its predecessor. The last level of refinement was the implementation, either in a high-level language like C or in the executable machine language, and this implementation was proven to correctly implement the lowest-level specification. By transitivity, the property proven true of the abstract specification was shown to be true of the implementation. These early verification efforts were done using semi-automated, machine checked proofs. The Provably Secure Operating System (PSOS) [66], the UCLA Unix Security Kernel [67], and Kit [68,69] are all examples of these systems, known generally as "security kernels."

In 1981 Rushby introduced the concept of a separation kernel [70]. Imagined as a way to make the verification of secure operating systems easier, the basic idea of a separation kernel is to mimic logically the physical separation provided by a distributed system. In

a separation kernel, execution contexts are separated into partitions, data is kept isolated within its partition, and information flow between partitions is always mediated. Typically, two partitions can communicate only through a small set of communication channels, which are determined once at initialization and kept invariant thereafter. The behavior and data of one partition is kept entirely separate from, and can have no effect on, every other partition.

Separation kernels make verification of secure operating systems easier by separating the policy from its enforcement. A separation kernel is responsible for providing data isolation and mediation for all information flow between partitions. However, it is up to an initialization process (usually running above the kernel level) to determine how the partitions should be set up: how many partitions there should be, which processes should run in each partition, and which partitions should be allowed to communicate with each other. In other words, it is up to that initialization process to set up the policy that says what security properties the system should provide. In this way, a separation kernel can be verified to show it properly enforces the partitioning, while the security policy of a particular system can be independently verified to show the system's policy provides the desired security properties. Greve et al. formalized the separation policy that a general purpose separation kernel should provide [71].

More recently, separation kernels have been used in a variety of security- and safety-critical contexts. Baumann et al. demonstrate the verification of the memory manager in PikeOS, a separation kernel based on the L4 kernel [72]. They show that memory will never be misallocated between partitions, and threads can only access memory within their own partition. The verification is done using a combination of automatic and manual tools. They use the VCC verifier for concurrent C code to establish certain lemmas hold for the source code, then a manual proof combines the lemmas into a proof of the isolation properties.

Separation kernels have been successfully used as the basis for systems requiring Common Criteria certification of level EAL6 or EAL7, the highest levels possible. Richards demonstrated the formalization and verification of a separation kernel in a real-time operating system environment used in avionics [73]. The verified separation property ensures fault-containment: a fault occurring in one partition will have no effect on the behavior of any other partition. Martin et al. report on the formal specification and development of a separation kernel for use in a smartcard [74]. The kernel provides the basis for the key management system of an F22 fighter aircraft and for secure radios used by the navy. Heitmeyer et al. demonstrate the formalization of a data separation property, and its verification, for an embedded device [75,76]. The kernel provides temporal as well as spatial data separation, as a partition's classification could change over time, and memory accessible at one classification level may not be accessible at a different classification level.

Perhaps the most complete verification, to date, of a modern, general purpose microkernel is the seL4 project [77,78]. The authors provide complete functional verification down to the source code level of the kernel, and their verification of information flow security properties make seL4 applicable as a separation kernel. The kernel's functionality is expressive enough

to allow a complete paravirtualized Linux kernel to run in one partition. However, this high assurance does come at a cost. Partitions are determined statically, and any desired communication between partitions must also be set up statically at initialization. Scheduling of partitions is done in a pre-determined, set round-robin fashion, with each partition getting a fixed time slice. As such, although an excellent example of verification of system software, seL4 is not suitable for use as a general purpose hypervisor. For example, data centers use hypervisors to try to eke out the most efficient allocation of resources to guest operating systems with varying workloads.

In all these cases, the formalization of the separation property differs slightly to suit the operating context, but the main goal – verifying isolation between components – is similar to our efforts to verify isolation between guest operating systems in a virtualized environment. The above research differs from ours, though, in that all the above cases, the separation kernel and its verification were developed together, whereas we focus on the verification of legacy software systems.

#### Verification of Virtualization Software

In this section we discuss some of the previous research exploring the possibility of verifying virtualization software.

Barthe et al. built a model of memory management in a paravirtualized hypervisor based on a simplified version of Xen [79]. They use the Coq proof assistant [80] to verify three properties of the model: 1) Isolation: A guest operating system can only read or write its own memory. 2) Non-interference: the behavior of one guest operating system is not influenced by the behavior of any other guest. 3) Liveness: a request made by a guest operating system to the hypervisor will eventually get a response. The model and proofs took around 20 KLOC in Coq's input language.

The Xenon project takes a step toward the verification of a general purpose hypervisor [81–83]. Based on the Xen hypervisor, Xenon strips out some non-essential features to make verification easier. The authors developed a formal specification of a security policy that guarantees non-interference between domains. This specification served as a guiding document during the re-engineering effort. They also developed formal models of some parts of the hypervisor, such as the hypercall interface. Full verification of an information flow security policy in a commodity hypervisor not designed for verification is an ambitious goal, and development of the formal models and specifications are important first steps. However, the verification of the specified properties was not completed.

The Hyper-V/VCC project represents perhaps the most ambitious hypervisor verification project to date [84]. The Hyper-V hypervisor is a large general-purpose hypervisor comprising roughly 100 KLOC in C and 5 KLOC in assembly [85]. It was not designed for verification, rather the reverse: the verification tool, VCC, was specifically designed for use

on large software systems such as Hyper-V. VCC is a verifier for concurrent C code [86]. It requires code be annotated and relies on code contracts, such as function pre- and post-conditions to develop the verification formula that can then be sent to an SMT solver for proof of validity. Along the way, the authors of this project developed a "baby hypervisor," the verification of which they used to guide the development of VCC [87]. For both the baby hypervisor and Hyper-V, the authors concentrated their verification efforts on memory virtualization, in particular that the virtual TLB presented to a guest correctly emulates the behavior of a physical TLB [88].

## Designing Virtualization Software for Verification

Formal verification of large software systems often runs into difficulty handling the complexity in these systems. The research described in this section tackles that problem by building systems specifically designed to make formal verification feasible. The designs focus on making the code modular, with well-defined interfaces, and often with functionality limited in some way that will considerably reduce complexity, thereby making verification easier.

Nova is an example of a hypervisor specifically designed for verification [89]. Similar to microkernels, much of the functionality of the hypervisor is moved to the user-level, minimizing the amount of privileged code that must be verified. Also similar to many microkernels, the Nova hypervisor is built around capability-based protection domains. The verification goals are to demonstrate spatial and temporal isolation between guest operating systems. The authors of Nova concentrate on tackling two challenges present in any verification effort: correct modeling of the system to be verified and correct representation of the system's environment. They tackle the first problem by developing a compiler from a subset of C++ to a formal semantics suitable for use as input to the PVS interactive theorem prover. This enables direct verification of the source code without requiring a modeling step. This is similar in some respects to the Hyper-V verification effort, which also included a translation from annotated C to a logical formula that could be then fed into a theorem prover. To model the environment, the Nova authors developed a formal description of parts of the IA32 architecture, including models of three memory interfaces provided by the physical CPU: physical RAM, memory-mapped devices, and virtual memory [90,91]. Although verification of the Nova hypervisor was not completed, its design, along with the environment models provide a strong contribution to the field of hypervisor design-for-verification [92].

Another, recent effort of hypervisor design for verification is the XMHF hypervisor framework [93]. The framework is designed to be an easily extended platform for building security-critical, hypervisor-based applications. The authors make three design choices to enable verification of the framework and any hypervisors built on top of it: 1) Common hypervisor functionality is built into the XMHF core, so that it can be verified once and then used by any hypervisor built on the framework. 2) The framework relies on new hardware support for virtualization [94], including nested page tables [95,96], DMA protection [97,98], and support

for dynamic root of trust [99]. This obviates the need to verify complex software implementations of these systems. However, it does not remove the complexity; rather, it pushes the complexity down to the hardware level. 3) Hypervisors built on the framework are restricted to supporting a single guest. This allows the hypervisor to be sequential and single-threaded, and it allows the guest OS to directly control any peripheral hardware devices. Verification of the XMHF framework focuses on proving memory integrity, i.e., guaranteeing that no guest can modify any of the hypervisor's code or memory. This is done using the CBMC model checker; however, some aspects of the code base, such as the logic for looping over the large page table structures, can not be handled by CBMC and for those portions, manual auditing is used to give confidence in the code's correctness. Managing large data structures during verification is a well-known challenge, and in Chapter 3 we present one solution for how to formally verify such structures.

#### **Testing Virtualization Software**

Another way to validate the correctness of virtualization software is by testing. With testing, the focus is on bug finding, rather than proving correctness. And, although the state space of these systems is by far too large to allow testing to be complete, several methods have been developed which have proven effective. Ormandy first used black box fuzz testing to look for security vulnerabilities in four virtualization software systems: Bochs, QEMU, VMware, and Xen [100]. He focused on the instruction decoding and handling mechanisms and used randomly generated inputs to find instructions or I/O activity that would cause the emulator to crash or exit abnormally. He found bugs in all four systems tested, and the bugs ranged from buffer and heap overflow errors to divide-by-zero errors. Ormandy showed that, for each system tested, an attacker could exploit the vulnerabilities found to reliably halt the virtualization process and, in some cases, take over the host process to run arbitrary code on the host. The latter is clearly dangerous, and the former can be used by the attacker to thwart malware analysis.

Martignoni et al. used directed fuzzing combined with differential testing to find bugs in process emulators, system emulators, and virtual machines [41]. In all cases, testing focused on finding defects in the emulation software, i.e., test cases or instructions that resulted in the emulated state differing from what the true state would have been. One of the challenges in using fuzzing-based methods on emulation software is achieving high instruction coverage; a random sampling of byte-code patterns is unlikely to achieve full x86 instruction coverage. A second challenge is determining, for each test case generated, what the correct system state should be after executing the instruction. Martignoni et al. tackle the first problem using a combination of purely random byte-code patterns and random data fields with known opcode fields. The authors tackle the second problem using a physical CPU as the oracle that gives the correct post-test case state. The authors looked at the system emulators Bochs, QEMU, VMware, and VirtualBox and found defects in all four of the systems. Paleari et al. applied a similar technique to x86 disassemblers, and again found bugs in all systems tested [101].

Disassembly code is similar to the instruction decode algorithms found in CPU emulators and hypervisors.

A different approach to testing virtualization software was taken by Martignoni et al. with their technique dubbed "path lifting" [40]. The authors use symbolic execution to explore paths through one "high-fidelity" emulator and use the results to generate test cases for a second "low-fidelity" emulator, looking for places where the behavior between the two emulators diverges. This approach is more complete than fuzz-based testing, but is still primarily concerned with bug finding. Like all the testing based techniques discussed in this section, path lifting is effective at finding bugs, but is unable to prove the absence of bugs or prove the validity of safety properties. That is the essential trade-off made between testing and formal verification: testing allows more automation at the expense of less strong results.

# Chapter 3

# Verifying Large Data Structures using Small and Short Worlds

A particular challenge for the verification of CPU emulators, virtual machine monitors, and hypervisors is their use of large data structures. For example, logical-to-physical address translation requires data structures to store the CPU's Translation Look-aside Buffer (TLB) and page tables. While these structures are finite-length for any given processor, they are usually too large to represent precisely for verification; often, they are abstracted to be of unbounded length. The data structures in the resulting model of the system are thus parametrized: the indices into those structures are parameters, taking values in a very large or even infinite domain (typically finite-precision bit-vectors or the integers). The techniques proposed for verifying such parametrized systems fall into two classes: those based on a smallmodel or cut-off theorem (e.g., [102–104]), or those based on abstraction (e.g., [105–107]). While existing approaches are elegant and effective for their respective problem domains, they fall short for the problems we consider: the small-model approaches usually restrict expressiveness, while abstraction-based approaches either focus on control properties (as opposed to equivalence/refinement) or handle only certain kinds of data structures. In both cases, some of the realistic case studies we consider cannot be handled. (We make a fuller comparison in Section 3.5.)

In this chapter, we present a new semi-automatic methodology for verifying safety properties in systems with large data structures [46]. Our approach comprises three steps. First, we employ standard mathematical induction to verify the safety property, and if that succeeds, the process is complete. Second, if induction fails, we create an over-approximate abstraction of the system, the "small world," in which unbounded data structures are parametrized and, in general, only a subset of the state is updated as per the original transition relation (e.g., only a few entries of the unbounded data structures); the rest of the state is updated with arbitrary values at each step. With this abstraction, the model is more amenable to state-space exploration. Third, we attempt to find a bound k on the reachability diameter of

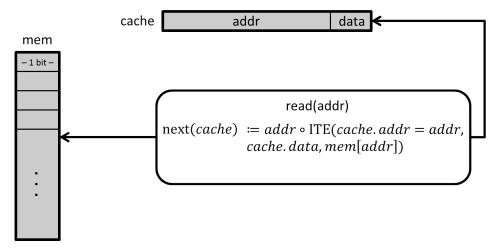

Figure 3.1: Running example.

A read-only memory and a single-entry cache. The cache is updated on each read command.

the small world so that, if bounded model checking (BMC) for k steps succeeds in the small world, then the safety property must hold in the small world, and since that is an over-approximation of the original system model, then the safety property holds there as well. Heuristics are presented for finding k that are effective for the class of systems we consider. We term this BMC-based approach the "short world" method, since it relies on computing a "short" bound for BMC. Our overall approach, termed Small-Short-World  $(S^2W)$ , is implemented on top of the UCLID system [108], which verifies abstract, term-level models using satisfiability modulo theories (SMT) solving. Note that the temporal safety verification problem for our class of systems is undecidable. As a result,  $S^2W$  is a semi-decision procedure.

## 3.1 Running Example

We introduce here a running example: a simple read-only memory system with a single-entry cache. We prove an invariant about the value returned by a read command. We build a model in our modeling language and demonstrate the verification of the safety property using  $S^2W$ . Our example is meant to be small, understandable, and illustrative, rather than "real-world."

Our example system (Figure 3.1) takes only one command, read, with a single parameter, the 32-bit address to be read; it returns a single-bit data value. At each read command, the cache is first checked. If the cache contains the data for the address requested, that value is returned. Otherwise, the value is read from memory. In either case, the cache is updated with the requested address and the returned data value. The update to cache is shown in the

above figure (we use "o" to mean concatenation). We prove an invariant about the cache: if the cache holds a valid address, then the cached data value is equal to the value stored in memory at that address. In other words, we show that the cache is correct.

## 3.2 Formal Description of the Problem

#### Notation and Terminology

A system is modeled as a tuple  $S = (\mathcal{I}, \mathcal{O}, \mathcal{V}, Init, \mathcal{A})$  where

- $\mathcal{I}$  is a finite set of input variables;

- $\mathcal{O}$  is a finite set of output variables;

- $\mathcal{V}$  is a finite set of state variables;

- Init is a set of initial states; and

- $\mathcal{A}$  is a finite set of assignments to variables in  $\mathcal{V}$ . Assignments define how state variables are updated, and thus define the transition relation of the system.

Input and output variables are assumed combinational (stateless), without loss of generality.  $\mathcal{V}$  is the only set of state-holding variables. Variables can be of two types: primitives, such as Boolean or bit-vector; and memories, which includes arrays, content-addressable memories (CAMs), and tables. An output variable is a function of  $\mathcal{V} \cup \mathcal{I}$ . When representing a system without outputs, we will omit  $\mathcal{O}$  from the representation. The set of initial states, Init, can either be viewed as a vector of symbolic terms representing any initial state, or as a Boolean-valued function of assignments to  $\mathcal{V}$ , written  $Init(\mathcal{V})$ .

Figure 3.2 denotes the grammar for expressions in our modeling language. The language has three expression types: Boolean, bit-vector, and memory.

```

\begin{array}{lll} b \mathbf{E} ::= & \text{true} \mid \text{false} \mid b \mid \neg b \mathbf{E} \mid b \mathbf{E}_1 \vee b \mathbf{E}_2 \\ & \mid b \mathbf{E}_1 \wedge b \mathbf{E}_2 \mid b \mathbf{v} \mathbf{E}_1 = b \mathbf{v} \mathbf{E}_2 \mid b \mathbf{vrel}(b \mathbf{v} \mathbf{E}_1, \dots, b \mathbf{v} \mathbf{E}_k) \ & \mid UP(b \mathbf{v} \mathbf{E}_1, \dots, b \mathbf{v} \mathbf{E}_k) \ & \mid (k \geq 0) \\ b \mathbf{v} \mathbf{E} ::= & c \mid v \mid ITE(b \mathbf{E}, \, b \mathbf{v} \mathbf{E}_1, \, b \mathbf{v} \mathbf{E}_2) \mid b \mathbf{vop}(b \mathbf{v} \mathbf{E}_1, \dots, b \mathbf{v} \mathbf{E}_k) \ & \mid m \mathbf{E}(b \mathbf{v} \mathbf{E}_1, \dots, b \mathbf{v} \mathbf{E}_l) \mid UF(b \mathbf{v} \mathbf{E}_1, \dots, b \mathbf{v} \mathbf{E}_k) \ & \mid (l \geq 1, k \geq 0) \\ m \mathbf{E} ::= & A \mid M \mid \lambda(x_1, \dots, x_k).b \mathbf{v} \mathbf{E} \ & \mid (k \geq 0) \end{array}

```

Figure 3.2: Expression Syntax.

c and v denote a bit-vector constant and variable, respectively, and b is a Boolean variable. by denotes any arithmetic/bitwise operator mapping bit-vectors to bit-vectors, while by rel is a relational operator other than equality mapping bit-vectors to a Boolean value. UF and UP denote an uninterpreted function and predicate symbol respectively. A and M denote constant and variable memories.  $x_1, \ldots, x_k$  denote parameters (typically indices into memories) that appear in bvE.

The simplest Boolean expressions (bE) are the constants true and false or Boolean variables b; more complicated expressions can be constructed using standard Boolean operators or using relational operators with bit-vector expressions. We also allow a Boolean expression to be an application of an uninterpreted predicate to bit-vector expressions.

Bit-vector expressions (bvE) include bit-vector constants, variables, if-then-else expressions (ITE), and expressions constructed using standard bit-vector arithmetic and bitwise operations. Additionally, bit-vector expressions can be constructed as applications of uninterpreted functions returning bit-vector values and applications of memories to bit-vector arguments. Each bit-vector expression has an associated bitwidth. When a bit-vector expression is used as an index into a memory we may abstract the bitwidth to be unbounded, meaning that the memory is of arbitrary size.

Finally, the primitive memory expressions (mE) can be (symbolic) constants or variables. More complex memory expressions can be modeled using the Lambda notation introduced by Bryant et al. [108] for term-level modeling; this includes the standard write (store) primitive for modeling arrays, as well as more general operations such as parallel updates to arrays, operations on CAMs, queues, and other data structures.

A next-state assignment  $\alpha$  denotes assignment to a state variable and is a rule of the form  $\mathtt{next}(x) := e, \mathtt{next}(x) := \{e_1, e_2, \dots, e_n\}$ , or  $\mathtt{next}(x) := \{*\}$ , where x is a signal in  $\mathcal{V}$ , and  $e, e_1, e_2, \dots, e_n$  are expressions that are a function of  $\mathcal{V} \cup \mathcal{I}$ . The curly braces express non-deterministic choice. The wildcard "\*" is also an expression of non-deterministic choice. It is translated at each transition into a fresh symbolic constant of the appropriate type. The set of all next-state assignments defines the transition relation  $\mathcal{R}$  of the system. Formally,  $\mathcal{R} = \bigwedge_{\alpha \in \mathcal{A}} r(\alpha)$ , where  $r(\mathtt{next}(x) := e) \doteq (x' = e)$  and  $r(\mathtt{next}(x) := \{e_1, e_2, \dots, e_n\}) \doteq \bigvee_{i=1}^n (x' = e_i)$ , where x' denotes the next-state version of variable x. We will sometimes write the transition relation as  $\mathcal{R}(\mathcal{V}, \mathcal{I}, \mathcal{V}')$  to emphasize that it relates current-state variables  $\mathcal{V}$  and next-state variables  $\mathcal{V}'$  based on the inputs  $\mathcal{I}$  received.

**Example 1** We formally describe our model from Section 3.1. Let  $S_T = (\mathcal{I}, \mathcal{O}, \mathcal{V}, Init, \mathcal{A})$  be the system, with

- $\mathcal{I} = \{addr\}$ . addr is the 32-bit address to read from memory.

- $\mathcal{O} = \{out\}$ . out is the value read from either memory or the cache.

- $\mathcal{V} = \{mem, cache\}$ . mem is constant and is modeled as an array of one-bit bit-vectors. It is represented by an uninterpreted function that maps a 32-bit address to a single bit. cache is a single 33-bit bit-vector; it holds the one-bit data value and 32-bit address of that value.

- $Init = (mem_0, cache_0)$ . mem is initialized to hold arbitrary data values at each address. cache is initialized to hold an invalid address, 0x000000000, with an arbitrary data value.

• A. On each read command *cache* is updated with the address read and the value returned by the read; *mem* remains constant.

#### **Problem Definition**

Consider a system  $\mathcal{S}$  modeled as described in the preceding section. We similarly model the environment  $\mathcal{E}$  that provides the inputs for  $\mathcal{S}$  and consumes its outputs. The composition of  $\mathcal{S}$  and  $\mathcal{E}$ , written  $\mathcal{S}||\mathcal{E}$ , is the model under verification,  $\mathcal{M}$ . The form of the composition depends on the context; we use both synchronous and asynchronous compositions. We will represent the closed system  $\mathcal{M}$  as a transition system  $(\mathcal{V}_{\mathcal{M}}, Init_{\mathcal{M}}, \mathcal{R}_{\mathcal{M}})$ , where the elements respectively denote state variables, initial states, and the transition relation. In all of our examples, the environment  $\mathcal{E}$  is stateless, generating completely arbitrary inputs to  $\mathcal{S}$  at each step; thus  $\mathcal{V}_{\mathcal{M}} = \mathcal{V}$ ,  $Init_{\mathcal{M}} = Init$  and  $\mathcal{R}_{\mathcal{M}} = \mathcal{R}$ .

This paper is concerned with verification of temporal safety properties of the form  $\mathbf{G}$   $\Phi$ , where  $\mathbf{G}$  is the temporal operator "always" and  $\Phi$  is a state invariant of the form

$$\forall x_1, \dots, x_k. \ \phi(x_1, \dots, x_k) \tag{3.1}$$

where  $\phi$  is a Boolean expression following the syntax of bE. The parameters  $x_1, \ldots, x_k$  are bit-vector valued, but usually too large to exhaustively case split on; therefore, it is common practice to abstract their bitwidths to be unbounded, and perform verification for memories of arbitrary size.

**Example 2** In our running example, we verify  $G \Phi_{3.2}$ , where

$$\Phi_{3.2} \doteq \forall x. \ (addr = x) \rightarrow \\ ((cache.addr = addr \land cache.addr \neq 0) \rightarrow \\ cache.data = mem[addr])$$

(3.2)

The problem tackled by this paper, temporal safety verification for systems with large data structures, is formally defined as follows.

**Definition 1 (Large Data Safety Verification)** Given a model  $\mathcal{M}$  formed as a composition of system  $\mathcal{S}$  and its environment  $\mathcal{E}$ , and a temporal safety property  $\mathbf{G}$   $\Phi$ , determine whether or not  $\mathcal{M}$  entails  $\mathbf{G}$   $\Phi$ .

This problem is known to be undecidable in general since a two-counter machine can be encoded in our formalism using applications of uninterpreted functions [109]. Hence, we can only devise a semi-decision procedure for the problem. In the next section, we describe such a procedure that is based on abstraction.

## 3.3 Methodology

$S^2W$  is based on a combination of abstraction and bounded model checking (BMC). We tackle state-space explosion by abstracting away all but a small subset of the space of the system. We call this mostly abstracted system our "small world." The abstracted portion of the system can be considered as being updated with an arbitrary value ("\*") at each step of execution. All other parts of the system are modeled precisely. Thus, this abstraction is a form of localization abstraction [110], where the localization is to small, finite portions of large data structures.

We check the safety property on the small world using BMC. To make BMC sound, we first find and prove the length of the diameter D of our small world to use as the bound – i.e., D is an integer such that every state reachable in D+1 steps is also reachable in D or fewer steps. Proving that a conjectured diameter D is correct is undecidable in our formalism [111]. The key to our approach is a set of heuristics that are effective in our chosen application domain of emulators, virtual machine monitors, and hypervisors. For our examples, the diameter of the mostly abstracted system is typically small; we therefore term this the "short world."

If BMC runs for D steps and does not find a violation of the safety property in our small world, then the original model is safe. If BMC finds a counter-example, we cannot say whether the property holds for the original model: BMC can return a spurious counter-example. Choosing the small world well reduces the likelihood of finding spurious counter-examples.

To summarize, there are two crucial pieces to our approach: choosing the right small world and proving the length of the short world. We discuss both of these in more detail below.

As an optimization, we prefix the above approach with an attempt to prove the safety property using one-step induction (on the original, non-abstract model,  $\mathcal{M}$ ). If that succeeds, there is no need to continue on to  $S^2W$ 's abstraction. This step can be generalized to perform k-step induction as needed.

For the presentation in this section, it is convenient to represent the system under verification  $\mathcal{S}$  as a transition system  $(\mathcal{I}, \mathcal{V}, \mathcal{R}, Init)$  where the elements of the tuple have the same meanings as in Section 3.2. The environment  $\mathcal{E}$  sets the values of the input variables in  $\mathcal{I}$  at each step; in all our case studies, the inputs from  $\mathcal{E}$  are completely unconstrained. Verification (using induction or BMC) is performed on the composition of  $\mathcal{S}$  and  $\mathcal{E}$ .

#### Induction

First,  $S^2W$  attempts to prove the safety property using simple one-step induction on the non-abstract model  $\mathcal{M}$ . We check the validity of the following two formulas, as per standard

23

practice:

$$Init_{\mathcal{M}}(\mathcal{V}_{\mathcal{M}}) \to \Phi(\mathcal{V}_{\mathcal{M}})$$

(3.3)

$$\Phi(\mathcal{V}_{\mathcal{M}}) \wedge \mathcal{R}_{\mathcal{M}}(\mathcal{V}_{\mathcal{M}}, \mathcal{V}'_{\mathcal{M}}) \to \Phi(\mathcal{V}'_{\mathcal{M}})$$

(3.4)

If both checks pass, the verification is complete. We report "Property valid" and exit. If check 3.3 fails, the property is invalid. We report "Property invalid in initial state" and exit. If check 3.4 fails, we continue with  $S^2W$ , to find the small world.

#### Small World

The objective of this step is to identify a small portion of system state that we should model precisely during BMC. Everything else will be allowed to take on arbitrary values at each step of execution.

It is important to note that the soundness of  $S^2W$  does not depend on the choice we make for the small world; we could randomly select some portion of the state to model precisely, abstract everything else away, and if our three steps complete and verify the property, the property would be true of the original, non-abstracted system. However, choosing the small world wisely ensures that the short world is indeed short, which allows BMC to complete in a reasonable amount of time. A well-chosen small world also reduces the number of spurious counter-examples returned by the BMC step.

We present here a heuristic for choosing the small world when dealing with systems involving large or unbounded data structures. In our case studies, the heuristic found a small world whose short world was reasonable in length and for which no spurious counter-examples were returned by the BMC.

To select those state variables to model precisely,  $S^2W$  starts with the property  $\mathbf{G}$   $\Phi$ , where  $\Phi$  is of the form  $\forall x_1, x_2, \ldots, x_n$ .  $\phi(x_1, x_2, \ldots, x_n)$ . If we prove  $\Phi$  by instantiating the quantifier with a completely arbitrary, symbolic parameter vector  $(a_1, a_2, \ldots, a_n)$ , that suffices to prove the original property. Thus, starting with the symbolic vector  $(a_1, a_2, \ldots, a_n)$ , we compute a dependence set  $\mathcal{U}$  for the instantiated property  $\phi(a_1, a_2, \ldots, a_n)$ .  $\mathcal{U}$  is a set of expressions involving state variables and the parameters  $a_1, \ldots, a_n$  such that fixing the values of the expressions in this set fixes the value of the instantiated property. For variable M modeling a memory, these expressions typically involve indexing into M at a finite number of (symbolic) addresses. For a Boolean or bit-vector variable, either the variable is in  $\mathcal{U}$  or not.

Typically, this set of expressions is derived syntactically by traversing the expression graph of the formula  $\phi$  represented in terms of state and input variables (after performing certain simplifications).

**Example 3** In our running example, recall that the property is G  $\Phi_{3,2}$  where:

$$\Phi_{3.2} \doteq \forall x. \ (addr = x) \rightarrow$$

$$((cache.addr = addr \land cache.addr \neq 0) \rightarrow$$

$$cache.data = mem[addr])$$

$\Phi_{3.2}$  has the form  $\forall x. \ \phi(x)$ . Instantiating x with a, a fresh symbolic constant, we can drop the quantifier and get  $\phi(a)$ , for which, by propagating the equality addr = a, we see that its value is determined by the expressions mem[a] and cache. Thus, we use  $\mathcal{U} = \{mem[a], cache\}$  as our dependence set.

Once we have computed  $\mathcal{U}$ , using the above heuristic or some other method, we can define our small world. Recall that  $\mathcal{S}$  is represented as a symbolic transition system  $(\mathcal{I}, \mathcal{V}, \mathcal{R}, Init)$ . Let  $\hat{\mathcal{R}}$  be a transition relation that differs from  $\mathcal{R}$  by setting all state variables not in  $\mathcal{U}$  to a non-deterministic value and leaving all others unchanged. Abusing notation slightly to use  $\mathcal{U}$  wherever we use  $\mathcal{V}$ , this means that  $\hat{\mathcal{R}}(\mathcal{U}, \mathcal{I}, \mathcal{U}') = \mathcal{R}(\mathcal{U}, \mathcal{I}, \mathcal{U}')$ , and  $\hat{\mathcal{R}}(\mathcal{W}, \mathcal{I}, \mathcal{W}') = \text{true}$  for  $\mathcal{W} = \mathcal{V} \setminus \mathcal{U}$ . Similarly,  $\hat{Init}(\mathcal{U}) = Init(\mathcal{U})$  and  $\hat{Init}(\mathcal{W}) = \text{true}$ .

Then the abstracted small world is  $\hat{\mathcal{S}} = (\mathcal{I}, \mathcal{V}, \hat{\mathcal{R}}, \hat{Init})$ .  $\hat{\mathcal{S}}$  is an overapproximate, abstract version of  $\mathcal{S}$  that precisely tracks only the state in  $\mathcal{U}$ , and allows all other variables to change arbitrarily at each step of execution. Thus, the composition of  $\hat{\mathcal{S}}$  and  $\mathcal{E}$  is an overapproximate model  $\hat{\mathcal{M}}$ . It is important to note that if  $\mathcal{M}$  was infinite-state,  $\hat{\mathcal{M}}$  continues to remain so.

The next step is proving a short world for  $\hat{S}$  and using BMC on  $\hat{\mathcal{M}}$  to verify the property.

#### Short World

The objective of this phase is to determine a bound on the diameter D of the abstract model  $\hat{\mathcal{M}}$ . For this section, we will assume that  $\mathcal{E}$  is stateless, as is the case for all of our case studies; the approach extends in a straightforward manner for the general case. Thus, the diameter of  $\hat{\mathcal{M}}$  is the same as that of  $\hat{\mathcal{S}}$ .

Suppose we believe the diameter to be  $D \leq k$ . To verify this bound, we check the validity of the following logical formula:

$$\forall \mathcal{V}_{0}, \mathcal{V}_{1}, \dots, \mathcal{V}_{k+1}, \mathcal{I}_{1}, \mathcal{I}_{2}, \dots, \mathcal{I}_{k+1}.$$

$$\left[Init(\mathcal{V}_{0}) \wedge \bigwedge_{i=0}^{k} \hat{\mathcal{R}}(\mathcal{V}_{i}, \mathcal{I}_{i+1}, \mathcal{V}_{i+1})\right] \rightarrow$$

$$\left[\exists \mathcal{V}'_{0}, \mathcal{V}'_{1}, \dots, \mathcal{V}'_{k}, \mathcal{I}'_{1}, \mathcal{I}'_{2}, \dots, \mathcal{I}'_{k}.Init(\mathcal{V}'_{0}) \wedge \bigwedge_{i=0}^{k-1} \hat{\mathcal{R}}(\mathcal{V}'_{i}, \mathcal{I}'_{i+1}, \mathcal{V}'_{i+1}) \wedge \bigvee_{i=0}^{k} \mathcal{V}_{k+1} = \mathcal{V}'_{i}\right] \quad (3.5)$$

Since  $\hat{\mathcal{R}}$  modifies state expressions outside  $\mathcal{U}$  arbitrarily on each step, we can replace  $\mathcal{V}$  everywhere in the above formula with  $\mathcal{U}$ , and obtain the actual convergence criterion that must be checked.

Nevertheless, checking the convergence criterion is undecidable for the class of systems we are interested in, due to the presence of uninterpreted functions, memories, and parameters with unbounded bitwidth [111]. The quantified formula in (3.5) is also hard to solve in practice. Therefore, quantifier instantiation heuristics must be devised to perform the convergence check. In this section, we present two such heuristics that have worked well for the range of case studies considered in this paper.

#### The Sub-Sequence Heuristic

The first heuristic checks that for any state reachable in k+1 steps using k+1 symbolic inputs to  $\hat{S}$ , one can also reach that state using *some sub-sequence of length*  $\leq k$  of those k+1 symbolic inputs. We can express the sub-sequence heuristic as performing a particular instantiation of the existential quantifiers in criterion 3.5, and checking the validity of the following formula that results:

$$\forall \mathcal{U}_{0}, \mathcal{U}_{1}, \dots, \mathcal{U}_{k+1}, \mathcal{I}_{1}, \mathcal{I}_{2}, \dots, \mathcal{I}_{k+1}, \mathcal{U}'_{0}, \mathcal{U}'_{1}, \dots, \mathcal{U}'_{k}.$$

$$\left[Init(\mathcal{U}_{0}) \wedge (\mathcal{U}_{0} = \mathcal{U}'_{0}) \wedge \bigwedge_{i=0}^{k} \hat{\mathcal{R}}(\mathcal{U}_{i}, \mathcal{I}_{i+1}, \mathcal{U}_{i+1})\right] \rightarrow$$