## Bounds on the Energy Consumption of Computational Kernels

Andrew Gearhart

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2014-175 http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-175.html

October 23, 2014

Copyright © 2014, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

Research partially funded by DARPA Award Number HR0011-12-2-0016, the Center for Future Architecture Research, a member of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA, and ASPIRE Lab industrial sponsors and affiliates Intel, Google, Nokia, NVIDIA, Oracle, and Samsung. Any opinions, findings, conclusions, or recommendations in this paper are solely those of the authors and does not necessarily reflect the position or the policy of the sponsors.

### Bounds on the Energy Consumption of Computational Kernels

by

Andrew Scott Gearhart

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

and the Designated Emphasis

in

Computational Science and Engineering

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor James W. Demmel, Chair Professor Katherine A. Yelick Professor Tarek I. Zohdi

Fall 2014

### Bounds on the Energy Consumption of Computational Kernels

Copyright 2014 by Andrew Scott Gearhart

#### Abstract

## Bounds on the Energy Consumption of Computational Kernels by Andrew Scott Gearhart Doctor of Philosophy in Computer Science and the Designated Emphasis in Computational Science and Engineering University of California, Berkeley Professor James W. Demmel, Chair

As computing devices evolve with successive technology generations, many machines target either the mobile or high-performance computing/datacenter environments. In both of these form factors, energy consumption often represents the limiting factor on hardware and software efficiency. On mobile devices, limitations in battery technology may reduce possible hardware capability due to a tight energy budget. On the other hand, large machines such as datacenters and supercomputers have budgets directly related to energy consumption and small improvements in energy efficiency can significantly reduce operating costs. Such challenges have influenced research upon the impact of applications, operating and runtime systems upon energy consumption. Until recently, little consideration was given to the potential energy efficiency of algorithms themselves.

A dominant idea within the high-performance computing (HPC) community is that applications can be decomposed into a set of key computational problems, called *kernels*. Via automatic performance tuning and new algorithms for many kernels, researchers have successfully demonstrated performance improvements on a wide variety of machines. Motivated by the large and increasingly growing dominant cost (in time and energy) of moving data, algorithmic improvements have been attained by proving lower bounds on the data movement required to solve a computational problem, and then developing *communication-optimal* algorithms that attain these bounds.

This thesis extends previous research on communication bounds and computational kernels by presenting *bounds on the energy consumption* of a large class of algorithms. These bounds apply to sequential, distributed parallel and heterogeneous machine models and we detail methods to further extend these models to larger classes of machines. We argue that the energy consumption of computational kernels is usually predictable and can be modeled via linear models with a handful of terms. Thus, these energy models (and the accompanying bounds) may apply to many HPC applications when used in composition.

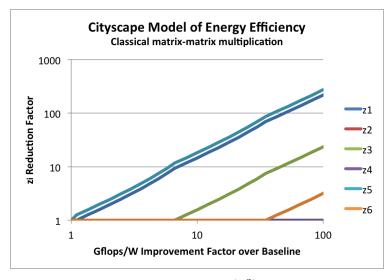

Given energy bounds, we analyze the implications of such results under additional constraints, such as an upper bound on runtime, and also suggest directions for future research that may aid future development of a hardware/software co-tuning process. Further, we present a new model of energy efficiency, Cityscape, that allows hardware designers to quickly target areas for improvement in hardware attributes. We believe that combining our bounds with other models of energy consumption may provide a useful method for such co-tuning; i.e. to enable algorithm and hardware architects to develop provably energy-optimal algorithms on customized hardware platforms.

Now this is not the end. It is not even the beginning of the end. But it is, perhaps, the end of the beginning.

- Sir Winston Churchill, 1942

# Contents

| C  | onten                     | ts                                                                                            | ii                 |

|----|---------------------------|-----------------------------------------------------------------------------------------------|--------------------|

| Li | st of l                   | Figures                                                                                       | v                  |

| Li | st of '                   | Tables                                                                                        | vii                |

| 1  | <b>Intr</b><br>1.1<br>1.2 | oductionCommunication Now Dominates Performance CostsEnergy Efficiency at the Algorithm Level | <b>1</b><br>1<br>2 |

|    | 1.3<br>1.4                | Thesis Goals and Contributions                                                                | 2<br>3             |

| 2  | Ene                       | rgy Consumption and Computing                                                                 | 5                  |

|    | 2.1                       | Power vs. Energy                                                                              | 6                  |

|    | 2.2                       | Phase-based Execution of Applications                                                         | 7                  |

|    | 2.3                       | Key Consumers of Energy on Desktops and Server Nodes                                          | 9                  |

|    |                           | Energy Consumption in CMOS Logic                                                              | 10                 |

|    |                           | Other Hardware Components                                                                     | 14                 |

|    | 2.4                       | Network Energy Consumption on Distributed Parallel Machines                                   | 15                 |

| 3  | Mac                       | chine Models for Runtime and Energy                                                           | 17                 |

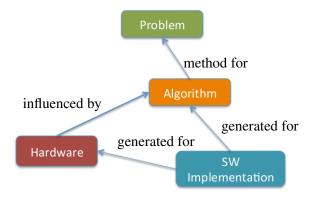

|    | 3.1                       | Problems, Algorithms, and Implementations                                                     | 17                 |

|    | 3.2                       | Machine Models                                                                                | 18                 |

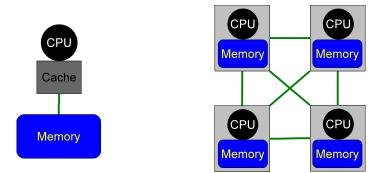

|    |                           | Sequential Machine Model (S)                                                                  | 19                 |

|    |                           | Distributed Parallel Machine Model 1 (DP1)                                                    | 21                 |

|    |                           | Model Compositions and Distributed Parallel Model 2 (DP2)                                     | 21                 |

|    |                           | Heterogeneous Machine Model (H)                                                               | 23                 |

|    | 3.3                       | Problems of Particular Focus                                                                  | 25                 |

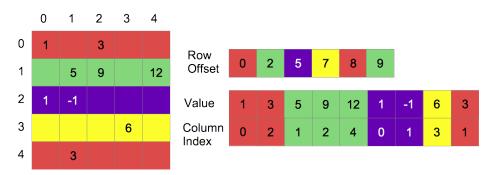

|    |                           | Matrix-vector multiplication                                                                  | 26                 |

|    |                           | Matrix-matrix Multiplication                                                                  | 29                 |

|    |                           | $O(n^2)$ <i>n</i> -body problem                                                               |                    |

|    | 3.4                       | Model Validation                                                                              | 37                 |

|   | 3.5                                                                                                           | Performance Counter Measurement                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |

|---|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 4 | Bou                                                                                                           | nds on Communication, Runtime and Energy for Specific Algorithms                                                                                                                                                                                                                                                                                                                                                    | 61                                                                                       |

|   | 4.1                                                                                                           | Communication Lower Bounds for Sequential and Distributed Parallel Machines .                                                                                                                                                                                                                                                                                                                                       | 61                                                                                       |

|   |                                                                                                               | Lower Bounds on the DP Models that Include Link Contention                                                                                                                                                                                                                                                                                                                                                          | 64                                                                                       |

|   | 4.2                                                                                                           | Energy Lower Bounds for Specific Algorithms                                                                                                                                                                                                                                                                                                                                                                         | 69                                                                                       |

|   |                                                                                                               | $O(n^3)$ Classical Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                            | 69                                                                                       |

|   |                                                                                                               | Strassen and Strassen-like Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                    | 72                                                                                       |

|   |                                                                                                               | Matrix-vector multiplication $\dots \dots \dots$                                                                                                                                                                                                                                                                    | 74<br>75                                                                                 |

|   | 4.3                                                                                                           | $O(n^2)$ n-body problem                                                                                                                                                                                                                                                                                                                                                                                             | 73<br>78                                                                                 |

|   | 4.3                                                                                                           | Bounds on Heterogeneous Machines                                                                                                                                                                                                                                                                                                                                                                                    | 80                                                                                       |

|   |                                                                                                               | Loomis-Whitney Dominated Lower Bound                                                                                                                                                                                                                                                                                                                                                                                | 82                                                                                       |

|   | 4.4                                                                                                           | Optimal Heterogeneous Algorithms                                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                                       |

|   |                                                                                                               | Heterogeneous Matrix-Vector Multiplication                                                                                                                                                                                                                                                                                                                                                                          | 84                                                                                       |

|   |                                                                                                               | Heterogeneous $O(n^3)$ Matrix-Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                 | 86                                                                                       |

|   |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |

| 5 | Bou                                                                                                           | nds on Communication, Runtime and Energy for Programs that Access Arrays                                                                                                                                                                                                                                                                                                                                            | 90                                                                                       |

| 5 | <b>Bou</b><br>5.1                                                                                             | nds on Communication, Runtime and Energy for Programs that Access Arrays<br>Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                | <b>90</b><br>90                                                                          |

| 5 |                                                                                                               | nds on Communication, Runtime and Energy for Programs that Access ArraysBounds on Programs that Reference ArraysSequential Model                                                                                                                                                                                                                                                                                    |                                                                                          |

| 5 |                                                                                                               | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1                                                                                                                                                                                                                                                                                                                                | 90<br>95<br>95                                                                           |

| 5 |                                                                                                               | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1Distributed Parallel Model 2                                                                                                                                                                                                                                                                                                    | 90<br>95<br>95<br>96                                                                     |

| 5 |                                                                                                               | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1Distributed Parallel Model 2Heterogeneous Model                                                                                                                                                                                                                                                                                 | 90<br>95<br>95<br>96<br>97                                                               |

| 5 | 5.1                                                                                                           | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1Distributed Parallel Model 2Heterogeneous ModelExample: Energy Lower Bound for Matrix-matrix Multiplication                                                                                                                                                                                                                     | 90<br>95<br>95<br>96<br>97<br>98                                                         |

| 5 |                                                                                                               | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1Distributed Parallel Model 2Heterogeneous Model                                                                                                                                                                                                                                                                                 | 90<br>95<br>95<br>96<br>97                                                               |

| 5 | 5.1                                                                                                           | Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                                                                                            | 90<br>95<br>95<br>96<br>97<br>98                                                         |

|   | 5.1                                                                                                           | Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                                                                                            | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b>                                           |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>App</li> <li>6.1</li> <li>6.2</li> </ul>                                   | Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                                                                                            | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b><br>105                                    |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>App<br/>6.1</li> <li>6.2</li> <li>6.3</li> </ul>                           | Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                                                                                            | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b><br>105<br>108                             |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>App<br/>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul>              | Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                                                                                            | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b><br>105<br>108<br>111                      |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>App<br/>6.1</li> <li>6.2</li> <li>6.3</li> </ul>                           | Bounds on Programs that Reference Arrays                                                                                                                                                                                                                                                                                                                                                                            | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b><br>105<br>108<br>111                      |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>App<br/>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1Distributed Parallel Model 2Heterogeneous ModelExample: Energy Lower Bound for Matrix-matrix MultiplicationPerfect Strong Scaling in the Distributed Machine ModelHeteroyeneous ModelClassical $O(n^3)$ Matrix-matrix Multiplication $O(n^2)$ n-body problemPrograms that access arrays with subsets of the iteration variables | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b><br>105<br>108<br>111                      |

| 6 | <ul> <li>5.1</li> <li>5.2</li> <li>App<br/>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Bounds on Programs that Reference ArraysSequential ModelDistributed Parallel Model 1Distributed Parallel Model 2Heterogeneous ModelExample: Energy Lower Bound for Matrix-matrix MultiplicationPerfect Strong Scaling in the Distributed Machine ModelHeteroyeneous ModelClassical $O(n^3)$ Matrix-matrix Multiplication $O(n^2)$ n-body problemPrograms that access arrays with subsets of the iteration variables | 90<br>95<br>96<br>97<br>98<br>99<br><b>105</b><br>108<br>111<br>117<br>122<br><b>130</b> |

| Bi | bliogr | aphy                                                 |  |  |  |  |  |  |  |  |  |  |  |  | 150 |

|----|--------|------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|-----|

| 8  | Con    | clusions                                             |  |  |  |  |  |  |  |  |  |  |  |  | 147 |

|    |        | Financial cost/Job $(C_{job})$<br>Further Directions |  |  |  |  |  |  |  |  |  |  |  |  |     |

iv

# **List of Figures**

| 2.1  | Tradeoff between minimizing energy or power                                                | 6  |

|------|--------------------------------------------------------------------------------------------|----|

| 2.2  | Typical Scientific Code Power Trace                                                        | 8  |

| 2.3  | Power phases of matmul benchmark on Sandy Bridge-EP                                        | 8  |

| 2.4  | Power phases of heterogeneous matmul on Sandy Bridge-EP and Nvidia K20                     | 9  |

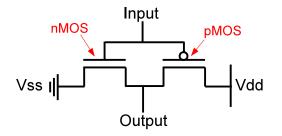

| 2.5  | CMOS inverter with n-type (nMOS) and p-type (pMOS) transistors indicated                   | 11 |

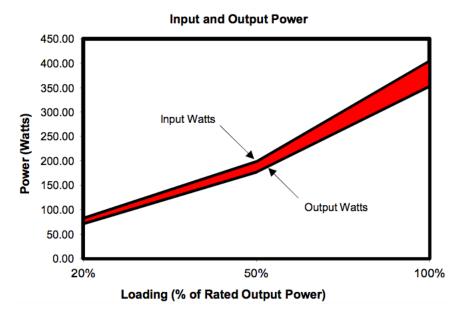

| 2.6  | Input/Output wattage curves for a Dell DH350E-S0 power supply for 2U servers [1]           | 15 |

| 3.1  | Relationship between hardware, algorithm and implementation                                | 18 |

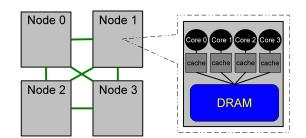

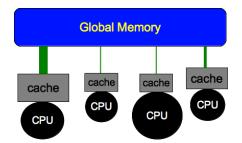

| 3.2  | Serial (S) and Distributed Parallel (DP) machine models                                    | 19 |

| 3.3  | Composition of Sequential (S) and Distributed Parallel (DP) Machine Models                 | 22 |

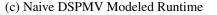

| 3.4  | Heterogeneous machine model                                                                | 24 |

| 3.5  | Compressed Sparse Row (CSR) storage format                                                 | 28 |

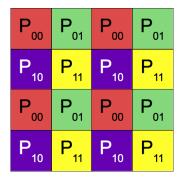

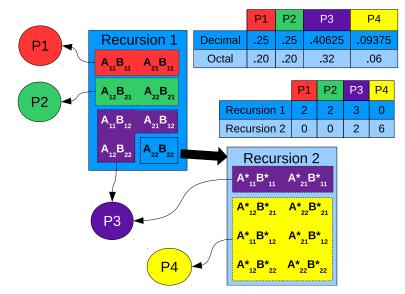

| 3.6  | Two-dimensional block cyclic distribution of a matrix on a 2-by-2 processor grid           | 31 |

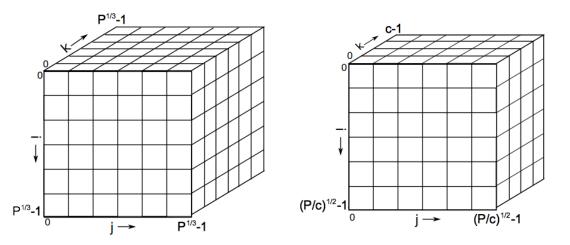

| 3.7  | Processor grids for 3D and 2.5D matrix-matrix multiplication [126]                         | 32 |

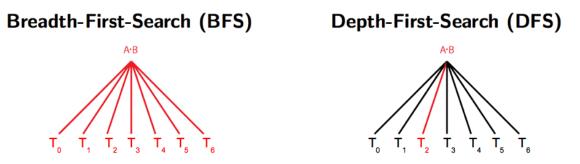

| 3.8  | Breadth-First or Depth-First traversals of recursion tree [98]                             | 35 |

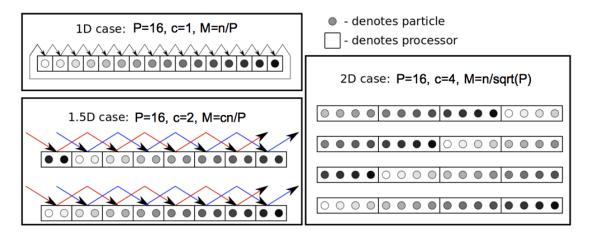

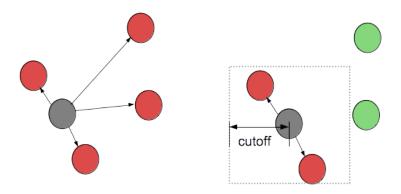

| 3.9  | Data layouts for 1D, 1.5D and 2D <i>n</i> -body algorithms                                 | 36 |

| 3.10 |                                                                                            | 37 |

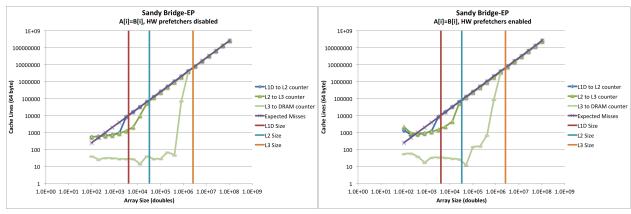

|      | Counting cache misses during array copy on Sandy Bridge-EP                                 | 39 |

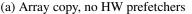

|      | Inaccurate floating point operation counts on Sandy Bridge-EP                              | 39 |

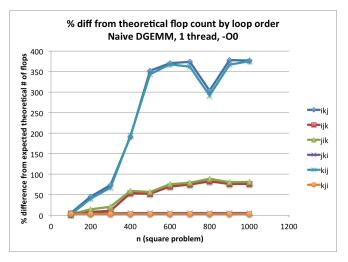

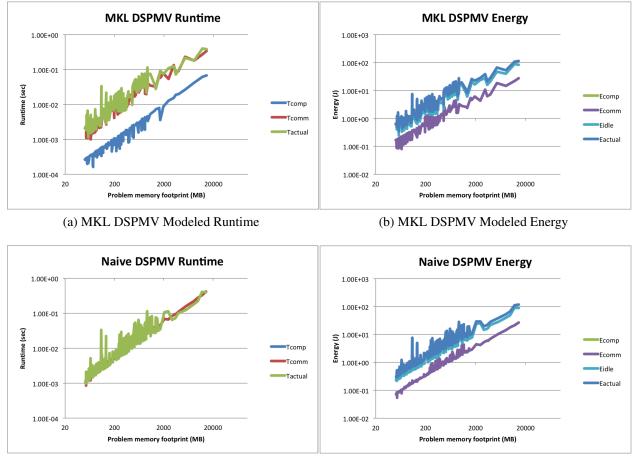

| 3.13 | Typical wall power sample windows for several sparse matrix-vector multiplication problems | 41 |

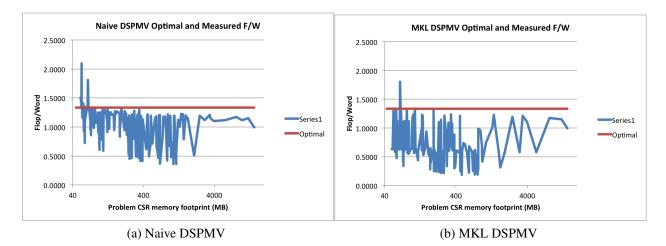

| 3.14 | Sandy Bridge-EP: Flop/Word ratios for double-precision sparse matrix-vector multi-         |    |

|      | plication (DSPMV)                                                                          | 45 |

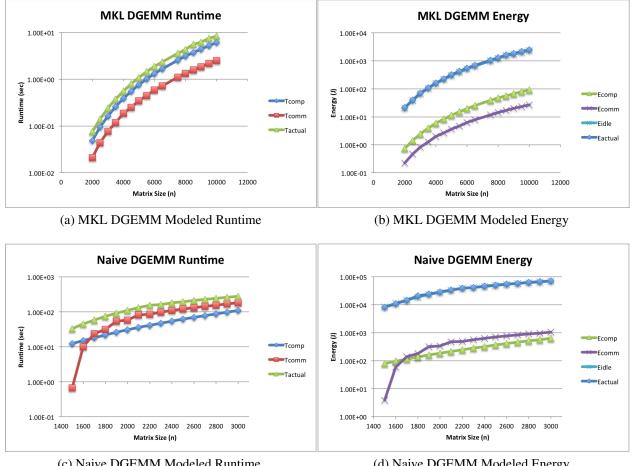

| 3.15 | Sandy Bridge-EP: Modeled (no row scaling) double-precision matrix-matrix multipli-         |    |

|      | cation (DGEMM)                                                                             | 49 |

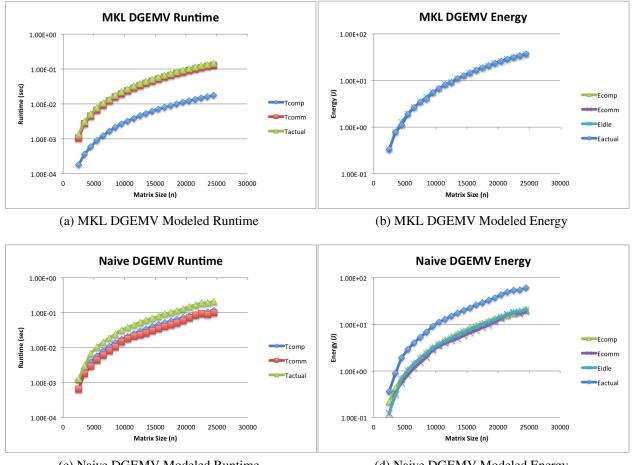

| 3.16 | Sandy Bridge-EP: Modeled (no row scaling) double-precision dense matrix-vector             |    |

|      | multiplication (DGEMV)                                                                     | 50 |

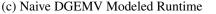

| 3.17 | Sandy Bridge-EP: Modeled (no row scaling) double-precision sparse matrix-vector            |    |

|      | multiplication (DSPMV)                                                                     | 51 |

| 3.18 | Heterogeneous machine for validation                                                       | 53 |

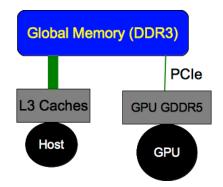

| 3.19 | Runtime impact of scaling either Host or GPU SGEMM size                                    | 54 |

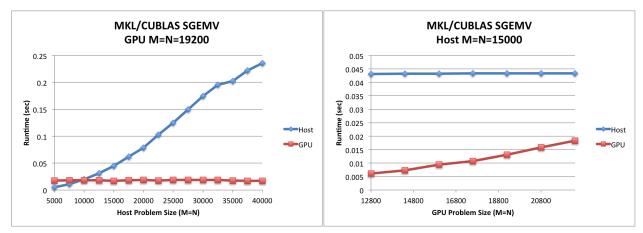

| 3.20 | Runtime impact of scaling either Host or GPU SGEMV size                                    | 56 |

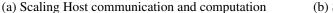

| 4.1 | Communication bounds for Strassen's algorithm on <i>d</i> -dimensional tori. The lower plot is log-log, while the upper is linear on the y-axis. Horizontal lines in the lower plot |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | correspond to perfect strong scaling                                                                                                                                                |

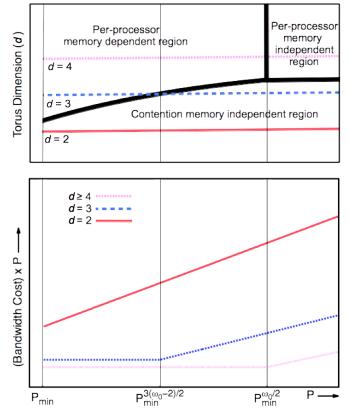

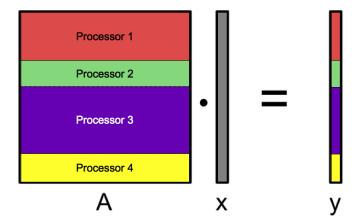

| 4.2 | Example of heterogeneous matrix-vector data partitioning with 4 processors 85                                                                                                       |

| 4.3 | Heterogeneous matrix-matrix computation example execution on 4 processors 89                                                                                                        |

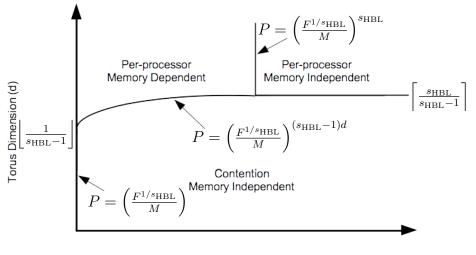

| 5.1 | Relationship between the per-processor and contention communication lower bounds, with labels on each region indicating lower bound dominance. $F$ and $M$ are constants. 93        |

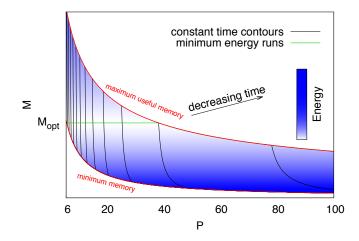

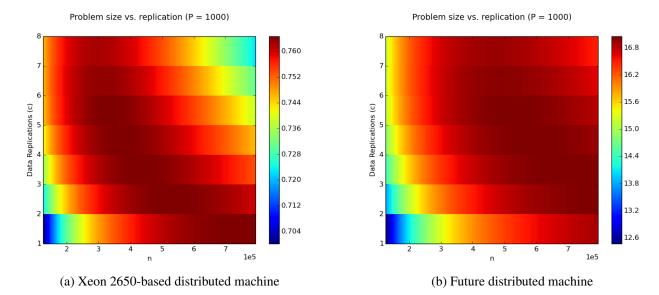

| 6.1 | Energy costs as node count and memory are scaled                                                                                                                                    |

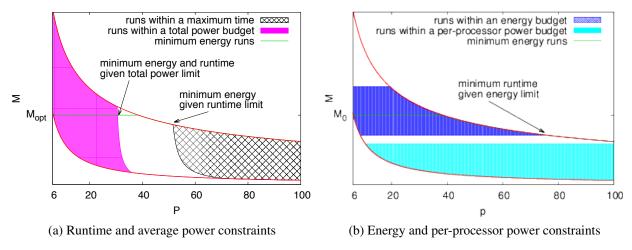

| 6.2 | Effect of constraints on energy efficiency                                                                                                                                          |

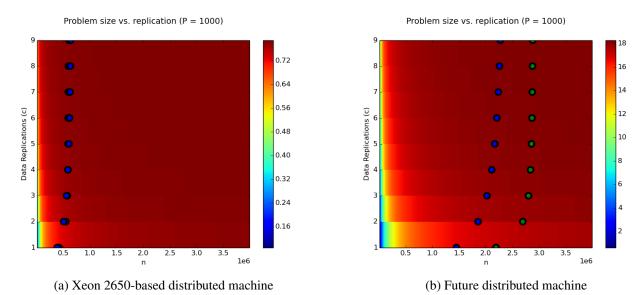

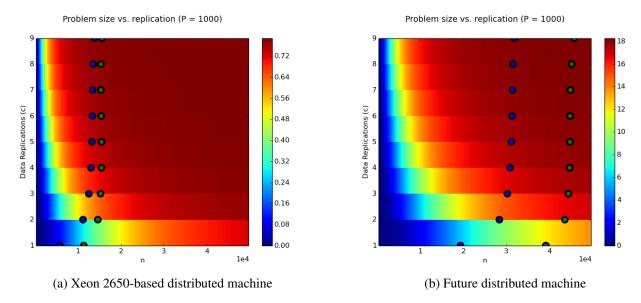

| 6.3 | 2.5D $O(n^3)$ Matrix-matrix Multiplication: Effect of replicating memory on energy                                                                                                  |

|     | efficiency                                                                                                                                                                          |

| 6.4 | CA $O(n^2)$ n-body: Effect of replicating memory on energy efficiency                                                                                                               |

| 6.5 | 3-Body Problem: Effect of replicating memory on energy efficiency                                                                                                                   |

| 7.1 | Example Cityscape Model for $O(n^3)$ Matrix-matrix multiplication                                                                                                                   |

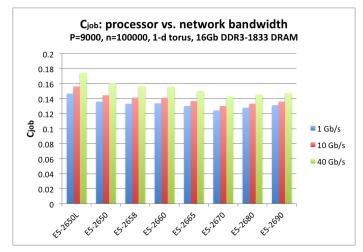

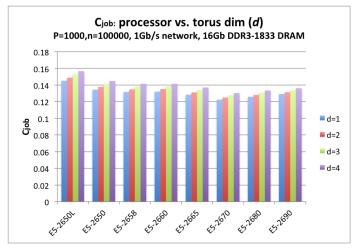

| 7.2 | $C_{job}$ with various parameter sets for Algorithm 11                                                                                                                              |

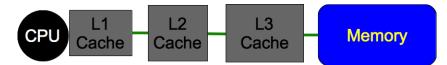

| 7.3 | Sequential Machine with 3 levels of fast memory                                                                                                                                     |

# **List of Tables**

| 3.1  | Computational motifs as described in [9]                                                             | 26  |

|------|------------------------------------------------------------------------------------------------------|-----|

| 3.2  | Measuring Data Movement on Sandy Bridge-EP                                                           | 38  |

| 3.3  | Sandy Bridge-EP: Arithmetic intensity (flop/word) for naive matrix-matrix multiplication             | 44  |

| 3.4  | Sandy Bridge-EP: Average runtime and energy % error (no row scaling)                                 | 46  |

| 3.5  | Xeon 7560: Average runtime and energy % error (no row scaling)                                       | 46  |

| 3.6  | Sandy Bridge-EP: Average runtime and energy % error (1/F row scaling)                                | 46  |

| 3.7  | Sandy Bridge-EP: Fitted sequential machine parameters without row scaling                            | 47  |

| 3.8  | Sandy Bridge-EP: Modeled vs. Measured Runtime Throughputs                                            | 47  |

| 3.9  | Xeon 7560: Fitted sequential machine parameters without row scaling                                  | 48  |

| 3.10 | Xeon 7560: Modeled vs. Measured Runtime Throughputs                                                  | 48  |

| 3.11 | Sandy Bridge-EP: Average runtime and energy % error when non-dominant terms are                      |     |

|      | dropped from model (with row scaling)                                                                | 52  |

| 3.12 | Sandy Bridge-EP: Fitted sequential machine parameters when non-dominant terms are                    |     |

|      | dropped from model (with row scaling)                                                                | 52  |

| 3.13 | Sandy Bridge-EP: Modeled vs. measured runtime throughputs when non-dominant                          |     |

|      | terms are dropped from model (with row scaling)                                                      | 52  |

| 3.14 | Fitted heterogeneous machine parameters without row scaling                                          | 57  |

| 4.1  | Per-processor bounds $(W_{DP})$ ([84, 15, 21, 20, 61]) vs. the new contention bounds                 |     |

|      | $(W_{DP}^{link})$ on a d-dimensional torus for classical linear algebra, fast matrix multiplication, |     |

|      | and the $O(n^2)$ n-body problem.                                                                     | 66  |

| 4.2  | Torus dimensions so that communication cost is either always contention bound ( $d \leq$             |     |

|      | $D_1$ ) or never contention bound $(d \ge D_2)$ for a selection of matrix multiplication al-         |     |

|      | gorithms. The assertions regarding the last three algorithms are under some technical                |     |

|      | assumptions / conjecture, see [20]                                                                   | 68  |

| 5.1  | Per-processor bounds $(W_{DP}^{HBL})$ ([45]) vs. the new contention bounds $(W_{DP}^{linkHBL})$ on a |     |

| 5.1  | d-dimensional torus for programs that reference arrays                                               | 92  |

|      | <i>a</i> -dimensional torus for programs that reference arrays                                       | 92  |

| 6.1  | Description of Xeon 2650-based and future distributed parallel machines                              | 109 |

| 6.2  | Parameters derived from machine descriptions                                                         | 110 |

| 7.1  | Intel Xeon-based distributed parallel baseline machine                                               | 122 |

| /.1  |                                                                                                      | 133 |

| Energy efficiency terms for several problems (all are measured in the same units, |

|-----------------------------------------------------------------------------------|

| namely joules/flop)                                                               |

| Additional model values                                                           |

| Processor parameters                                                              |

| Network adaptor and cable parameters                                              |

| DRAM parameters                                                                   |

| Parameters for minimal $C_{job}$                                                  |

|                                                                                   |

#### Acknowledgments

Thanks to my advisor, Jim Demmel, for his support and mentorship over the past six years. Jim's experience and creativity have been extremely helpful in the development of my own research process and I look forward to his continued insight into mathematical problems in the years to come. Also thanks to my co-adviser, Tarek Zohdi. Tarek has been an excellent technical reference, as well as a point of stability and perspective regarding the graduate school experience. Example: "Thesis? Once you have a topic, just start writing something up...the process of producing tends to fill in the rest". Without Tarek's support, I would have probably gone a bit squirrely several years ago. Thanks Jim and Tarek!

Many thanks to Grey Ballard and Oded Schwartz for their insight and support on several projects. Both Grey and Oded are brilliant, patient researchers and always willing to carefully walk through a technical challenge. I wish them the best of luck in their burgeoning academic careers, and I'm excited to hear of great things from their continuing research. Thanks also to other Parlab/ASPIRE students that have been extremely helpful: Michael Anderson, Vasily Volkov, Benjamin Lipshitz, among many others.

I'd also like to extend my thanks to Kathy Yelick and Sam Williams of UC Berkeley and Lawrence Berkeley National Laboratory for their technical insight and support. Kathy is an amazing resource regarding the state of high-performance computing technology and I've yet to find a computer architecture that Sam is unable to tune. Also thanks to Harsha Simhadri for his insight into different theoretical approaches to modeling machine communication.

As this thesis has required a bit of hardware knowledge, I'd like to thank David Sheffield, Yunsup Lee, Andrew Waterman, Scott Beamer, Brian Zimmer and Ben Keller for putting up with my novice questions regarding various architectural and device-level concepts. David, Brian and Ben have also been willing to spend a significant amount of time making my life a bit easier, from tweaking build infrastructures to soldering leads.

I've been continually amazed by the quality of the support staff in the UC Berkeley EECS department and Parlab/ASPIRE. Kostadin Ilov has spent many hours moving, rebooting, reinstalling and hacking various machines on my behalf, all with a joke and a smile. Thanks also to Roxana Infante and Tamille Johnson for tirelessly handling my various "crises": from ordering parts, to missing registration deadlines, to supplying Advil. The CS graduate student advisors, La Shana Porlaris and Xuan Quach, also deserve thanks for their support in wading through the morass of paperwork required to update schedules, add a designated emphasis, or change a grade.

My friends at Intel Corporation have been exceptional resources and mentors as I've developed as a student and researcher. Special thanks to Mark Rowland and Gans Srinivasa for their mentorship, Ian Steiner for his prowess of all things IA and Hugh Caffey for his insight into Intel's performance counter infrastructure. Also, thanks to the other Intel employees that helped make my two summers interning in Hillsboro productive and insightful.

Thanks to my parents, sister Rachel, and other family members that have supported me throughout classes, exams, prelims, quals, etc. Special thanks to my boyfriend, Jade Donigan, for also putting up with my regular neurotic moments over the last several years. Finally, thanks to all the friends and colleagues that have provided support and wisdom over the years. I'm flattered and humbled to have had the chance to interact with such amazing people during my time at Berkeley.

Research partially funded by DARPA Award Number HR0011-12-2-0016, the Center for Future Architecture Research, a member of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA, and ASPIRE Lab industrial sponsors and affiliates Intel, Google, Nokia, NVIDIA, Oracle, and Samsung. Any opinions, findings, conclusions, or recommendations in this paper are solely those of the authors and does not necessarily reflect the position or the policy of the sponsors.

## Chapter 1

## Introduction

### **1.1 Communication Now Dominates Performance Costs**

Historically, algorithm developers have focused on asymptotically minimizing the number of floating point operations (flops) required to execute a computational problem. If floating point costs dominate the computation, this is a viable approach to increase performance. However, many current computational kernels only attain a small fraction of the peak floating point capability of the machine and are constrained by the bandwidth and latency characteristics of the memory subsystem [9]. We refer to the traffic between levels of the memory hierarchy as communication, and note that reducing communication traffic allows for an algorithm to potentially attain a higher fraction of the machine's peak floating point rate (see the Roofline model [148] for more details). Unfortunately, the performance gap between off-chip communication bandwidth and latency currently exceeds the cost of a floating point operation by an order of magnitude or more, and the disparity is increasing with time [121]. This communication bottleneck exists across the entire spectrum of computing, from datacenters to embedded devices, and suggests a need for new classes of algorithms that focus on minimizing communication costs (which may also include synchronizations in parallel codes), as opposed to floating point operations.

Indeed, a rapidly-evolving field of algorithm research addresses the problem of communication costs. Prior to the development of optimal algorithms, attainable lower bounds on the amount of communication required to solve a computational problem must be considered. Starting with foundational work by Hong, Kung and others, there are known lower bounds on the amount of communication required for specific algorithms [86, 84]. More recently, Ballard et al.[15] presented generalized communication lower bounds for many problems in dense and sparse linear algebra (as well as a few graph problems). These communication lower bounds were then expanded to Strassen and Strassen-like algorithms [20, 98] as well as an even larger class of problems [45] via a generalization of the argument presented within [15]. From these lower bounds, it was discovered that many existing algorithms were not communication-optimal and many new optimal algorithms were created. For example, new communication-optimal algorithms have been developed for matrix-matrix multiplication [126], LU [126], QR [15] and Cholesky [14] factorizations,

matrix-powers computations [76, 111], tensor contractions [127] and the  $O(n^2)$  n-body problem [61], among others. This communication optimality may come at the cost of additional flops, as in the case of certain Krylov subspace computations [76], or via the use of additional memory as in 2.5D matrix-matrix multiplication [126]. Implementations of many of these algorithms have been able to attain speedups on various machines. An introduction and overview of these results for linear algebra can be found in [13].

## **1.2** Energy Efficiency at the Algorithm Level

While the bandwidth and latency constraints may result in decreased floating point throughput (measured in Gflop/s), off-socket communication also costs a significant amount of energy relative to the energy cost of a floating point operation. Akin to the runtime gap between flops and communication, the energy gap between performing a floating point operation and moving a word of memory off-socket is at least an order of magnitude [43]. This issue has been addressed by device engineers and hardware architects extensively (see [89] for a review of architectural techniques to reduce energy consumption), but until recently has not received significant interest from the algorithm and application development community. Previous research into energy-efficient algorithms was mostly focused on maximizing battery life within distributed sensor networks [153, 42, 154]. More recently, researchers have begun efforts to extend the throughput roofline model of [148] to energy [44] and develop benchmarks to characterize the energy/operations characteristics of machines running various workloads [43, 28, 91]. Additional research has attempted to develop approaches to co-tuning new hardware and software implementations for increased efficiency [110, 49, 136, 119], and such research is gaining traction in both industry and government.

## **1.3** Thesis Goals and Contributions

This thesis adds to the growing body of work on energy efficiency by considering the impact of algorithmic changes to runtime and energy consumption. This is accomplished by combining communication bounds with models of machine behavior to construct lower bounds on the runtime and energy required to compute a problem of a given size. Such lower bounds are then used to analyze the impact of improvements in processor hardware parameters and the amount of extra memory utilized by certain algorithms. We also present new communication lower bounds for a heterogeneous machine model, and also describe communication-optimal algorithms for dense matrix-matrix and matrix-vector multiplication within heterogeneous processors.

In this thesis, we explicitly focus on desktop and server platforms, as these are easier to measure with low-cost equipment and often have relatively homogeneous hardware designs when compared to handheld and embedded devices. Also, these classes of machines tend to have a relatively small and consistent set of key energy-consuming components and lend themselves to theoretical analysis. We will argue that on the timescale of seconds, the runtime and energy characteristics of these classes of machines can be reasonably described via simple linear models that consider

#### CHAPTER 1. INTRODUCTION

processor, memory and static costs. Furthermore, we argue that most scientific applications can be decomposed into regions of constant arithmetic intensity and power that correspond to the execution of computational kernels. While not within the scope this this document, we believe that this approach is applicable to other classes of machines, such as mobile devices, with different model constructions.

The key contributions of this thesis are as follows:

- We present empirical evidence that at the application level and within a given level of the memory hierarchy, the energy consumption of computational kernels is predicable with linear models that comprise a handful of terms (Chapter 3).

- Via such models, we present non-trivial lower bounds on the runtime and energy required to execute algorithms on sequential and distributed parallel machine models. These bounds build upon recent developments in communication lower bounds and communication-optimal algorithms. In particular, we focus upon the problems of dense classical  $O(n^3)$  and Strassen matrix-matrix multiplication, dense and sparse matrix-vector multiplication, and the  $O(n^2)$  n-body problem (Chapter 4).

- We present runtime and energy bounds on a model of heterogeneous processing, as well as new algorithms for heterogeneous dense matrix-matrix and matrix-vector multiplication that have energy and runtime costs that are provably optimal (Chapter 4).

- We extend energy bounds for individual algorithms to a large class of programs that access arrays via affine expressions of the iteration variables (Chapter 5).

- We describe an algorithm that is provably optimal for a subset of such problems on distributed parallel machines, and show that a region of perfect strong scaling with constant energy exists as the algorithm utilized additional memory to reduce communication volume (Chapter 5).

- We use these bounds to explore the potential runtime and energy efficiency tradeoffs that occur by using additional memory to reduce communication in the presence of various constraints, such as runtime or energy limits (Chapter 6).

- Via our new Cityscape model, we propose a method to generate constraints on hardware parameters so as to attain a target level of energy efficiency for a large class of algorithms (Chapter 7).

- We show that energy and runtime bounds can be used to approximate the financial cost per job, and also optimize machine hardware according to that metric (Chapter 7).

## **1.4 Thesis Organization**

The content of this thesis is divided into a number of chapters. In Chapter 2, we provide an overview of power and energy consumption on modern desktop and server platforms, and argue

#### CHAPTER 1. INTRODUCTION

that the energy consumption of such machines is due to the activity of a small number of key hardware components. We also argue that certain characteristics of many scientific applications aid an attempt to model energy consumption and runtime via linear models to a level of granularity sufficient for algorithm developers.

Chapter 3 describes the computational problems specifically targeted for analysis within this work, and also presents models for the runtime and energy of sequential, distributed parallel, and heterogeneous machines. Chapter 3 then describes the use of performance counters to measure memory traffic and includes evidence that linear models for runtime and energy are adequate for algorithm and hardware developers to gain a high-level idea of the runtime and energy efficiency of an algorithm. Chapter 4 presents energy bounds for specific algorithms on sequential, distributed parallel, and heterogeneous classes of machines, and Chapter 5 extends these algorithm-specific results to generalized energy bounds on a much larger class of computational problems. Chapter 5 also shows that a communication-optimal algorithm for a subset of this larger class of problems is able to halve runtime by doubling the number of processors on a fixed problem size. This perfect strong scaling in runtime is attained with constant energy by utilizing additional memory to offset communication volume.

In Chapter 6, we apply the energy and runtime bounds of Chapters 4 and 5 to a set of questions that are potentially useful to algorithm developers. In particular, we demonstrate how the use of additional memory to offset communication affects energy efficiency in the presence of various constraints on total runtime and energy, among others. Chapter 7 extends this concept by describing ranges of hardware parameters that attain a target level of energy efficiency or the optimal financial cost per job. Finally, in Chapter 8 we conclude and discuss directions for potential future research. Code, data and analysis for the results presented within this dissertation can be found at https://github.com/agearh/dissertation.git.

## Chapter 2

## **Energy Consumption and Computing**

As mentioned previously, this document utilizes machine models to bound the amount of energy consumed during the execution of an algorithm. These bounds are then used to provide insights into algorithm performance and future hardware design. To assist in doing this, we make four assumptions about the behavior of scientific applications, which will be justified via a combination of original and existing research:

- Assumption 1: Scientific applications can be divided into regions of execution that correspond to key computational kernels of the application. We refer to these regions of execution as *phases* in this document.

- Assumption 2: At the timescale of seconds, power consumption is relatively constant during execution of a phase.

- Assumption 3: The primary energy consumers on desktop and server nodes are processor execution units, static random-access memory (SRAM) caches and dynamic random-access memory (DRAM) when considering problem sizes that fit within main memory.

- Assumption 4: When discussing distributed machines, the energy of current internode networks may not scale with utilization and is thus another static term. We will derive a second distributed parallel machine model to reflect this situation in Chapter 3.

In this chapter, we argue for the applicability of these assumptions to many scientific applications by both citing previous research and presenting our own evidence. We begin by discussing tradeoffs between power and energy (Section 2.1) and then argue that many scientific applications demonstrate phase-based power behavior that corresponds to the execution of computational kernels (Section 2.2). Finally, we discuss key consumers of energy on desktops and server nodes (Section 2.3) as well as distributed parallel machines (Section 2.4).

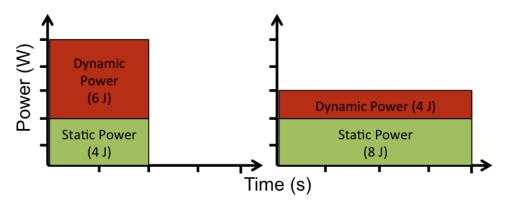

Figure 2.1: Tradeoff between minimizing energy or power

## 2.1 Power vs. Energy

Before discussing the assumptions presented earlier, a brief discussion of the relationship between power and energy is warranted. First and perhaps foremost in this discussion, digital circuits can be considered as devices that convert electrical energy into an application-specific output with some loss which is represented as dissipated heat. The issues of reducing energy consumption and power within computing devices are clearly linked as energy is the integral of power with respect to time, often represented simply as E = HT where H is the average power over the time period T. In this document, we primarily limit our discussion (unless otherwise noted) to the problem of minimizing overall energy consumption during the execution of an algorithm. This is a useful problem for both handheld devices as well as datacenters, where the goals are to extend battery life and reduce operating costs, respectively. As a common example, the most energy-efficient means of computation may be to use a large amount of power to finish quickly and go to idle. Such an idea is called "race-to-halt", and will be discussed in greater detail later in this document. On the other hand, minimizing power consumption may involve solving the same problem at the slowest rate possible. In this situation, the power is minimized while the overall energy required to complete the computation may be suboptimal. Figure 2.1 illustrates this situation as two runs of the same problem at different processor performance settings. Note that in Figure 2.1, the first run of the algorithm consumes 10J of energy and 5W of power for two seconds. The other run (perhaps at a lower clock frequency and processor voltage) consumes 12J of energy and 3W of power over four seconds. From the standpoint of minimizing energy, the first run is superior as the workloaddependent energy consumption (the dynamic energy) dominates the workload-independent energy consumption (*static energy*). We will expand upon the concepts of static and dynamic energy later in this chapter, and will use this distinction to define models of energy in Chapter 3.

### **2.2** Phase-based Execution of Applications

In this thesis, we assume that most scientific applications are composed of a set of key computational kernels that are required for the problem to be solved in a specific order along a critical path. Each kernel may then be optimized independently of the other kernels in the application. This application structure roughly corresponds to the Bulk-Synchronous Parallel (BSP) model of parallel execution first proposed by Valiant [139], but is more general as no assumptions are made about hardware or synchronization between phases. We believe that by improving the efficiency (both in throughput and energy) of a small set of application kernels, such benefits can be applied to a large number of scientific codes. This view of scientific computing echoes the conclusions of the Berkeley View on Parallelism [9] which surveyed a large number of scientific application domains.

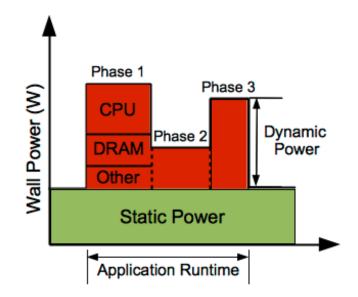

This work focuses on the energy and runtime costs of application kernels that execute at time scales that range from tenths of a second to minutes. At this coarse level of granularity (many thousands of clock cycles), we are not concerned with the ability to estimate or measure power to an extremely high level of fidelity (unlike chip designers or architects). At this time scale, we observe that many applications demonstrate *phase-based* power consumption behavior. By this, we mean that the power for an algorithm tends to stay relatively constant during different portions of its execution timeline and note that power phases typically occur during the execution of a kernel within the application. In Figure 2.2, we depict the wall power<sup>1</sup> trace of a machine running a generic application with three phases of execution. Note that Figure 2.2 shows a common, constant level of static power that does not depend on application behavior. The red portions of the figure depict the dynamic energy of the algorithm in three phases, each of which represents a region of constant wall power during its runtime. Later in this chapter, we will also show evidence that the key consumers of energy on desktops and server nodes are processor execution units, caches, and main memory. In Chapter 3 we will present empirical evidence suggesting that multiplying this phase-constant power by the runtime of a phase is an accurate way of approximating the energy consumption of a kernel for many applications.

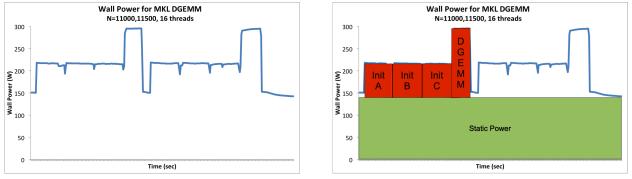

To support the diagram of a generic wall power trace shown in Figure 2.2, we recorded the power of a dual-socket Sandy Bridge-EP server running a benchmark that allocates and initializes three square matrices prior to running the parallel double-precision dense matrix-matrix multiplication (DGEMM) implementation found in Intel's Math Kernel Library (MKL) version 11.1. This wall power trace is shown in Figure 2.3 and has a time axis that ranges to approximately 330 seconds. In the power trace, we see the benchmark executed twice for different matrix sizes selected to fit within the machine's main memory (thus, little disk access occurs and the problems are unable to fit within last level cache). To correlate phase and kernel behavior, we annotated the initialization and computation phases of the benchmarks with timestamps that were then aligned with the sample times from a meter that measures wall power. For clarity, the Linux *sleep* command was used to impose 10 second intervals between the execution of each of the different-sizes problems.

In Figure 2.3, we note that the current static power of the machine is approximately 140W and

<sup>&</sup>lt;sup>1</sup>Wall power is the total power consumed by the machine, including power supply inefficiency.

Figure 2.2: Typical Scientific Code Power Trace

(a) Wall power for two runs of DGEMM benchmark

(b) Wall power with phase annotations

Figure 2.3: Power phases of matmul benchmark on Sandy Bridge-EP

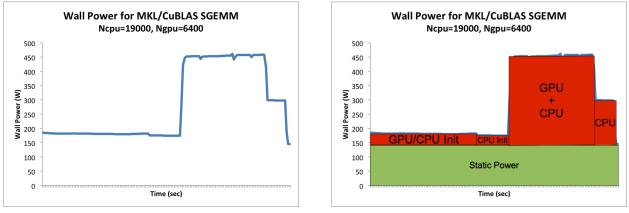

(a) Wall power for a run of heterogenous SGEMM benchmark

(b) Wall power with phase annotations

Figure 2.4: Power phases of heterogeneous matmul on Sandy Bridge-EP and Nvidia K20

that the machine while running *sleep* consumes approximately 150W. Between these idle periods, four power phases can be clearly seen: 3 of an identical length between approximately 210-220W, and one phase between approximately 290-300W. Via the timestamps, we observe that these four power phases correspond exactly to the three parallel initialization phases of the benchmark followed by the actual matrix-matrix multiplication operation itself. This result supports the structure of the generic wall power trace in Figure 2.2. Further, we also note that power appears to be relatively constant across problem sizes within a given level of memory.

This concept of power phases can be extended further when multiple heterogeneous devices are executing during an application run. In Figure 2.4, we see an example of an annotated wall trace of a benchmark that performs single-precision dense matrix-matrix multiplications (SGEMMs) on both a host machine (CPU) and a graphics processing unit (GPU). This wall power trace was generated by running Algorithm 7 of Section 3.4 with gpuInner = 50, gpuOuter = 5, hostInner = 2 and square problem sizes of  $n_{cpu} = 19000$  on the host and  $n_{gnu} = 6400$  on the GPU. Note that with two devices executing, the constant power phase of the GPU overlaps with the power phase of the host/CPU. In Chapter 3, we discuss the implications for modeling energy consumption with multiple devices.

## 2.3 Key Consumers of Energy on Desktops and Server Nodes

As mentioned earlier in the chapter, we argue that the key hardware components that dominate dynamic energy consumption on desktops and servers are:

- Processor execution units (eg. floating point units, branch predictors, or reorder buffers)

- Static random-access memory (SRAM)

• Dynamic random-access memory (DRAM)

The dominance of these few components is supported by research that directly instruments hardware components for power, and then considers energy consumption while running benchmarks. Other researchers have devoted significant effort toward direct measurement of desktop and server components via specialized instrumentation devices, in particular PowerPack [66] and PowerMon [26]. Both projects involve inserting current sense resistors (CSRs) into wires between the power supply and machine devices to measure current (and thus power, as wires are of a known voltage and power = current \* voltage). Thus, PowerPack and PowerMon avoid measurement of power supply losses while creating the new problem of differentiating component power from various supply wires (e.g. the ATX power supply specification defines a 20-wire input from the power supply to motherboard on desktop machines [10]). Both PowerPack and PowerMon address this issue via a set of benchmarks that attempt to isolate component power. PowerPack, originating from Virginia Tech, uses a commodity National Instruments data acquisition (NI-DAQ) device to measure voltage drops across sense resistors. This device has the advantage of being widely available with a stable software stack, but has a high per-unit cost. To address this limitation, the PowerMon project utilizes a custom monitoring breadboard to collect data samples. The design for this board is freely available, and it was designed to allow for cheap instrumentation of distributed systems. PowerPack [66] and PowerMon [26] both argue for the dominance of processor and DRAM energies on desktop and server nodes, and this is further supported by the data reported in studies that use PowerPack [101, 145, 103] for related research. The dominance of processors and main memory (DRAM) over components such as disks is also argued by Brown and Reams [37]. The authors of [27] take this argument further, and argue for an increasing fraction of total distributed machine energy consumed by node DRAM with successive reductions in device feature sizes.

Processor execution units, SRAMs and DRAMs each share a common underlying technology, that of complementary metal-oxide semiconductor (CMOS) logic. We have argued that research supports the dominance of these components with regard to dynamic energy, but also acknowledge that the static power of other machine components (such as power supply inefficiency, motherboards, and hard drives) may contribute a large portion of overall static energy consumption. We consider these devices later in this chapter. In the next section, we discuss dominant sources of energy consumption in CMOS and provide references for readers interested in further details.

### **Energy Consumption in CMOS Logic**

Manufacturers utilize CMOS technology to implement digital circuits due to additional noise resistance and reduced energy consumption over other logic classes such as N-type metal-oxidesemiconductor (NMOS) or Transistor-transistor logic (TTL) (see classic text by Glasser and Dubberpuhl [68] for more details). CMOS utilizes paired p-type and n-type MOS transistors (pMOS and nMOS transistors, respectively) in a manner such that current does not flow from supply  $(V_{dd})$ to ground  $(V_{ss})$  once the output signal has stabilized. pMOS and nMOS transistors are both examples of field effect transistors (FETs), and as such can be considered to have 4 terminals: source,

Figure 2.5: CMOS inverter with n-type (nMOS) and p-type (pMOS) transistors indicated

drain, gate and body. In this discussion, we ignore the body terminal as it is typically connected to the source.

In pMOS transistors, current flows from source to drain when there is a negative potential difference between gate and source. Inversely, current flows within nMOS transistors when there exists a positive potential difference between source and drain. Charge begins to flow from source to drain once the potential difference reaches a specific threshold voltage ( $V_{th}$ ). CMOS logic builds logical gates, which implement simple binary functions from paired nMOS and pMOS transistors. As a simple example of a common CMOS gate, an inverter circuit is shown in Figure 2.5.

Figure 2.5 shows an nMOS and a pMOS transistor. When the input signal is HIGH, the pMOS is OFF and the nMOS is ON. This allows the nMOS transistor to pull down the output signal toward  $V_{ss}$ . On the other hand, if the input signal is LOW, the nMOS is OFF and the pMOS pulls the output up toward  $V_{dd}$ .

The energy consumption of CMOS circuits,  $E_{logic}$ , can be defined as the summation of three classes of terms: dynamic gate energy, static gate leakage, and interconnect energy. Dynamically,  $E_{logic}$  is composed of two terms: the switching energy  $E_{switch}$  and the short energy  $E_{short}$ . Static energy consumption can be approximated via a single term: leakage, or  $E_{leak}$ , and we express interconnect energies as a single term ( $E_{wire}$ ). We express  $E_{logic}$  as the sum of these terms in Equation (2.1).

$$E_{logic} = E_{switch} + E_{short} + E_{leak} + E_{wire}$$

(2.1)

**Dynamic Transistor Energy**  $(E_{switch} + E_{short})$  Because transistors can be regarded as parallelplate capacitors, a state transition charges or discharges electrical energy. This process is one of the key components of energy consumption within CMOS circuits, and is represented by  $E_{switch}$ in Equation 2.1. Due to its relationship with capacitor charge/discharge cycles,  $E_{switch}$  can be represented via a capacitance expression

$$E_{switch} = \sum_{i=1}^{N_g} n_i c_i V_{dd}^2$$

(2.2)

where  $N_g$  is the number of gates,  $n_i$  is the number of times gate *i* toggles during computation,  $c_i$  and  $V_{dd}$  describe the capacitance of gate *i* and the circuit supply voltage, respectively [69]. Note that this discussion treats gates in the same manner as transistors. We do this as gates are collections of transistors, and at a coarse level are larger capacitors themselves. From Equation (2.2), we see that reducing  $V_{dd}$  has a quadratic impact upon energy consumption. Furthermore, capacitance  $c_i$  is proportional to the size of the gate and can be represented by

$$c_i = \hat{c}_i W_i L_i \tag{2.3}$$

where  $\hat{c}_i$  is the capacitance/area of the gate oxide,  $W_i$  is the gate width and  $L_i$  is the gate length.

In addition to  $E_{switch}$ , dynamic energy in CMOS logic is also consumed by the momentary connection between  $V_{ss}$  and  $V_{dd}$  as the paired nMOS and pMOS transistors shift between states. This is called the short-circuit current, and is represented by  $E_{short}$  in Equation 2.1. According to Veendrick [141],  $E_{short}$  can be minimized (to  $\leq 20\%$  of  $E_{logic}$ ) by matching input and output rise and fall times. Further, as noted in [114], decreasing the ratio of  $V_{th}$  to  $V_{dd}$  can also result in a 20% contribution of  $E_{short}$  to  $E_{logic}$ . As  $E_{short}$  does not directly impact the following analysis and is primarily of concern to logic designers, we do not discuss its contribution further.

Leakage Energy  $(E_{leak})$  The static power dissipation, or leakage, of CMOS gates is represented by the  $E_{leak}$  term of Equation 2.1. While  $E_{leak}$  can be partitioned into at least eight different components [90], we will be primarily concerned with sub-threshold leakage (or weak inversion leakage). Sub-threshold currents often dominate amongst leakage components [90, 113]. Therefore, in this work the term "leakage" refers to the sub-threshold component of the overall leakage current of a device. For a more detailed analyses of leakage, we refer readers to [113] and [117].

In an ideal world, the dynamic switching component  $(E_{switch})$  of a CMOS circuit would be the only consumer of energy. For many years, reductions in  $V_{dd}$  were combined with feature size reductions to maintain a relatively constant power density and increased clock frequency (which translates to greater potential instruction throughout). Called "Dennard Scaling" after Robert Dennard's observation in 1974 [57], this practice is no longer utilized as reductions in  $V_{dd}$  require corresponding reductions in  $V_{th}$  to maintain clock frequency increases via reductions in circuit delay[69]. To see how this has become problematic, we must first define the sub-threshold current,  $I_{leak}$ . According to Helms, Schmidt and Nebel [72], this current is

$$I_{leak} = KV_{th}^2 (W/L) e^{(V_{gs} - V_{th}/(nV_T))} (1 - e^{-V_{ds}/V_T})$$

where n and K are technology parameters, W and L and the width and length of the gate,  $V_{ds}$  is the drain-source voltage and  $V_{gs}$  is the gate-source voltage.  $V_T$  is the thermal voltage, which is proportional to temperature. Note that due to the exponential relationship between threshold voltage and leakage current, a small decrease in  $V_{th}$  results in large increase in  $I_{leak}$ . It is this relationship that has effectively eliminated Dennard scaling, and contributed to the development of multicore processors that substitute increases in clock frequency with parallelism, essentially pushing the onus of performance onto algorithm, software and compiler engineers.

At the level of an entire CMOS circuit, the total leakage energy  $E_{leak}$  is the sum of each gate's leakage energy

$$E_{leak} = \sum_{i=1}^{N_g} I_{leak_i} V_{dd} T_c$$

where  $I_{leak_i}$  is the leakage current of gate *i* and  $T_c$  is the cycle time. In the energy models we define in Chapter 3,  $E_{leak}$  is merged into a single term with other static energy sources, such as disks. More-detailed models could be used to explicitly expose this term for analysis (see Section 7.4 for ideas on how to construct such models).

**Interconnect Energy** ( $E_{wire}$ ) Similar to gate energy, interconnects consume energy via two components: switching energies and leakage. That is,

#### $E_{wire} = E_{wireSwitch} + E_{wireLeak}.$

The expression for switching energy of wires,  $E_{wireSwitch}$ , can be represented as a capacitance expression in an analogous manner to  $E_{switch}$ . Like  $E_{switch}$ ,  $E_{wireSwitch}$  is proportional to wire size and and quadratically dependent on voltage. On the other hand, wire static losses are inversely proportional to wire size as  $E_{wireLeak}$  is dominated by resistance losses.

In CMOS circuits, pMOS and nMOS transistors are connected to form gates, gates are connected to form circuit blocks, and blocks are connected to build larger components, such as floating point units, or caches. These larger components are then linked to build processors and systems. As blocks are combined into larger components and structures, interconnect lengths increase, but the overall number of such wires decreases. The relationship between wire length and frequency can be approximated via the power-law relation described by Rent's rule [95] and the work of Donath [59, 60]. Furthermore, Sylvestor and Keutzer [135] observed that interconnects occur in two classes: local wires that scale with technology generations, and global wires that do not. This relationship between wire and technology scaling was further described in the seminal work by Ho, Mai and Horowitz [75]. Local wires can be modeled effectively via Rent's rule, but global interconnects may use different approaches that are dependent on implementation [100]. Global wires (typically clock trees or buses) present a timing bottleneck (as delay increases quadratically with wire length), which can be mitigated via such techniques as larger wires or the use of inverter chains as repeaters, but such techniques trade delay for increased dynamic and static wire energy consumption [8].

As they do not scale with process technology, global interconnects represent a significant and probably increasing fraction of system energy. Nir et al.[105] note that processor interconnect power is approximately 50% of total dynamic power, with this half split evenly between local and global wires on a testbed processor. In 2002, Basu et al.[25] observed that the off-chip bus of an embedded processor consumed 9.8-23.2% of system power, and argue that energy could be saved via fewer wire activations and then reducing the number of bit transitions within these active wires. This idea of energy-efficient global wire behavior has been further explored for both on-chip [99] and off-chip [134, 133] interconnects. Much of the existing work to reduce the time and energy

costs of long wires has been focused at the level of hardware design and architecture. While this approach is certainly insightful, it begs the question of any communication reduction to be gained at the algorithm and application level. As we will discuss in Chapter 3, the development of algorithms that perform a provably minimal amount of communication has resulted in runtime improvements on both shared and distributed-memory machines (see [13] for a survey). We hypothesize that such algorithms also reduce energy consumption, but the verification of this conjecture remains the subject of ongoing and future research. In Chapter 3, we will define energy models that include the energy and runtime cost of data movement as a combination of wire and memory energies.

#### **Other Hardware Components**

In the previous sections, we argued that the dynamic energy on modern server and desktop platforms is predominately consumed by processor packages, SRAMs (primarily caches) and DRAM and discussed the primary sources of energy consumption in CMOS logic. We here cite previous work arguing that other hardware components (such as storage drives, motherboards, fans and power supplies) represent either static or negligible dynamic contributions to total system energy consumption.