# Silicon Carbide Bipolar Junction Transistors for High Temperature Sensing Applications

Nuo Zhang

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-170 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-170.html

December 1, 2016

# Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Silicon Carbide Bipolar Junction Transistors for High Temperature Sensing Applications

by

#### Nuo Zhang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering & Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Albert P. Pisano, Chair Professor Tsu-Jae King Liu Professor Liwei Lin

Spring 2014

Silicon Carbide Bipolar Junction Transistors for High Temperature Sensing Applications

Copyright © 2014

by

Nuo Zhang

#### Abstract

Silicon Carbide Bipolar Junction Transistors for High Temperature Sensing Applications

by

#### Nuo Zhang

Doctor of Philosophy in Electrical Engineering & Computer Sciences

University of California, Berkeley

Professor Albert P. Pisano, Chair

An integrated sensing module capable of operating at high temperatures would be beneficial to a number of industrial applications, such as automotive industries, aerospace systems, industrial turbines and deep-well drilling telemetric systems. Consider industrial turbines as an example. It is important to monitor a variety of physical parameters within the hot sections of the turbines in order to increase turbine efficiency, reliability and to reduce pollution. In addition, real-time monitoring can help to detect and predict the failures of critical components in a timely fashion to reduce the maintenance costs of the systems. A high temperature integrated circuit is an important part of such systems, because it provides power management function for the energy scavenger, builds the electrical interface with MEMS-based harsh environment sensors, and amplifies the sensing signals. Therefore, it is essential to have transistors, the building blocks of integrated circuits, which can operate at high temperatures.

Silicon carbide (SiC) is a promising semiconductor for high temperature applications due to its excellent electrical and physical properties. The wide bandgap energy (3.2 eV for 4H-SiC) and low intrinsic carrier concentration allow SiC semiconductor devices to function at much higher temperatures. Moreover, high breakdown electric field (3-5 MV/cm), high-saturated electron velocity (2×10<sup>7</sup> cm/s) combined with high thermal conductivity (3-5 W/cm·°C) enable SiC devices to work under extreme conditions. There are growing interests on developing high temperature integrated circuits using SiC bipolar junction transistors (BJTs) because SiC BJTs are not as strongly affected by oxide quality as SiC metal-oxide-semiconductor field effect transistors (MOSFETs). In addition, SiC BJTs are normally-off devices and have higher transconductance compared with SiC junction field effect transistors (JFETs).

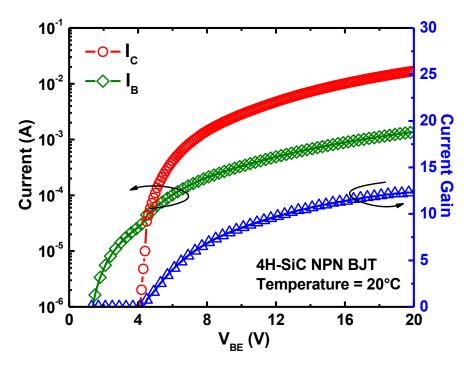

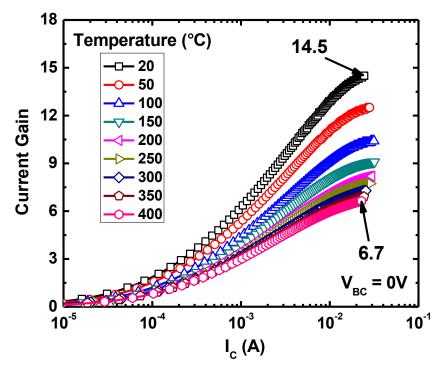

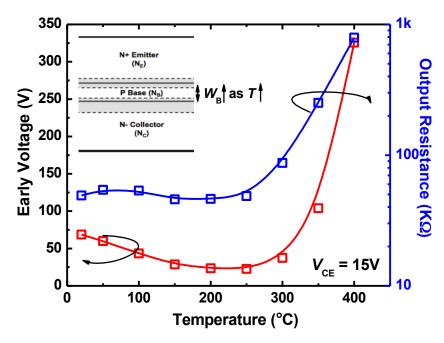

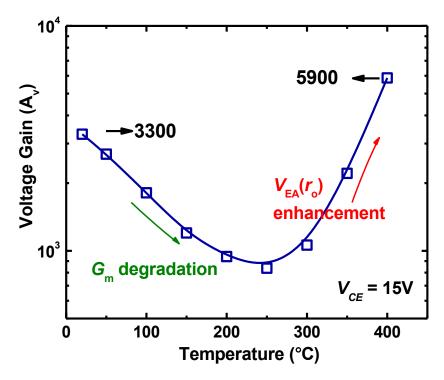

This dissertation presents comprehensive analytical and experimental results on 4H-SiC NPN BJTs capable of operating at high temperatures up to 400 °C. Comprehensive characterization including current gain, early voltage, output resistance, and intrinsic voltage gain was performed. At room temperature, the device has a current gain of 14.5 and an intrinsic voltage gain of 3300. At elevated temperatures, the intrinsic voltage gain increases to 5900 at 400 °C, although the current gain of the device is reduced to 6.7.

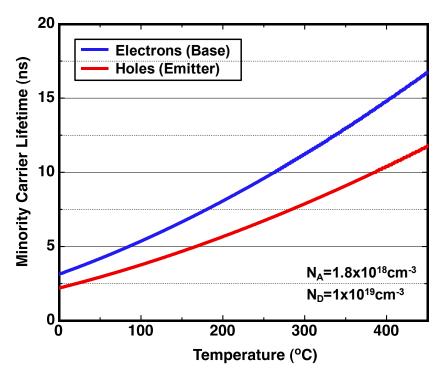

This suggests that 4H-SiC BJT has the potential to be used as a voltage amplifier at extremely high temperatures. High temperature effects of 4H-SiC are theoretically studied. The incomplete ionization effect and the temperature dependence of minority carrier lifetime are the two main competing mechanisms for the change of device performance with rising temperature. To further enhance the current gain, fabrication process can be improved for reduction of interface traps residing between SiC and the passivation oxide layer.

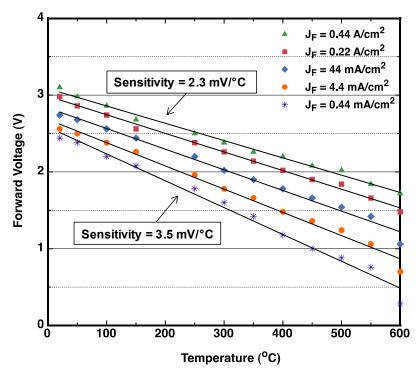

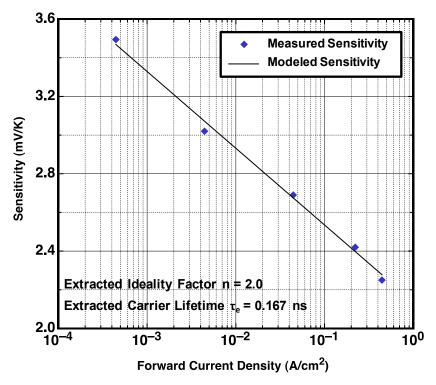

This dissertation also presents the design, fabrication and characterization of a high-performance temperature sensor based on 4H-SiC pn diode. The device shows stable operation from room temperature up to 600 °C. Under forward bias condition, the temperature sensitivity of the sensor changes from 2.3 mV/°C at a forward current density of 0.44 A/cm², to 3.5 mV/°C at a forward current of 0.44 mA/cm². Higher sensitivity can be achieved at a lower forward current level. The experimental results indicate a good agreement with theoretical analysis. These results show that the device has the potential to be integrated with supporting circuitries to build a sensing module for high temperature applications.

To my parents and my husband

## TABLE OF CONTENTS

| List of Figures                                                                          | iv  |

|------------------------------------------------------------------------------------------|-----|

| List of Tables                                                                           | vi  |

| List of Abbreviations                                                                    | vii |

| Acknowledgments                                                                          | xi  |

| Chapter 1 Introduction                                                                   | 1   |

| 1.1 High Temperature Sensing Applications                                                |     |

| 1.2 Material Properties of Silicon Carbide                                               |     |

| 1.2.1 Crystal Structure                                                                  |     |

| 1.2.2 Material Properties                                                                |     |

| 1.3 High Temperature SiC Electronics                                                     |     |

| 1.4 Fundamentals of Bipolar Junction Transistors                                         |     |

| 1.5 Thesis Organization                                                                  | 9   |

| Chapter 2 Physical Models                                                                | 11  |

| 2.1 Band Structure                                                                       | 11  |

| 2.1.1 Energy Bandgap and Temperature Dependence                                          |     |

| 2.1.2 Bandgap Narrowing                                                                  |     |

| 2.1.3 Effective Masses and Effective Density of States                                   |     |

| 2.2 Mobility                                                                             |     |

| 2.3 Incomplete Ionization                                                                |     |

| 2.4 Generation-Recombination                                                             |     |

| 2.4.1 Shockley-Read-Hall Recombination                                                   |     |

| 2.4.2 Surface SRH Recombination                                                          |     |

| 2.4.3 Auger Recombination.                                                               |     |

| Chapter 3 Microfabrication Technology of SiC Bipolar Junction Transistors                | 19  |

| 3.1 Fabrication Process Flow of SiC Bipolar Junction Transistors                         | 19  |

| 3.2 Fabrication Challenges                                                               |     |

| 3.2.1 Etching of Silicon Carbide                                                         |     |

| 3.2.2 Metallization                                                                      |     |

| 3.2.3 Surface Passivation                                                                | 29  |

| 3.3 Conclusions                                                                          | 30  |

| Chapter 4 Simulation and Characterization Results of 4H-SiC Bipolar Junction Transistors | 32  |

| 4.1 Device Structure                                                                     | 32  |

|                                                                                          |     |

| 4.2 Room Temperature Characterization of the 4H-SiC BJT             | 36 |

|---------------------------------------------------------------------|----|

| 4.3 High Temperature Effects in 4H-SiC                              | 36 |

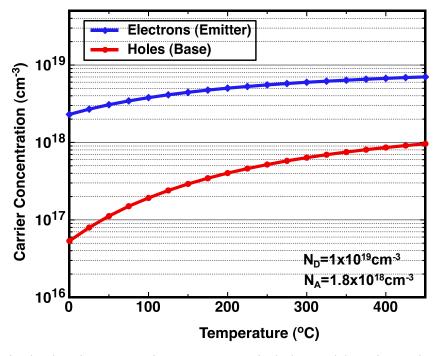

| 4.3.1 Temperature Dependence of Carrier Concentration               | 36 |

| 4.3.2 Temperature Dependence of Carrier Lifetime                    | 40 |

| 4.4 High Temperature Characterization of 4H-SiC BJTs                | 40 |

| 4.5 Effects of SiC/SiO <sub>2</sub> Interface Traps                 |    |

| 4.6 Conclusions                                                     | 46 |

| Chapter 5 Fabrication and Characterization of SiC PN Diode for High |    |

| Temperature Sensing Applications                                    | 47 |

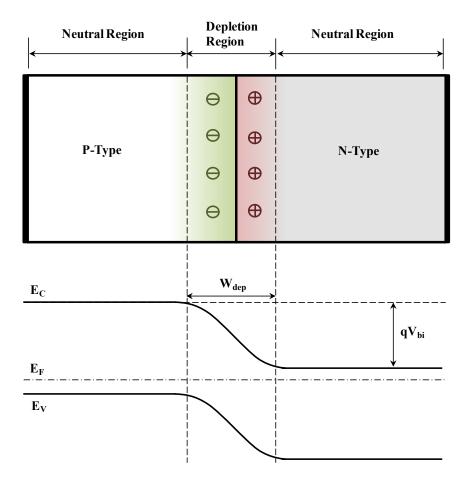

| 5.1 Fundamentals of PN Junction Diode                               | 47 |

| 5.1.1 PN Junction Electrostatics Under Equilibrium                  | 48 |

| 5.1.2 Current Conduction Mechanisms                                 | 49 |

| 5.2 Temperature Sensing Mechanism                                   | 50 |

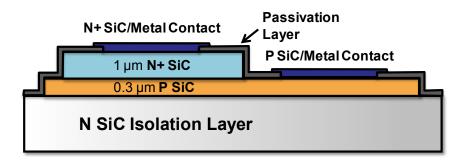

| 5.3 Sensor Structure                                                | 51 |

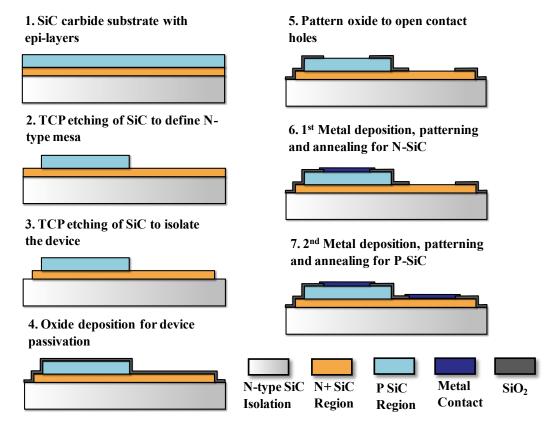

| 5.3 Fabrication Process Flow of the Temperature Sensor              | 52 |

| 5.4 Characterization Results                                        | 53 |

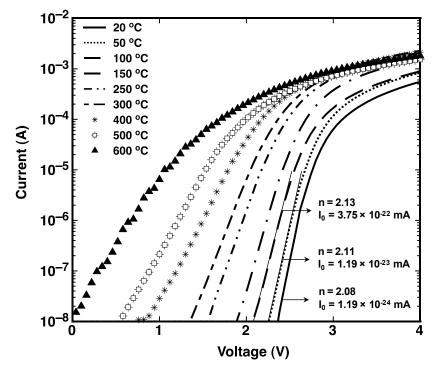

| 5.4.1 I-V Measurements at Different Temperatures                    | 53 |

| 5.4.2 Evaluation of the Temperature Sensor                          | 54 |

| 5.5 Conclusions                                                     | 56 |

| Chapter 6 Conclusions and Future Research Directions                | 57 |

| 6.1 Summary                                                         | 57 |

| 6.2 Future Research Directions                                      | 59 |

| Bibliography                                                        | 60 |

## LIST OF FIGURES

| Figure 1-1. | Tetrahedrally bonded Si-C cluster [1], [13].                                                                                                            | .4  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1-2. | Hexagonal close packing positions of Si-C bilayers [1], [15]                                                                                            | .5  |

| Figure 1-3. | Stacking sequences of Si-C bilayers along c-axis for 3C-, 4H-, and 6H-SiC [15].                                                                         | .5  |

| Figure 1-4. | Schematic of a NPN BJT biased at forward active region [34]                                                                                             | .8  |

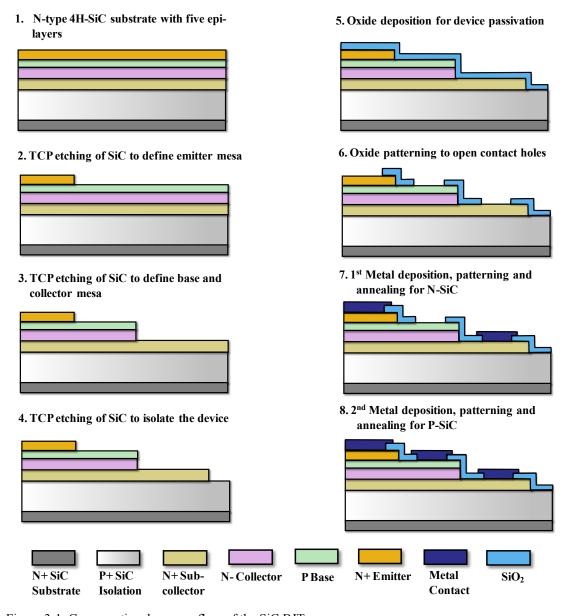

| Figure 3-1. | Cross-sectional process flow of the SiC BJT.                                                                                                            | .20 |

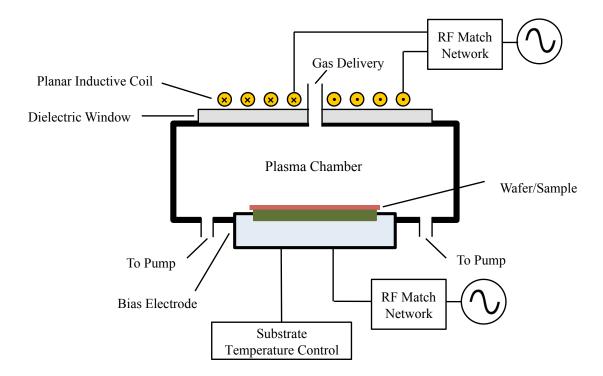

| Figure 3-2. | Schematic of TCP etching system (Lam Research) [63].                                                                                                    | .22 |

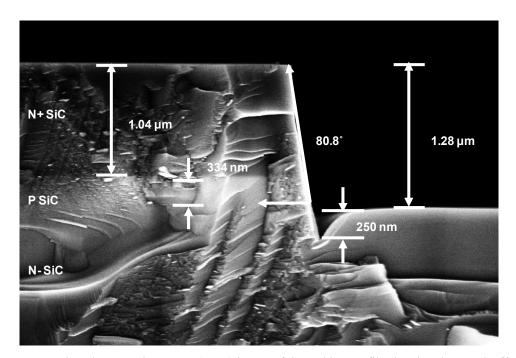

| Figure 3-3. | Scanning electron microscopy (SEM) image of the etching profile showing the trench effect.                                                              | .23 |

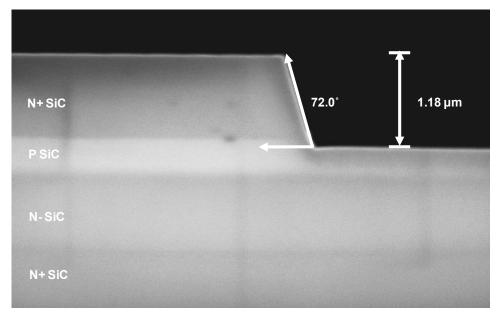

| Figure 3-4. | SEM image of the etching profile without trench effect.                                                                                                 | .24 |

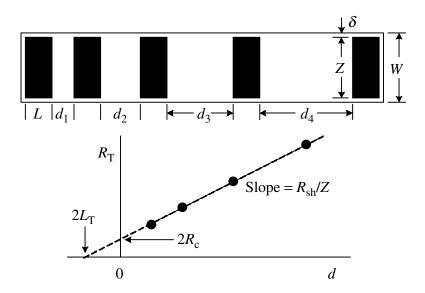

| Figure 3-5. | Schematic of a transfer length method test structure and a plot of total resistance $(R_T)$ $vs.$ contact spacing $(d)$ [72]                            | .26 |

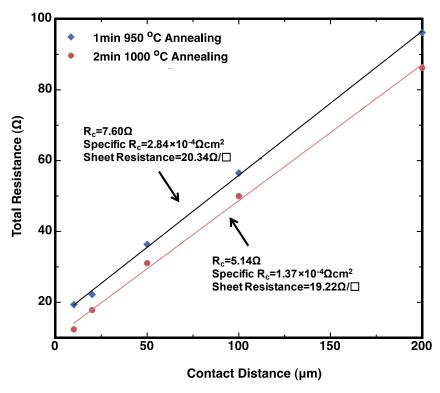

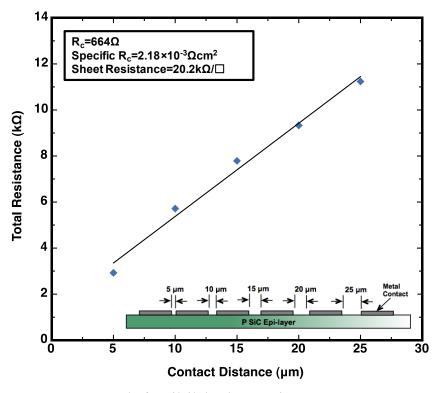

| Figure 3-7. | TLM measurement results for Ni/Ti/Al and p-type SiC contacts                                                                                            | .28 |

| Figure 3-6. | TLM measurement results for Ni and n-type SiC contacts under different annealing conditions.                                                            | .28 |

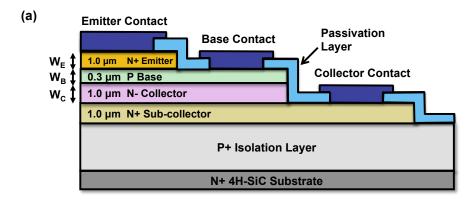

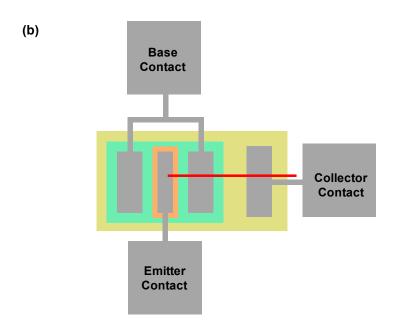

| Figure 4-1. | (a) Cross-sectional schematic and (b) schematic top view of the 4H-SiC BJT. The red line in (b) indicates the position of the cross-section in (a)      | .33 |

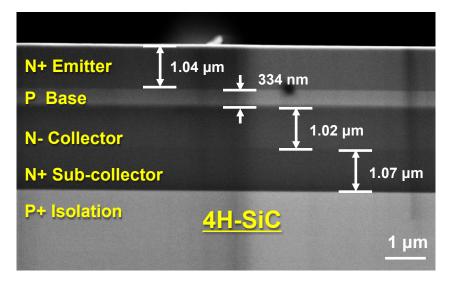

| Figure 4-2. | SEM image of the cross-section view showing the thickness of each epitaxial layer                                                                       | .35 |

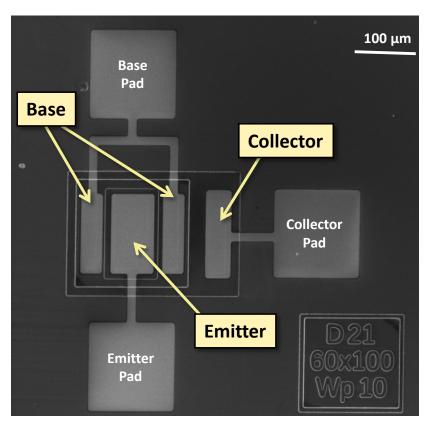

| Figure 4-3. | SEM image of the fabricated 4H-SiC BJT.                                                                                                                 | .35 |

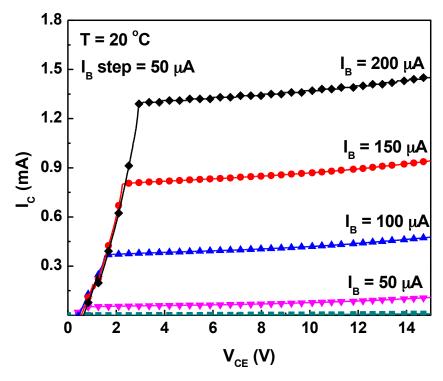

| Figure 4-4. | Measured forward output characteristics ( $I_C$ - $V_{CE}$ ) with $I_B$ from 0 $\mu$ A to 200 $\mu$ A at room temperature (20 °C).                      | .37 |

| Figure 4-5. | Measured SiC BJT base and collector current ( $I_B$ and $I_C$ ) and current gain ( $\beta$ ) $vs$ . base-emitter bias ( $V_{BE}$ ) at room temperature. | .37 |

| Figure 4-6. | Simulated carrier concentration <i>vs.</i> temperature in the base and the emitter regions.                                                             | .39 |

| Figure 4-7. Simulated minority carrier lifetime <i>vs.</i> temperature in the base and the emitter regions.                                                                                                        | .39 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

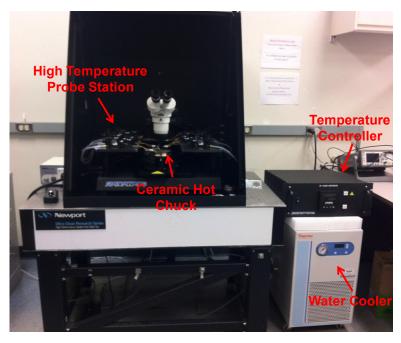

| Figure 4-8. High temperature probe station made by Signatone.                                                                                                                                                      | .40 |

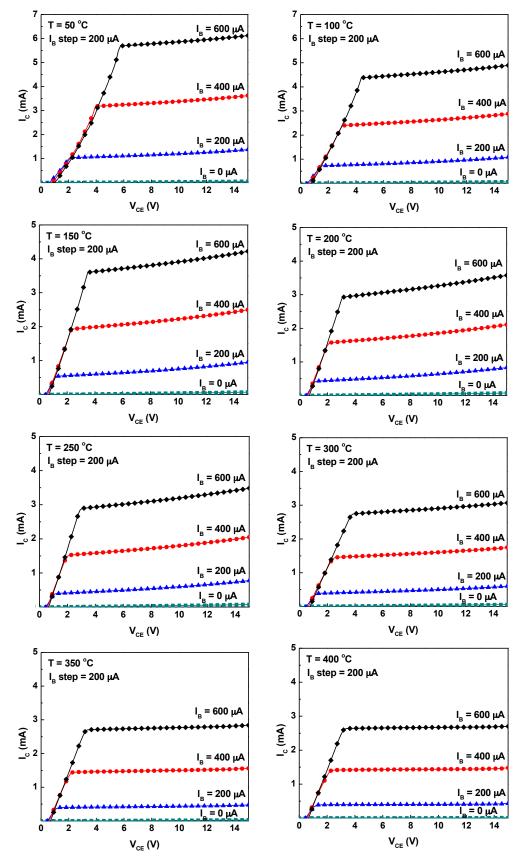

| Figure 4-9. Measured forward output characteristics at different temperatures                                                                                                                                      | .41 |

| Figure 4-10. Measured SiC BJT current gain <i>vs.</i> collector current at different temperatures (up to 400 °C).                                                                                                  | .42 |

| Figure 4-11. Measured SiC BJT early voltage ( $V_{\rm EA}$ ) and output resistance ( $r_{\rm o}$ ) vs. temperature; the inset illustrates the base width ( $W_{\rm B}$ ) widening effect at elevated temperatures. | .42 |

| Figure 4-12. Measured SiC BJT voltage gain (A <sub>v</sub> ) vs. temperature                                                                                                                                       | .44 |

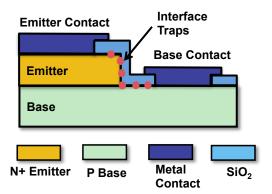

| Figure 4-13. Schematic cross-sectional view of the 4H-SiC BJT presenting where the interface traps physically reside in the device.                                                                                | .44 |

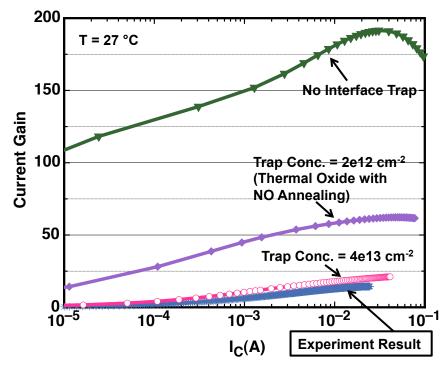

| Figure 4-14. TCAD simulation results of SiC BJT current gain <i>vs.</i> collector current with different trap concentrations.                                                                                      | .45 |

| Figure 5-1. Conceptual pn junction and equilibrium energy band diagram.                                                                                                                                            | .49 |

| Figure 5-2. Cross-sectional schematic of the temperature sensor based on 4H-SiC pn diode.                                                                                                                          | .51 |

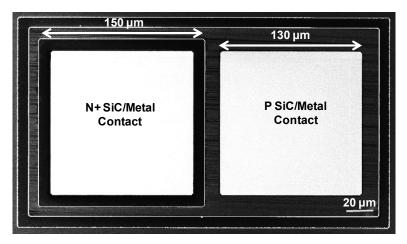

| Figure 5-3. SEM image of the fabricated temperature sensor based on 4H-SiC pn diode.                                                                                                                               | .52 |

| Figure 5-4. Cross-sectional process flow of the temperature sensor.                                                                                                                                                | .53 |

| Figure 5-5. I-V measurement of the 4H-SiC pn diode based temperature sensor at different temperatures (20 – 600 °C).                                                                                               | .54 |

| Figure 5-6. Measured forward voltage <i>vs.</i> temperature at different forward current densities.                                                                                                                | .55 |

| Figure 5-7. Measured and modeled sensitivity <i>vs.</i> forward current density of the 4H-SiC pn diode temperature sensor. The extracted ideality factor and carrier lifetime are indicated on the graph.          | .55 |

## LIST OF TABLES

|            | High temperature electronic applications [10]. BS stands for bulk silicon technology, SOI stands for silicon on insulator technology,  |     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | WBG stands for wide bandgap semiconductor technology and NA stands for not presently available.                                        | .3  |

|            | Material properties of Si, GaAs and SiC [14]. $\perp$ indicates perpendicular to c-axis, and $\parallel$ indicates parallel to c-axis. | .6  |

|            | Parameters for bandgap narrowing model of 4H-SiC in Equation (2.6)-(2.9) [38].                                                         | .13 |

| Table 3-1. | Summary of the etching recipes of crystalline 4H-SiC.                                                                                  | .25 |

| Table 3-2. | Summary of interface state densities for SiO <sub>2</sub> /SiC interfaces                                                              | .29 |

#### LIST OF ABBREVIATIONS

Al Aluminum

Al<sub>2</sub>O<sub>3</sub> Aluminum oxide

Ar Argon

A<sub>v</sub> Intrinsic voltage gain

α Common-base current gain

$\alpha_T$  Base transport factor

B Boron

BJT Bipolar junction transistor

β Common-emitter current gain

C Carbon

CF<sub>4</sub> Tetrafluoromethane

CHF<sub>3</sub> Trifluoromethane

Cl<sub>2</sub> Chlorine

CMOS Complementary metal-oxide-semiconductor

CO Carbon monoxide

CVD Chemical vapor deposition

DC Direct current

D<sub>N</sub> Diffusion coefficient of electrons

D<sub>P</sub> Diffusion coefficient of holes

ECR Electron cyclotron resonance

E<sub>g</sub> Energy bandgap

E<sub>A</sub> Acceptor ionization energy

E<sub>D</sub> Donor ionization energy

E<sub>Fn</sub> Quasi-Fermi level for n-type semiconductor

E<sub>Fp</sub> Quasi-Fermi level for p-type semiconductor

$\epsilon_0$  Vacuum permittivity

$\varepsilon_{\rm s}$  Relative permittivity

GaAs Gallium arsenide

G<sub>m</sub> Transconductance

HBr Hydrogen Bromide

HF Hydrogen Fluoride

HMDS Hexamethyldisilazane

IC Integrated Circuit

ICP Inductively coupled plasma

I<sub>B</sub> Base current

$I_{C}$  Collector current  $I_{E}$  Emitter current

JFET Junction field effect transistor

k Boltzmann constant

$L_N$  Diffusion length of electrons  $L_P$  Diffusion length of holes

MESFET Metal-semiconductor field effect transistor

MOSFET Metal-oxide-semiconductor field effect transistor

N<sub>B</sub> Doping concentration in the base region

$N_{C}$  Doping concentration in the collector region  $N_{E}$  Doping concentration in the emitter region  $N_{A}$  Doping concentration of p-type semiconductor

N<sub>A</sub> Concentration of ionized acceptors

N<sub>D</sub> Doping concentration of n-type semiconductor

N<sub>D</sub><sup>+</sup> Concentration of ionized donors

N<sub>c</sub> Effective density of conduction band states

N<sub>v</sub> Effective density of valance band states

Ni Nickel

NO Nitric oxide N<sub>2</sub>O Nitrous oxide

n Electron concentration/Ideality factor of PN junctions

n<sub>i</sub> Intrinsic carrier concentration

O<sub>2</sub> Oxygen

PECVD Plasma enhanced chemical vapor deposition

p Hole concentration

ρ<sub>c</sub> Specific contact resistance

q Electric charge

RIE Reactive ion etching

RTD Resistance temperature detector

RTA Rapid thermal annealing

$R_c$  Contact resistance  $R_{sh}$  Sheet resistance  $r_o$  Output resistance

γ<sub>E</sub> Emitter injection efficiency factor

δ Recombination factor

SEM Scanning electron microscopy

Si Silicon

SiC Silicon carbide  $Si_3N_4$  Silicon nitride  $SiO_2$  Silicon dioxide

SOI Silicon-on-insulator

T Temperature

TCP Transformer coupled plasma

TLM Transfer length method

Ti Titanium

$\tau_e$  Effective carrier lifetime  $\tau_n$  Carrier lifetime of electrons

$\tau_p$  Carrier lifetime of holes

$\begin{array}{ll} \mu_n & & \text{Electron mobility} \\ \mu_p & & \text{Hole mobility} \end{array}$

V Voltage

V<sub>A</sub> Early voltage

V<sub>BC</sub> Base-collector voltage

$V_{BE}$  Base-emitter voltage

$V_{CE}$  Collector-emitter voltage

V<sub>bi</sub> Built-in potential

W<sub>B</sub> Base width

$W_{dep} \hspace{1cm} Depletion \ width$

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my sincere gratitude to my advisor, Professor Albert P. Pisano, for his guidance and support. His contagious enthusiasm, intense dedication, and limitless patience, have set an example that I will strive to follow. I would like to thank him for all the valuable discussion, which consolidates my knowledge and also inspires me to pursue novel research directions. I am truly grateful to have had the opportunity to work and learn under his mentorship.

I would like to thank Prof. Tsu-Jae King Liu and Prof. Liwei Lin for reviewing my dissertation and giving me invaluable feedback. I would also like to thank Prof. Tsu-Jae King Liu, Prof. Liwei Lin and Prof. Ali Javey for serving on the committee of my qualifying exam. They have given me much critical and constructive feedback that helped shape this thesis.

During my tenure as a graduate student at Berkeley, I had the opportunity to work with some of the most talented people. I would like to thank all my group members and colleagues for their support. In particular I would like to thank Dr. Debbie G. Senesky, Dr. Yi Rao, Dr. Jim C. Cheng, Dr. Chih-Ming Lin, Dr. Nuo Xu, Dr. Clinton G. Warren, and Dr. Ting-Ta Yen for the valuable discussion, and their generous help and training on the fabrication and characterization tools.

I am also thankful to the Marvell Nanofabrication Laboratory staff for their help and assistance. Special thanks go to Dr. Xiaofan Meng, who helped with the deposition of different metal layers. I would also like to thank Joe Donnelly, Ryan Rivers and Jay Morford for their help and assistance on the fabrication process. At the same time, I want to thank Zeying Ren for giving me helpful suggestions and tool assistance.

Last but not least, I would like to show my deepest gratitude to my parents, for their unconditional love and support. Many thanks to my beloved husband Wenchao for being supportive all the time, and cheering me up when I am down. I am truly grateful that we worked alongside each other during this Ph.D. journey.

# Chapter 1

## Introduction

There is a rising demand for harsh-environment integrated circuits and sensors for a wide variety of applications, ranging from structure health monitoring and process control to space navigation. The ability to continually obtain information in situ in high temperature environment such as a jet engine or a deep oil well can potentially save millions of dollars and even human lives. It also opens doors to space missions to locations with extreme conditions such as Venus, where devices would be required to operate around 500 °C. Wide bandgap materials are well suited for these applications due to their superior electrical and mechanical properties compared to the silicon incumbents. 4H-SiC, a polytype of silicon carbide (SiC), for instance, has a bandgap (3.2 eV) that is almost 3 times of that of silicon (1.12 eV) [1]. The wider bandgap results in a much lower intrinsic carrier concentration compared to that of silicon [1], which makes it an ideal candidate for high temperature (> 300°C) applications. These high temperature capabilities will be the main subject of investigation in this thesis. The overarching objective of the thesis is to develop 4H-SiC technologies for both transistor and sensor devices. Specifically, we investigate and develop the design, simulation, fabrication and characterization of 4H-SiC bipolar junction transistor (BJT) that is capable of operating at elevated temperatures up to 400°C. In addition, a high-performance temperature sensor based on 4H-SiC pn diode which can stably operate in a temperature range from 20°C to 600°C is demonstrated. This type of temperature sensor can be integrated with supporting circuitries to create a sensing module that is capable of working at extremely high temperatures.

## 1.1 High Temperature Sensing Applications

Harsh environment conditions are typically characterized by prolonged operation at high temperatures, exposure to intense radiation and exposure to corrosion and erosion. These conditions are common to combustion engines, chemical plants, oil wells, and space missions. Electronic and sensor components that can withstand such harsh environments can be highly beneficial to these applications. The ability to place sensing units at crucial

hot spots can be the key enabler for a multitude of innovations that are not possible with traditional silicon-based devices. For instance, in-cylinder monitoring of a combustion engine not only provides a means to gather accurate information about the status of the engine but also enables closed-loop control that can improve combustion efficiency. In this section, we first highlight some of these applications and describe in particular their high temperature requirements. We then review current available device technologies and discuss their limitations under these requirements.

#### **Combustion Monitoring**

The continual demand for increasing fuel efficiency and reducing environmental footprints require advances in combustion controls for automotive engines and gas turbines [2]. Optimizing an engine for these objectives require precise control of temperature, pressure, air-to-fuel ratio, and timing [3]. Traditional sensing mechanisms are based on indirect measurements, which limits the scope of control methods. Incylinder sensing, on the other hand, holds the promise that it can provide accurate and timely information about combustion events, which in turn can be utilized to develop advanced closed-loop control systems for the engines to achieve the aforementioned objectives [4]. The temperature requirements in these environments can be quite stringent. A typical engine (gasoline or diesel) has an in-cylinder temperature ranging from 200 °C to 450 °C [5]. The temperature inside a gas turbine can reach as high as 650 °C [5]. Therefore, it is crucial to develop integrated sensing modules (sensors and electronic components) that can operate reliably over an extended period of time at high temperatures, in order to unleash the full potential of these advanced control systems.

#### Process Control

In production environments such as an oil refinery or a chemical plant, it is important to have proper process control to maintain quality, reduce operational cost and minimize waste. Current methods for performing process control rely on periodic data interrogation that lags behind the actual process, due to inability to directly gather information in harsh environments such as a deep oil well or a reactor plant. This leads to waste of resources and inferior products. Similar to combustion monitoring, a sensing module directly placed in these environments can enable real-time monitoring of process parameters, thus allows improved process control and detects hazardous scenarios in a timely manner [6]. The peak temperature requirements can range from 300°C in an oil or gas drill to 600°C in a geothermal extraction site [10].

#### Space Navigation

An important sensing module that is common to these navigation systems is the inertial measurement unit (IMU) [7]. A typical IMU contains a gyroscope, an accelerometer and the necessary electronic circuits, which together are used to harvest information on a

craft's velocity and orientation. However, traditional silicon devices are incapable of handling the stringent conditions often encountered by these navigation systems without extensive cooling, packaging and radiation shielding. These additional items would add volume and weight, thus placing a severe burden on the overall cost of the mission. NASA's Venus exploration mission, for instance, would require devices to operate around 500°C.

#### Structural Health Monitoring

Continual monitoring in environments such as a nuclear energy production plant or a steam generator tube and pressure vessel is crucial for ensuring operation inside the safety margins. It also reduces downtime for inspection and repair that may incur expensive labor cost and disrupt the services of these plants. Hence, measuring structural changes, also known as structural health monitoring, in the critical areas, can bring significant benefits to these applications [8]. An ideal sensing module for these applications would consist of sensors such as piezoelectric or piezoresistive sensors as well as integrated electronic components with wireless capabilities. The operating conditions of these applications such as inside a nuclear energy or a high-power processing plant, however, would also require the sensing module to work at high temperatures (> 300°C) over a long period of time. This thesis explores the development of high temperature transistors and sensors based on silicon carbide that can serve as the

Table 1-1. High temperature electronic applications [10]. BS stands for bulk silicon technology, SOI stands for silicon on insulator technology, WBG stands for wide bandgap semiconductor technology and NA stands for not presently available.

| High Temperature Electronic  | Peak         | Current    | Future     |

|------------------------------|--------------|------------|------------|

| Applications                 | Ambient (°C) | Technology | Technology |

| Automotive                   |              |            |            |

| Engine Control Electronics   | 150          | BS & SOI   | BS & SOI   |

| On-cylinder & Exhaust Pipe   | 600          | NA         | WBG        |

| Electric Suspension & Breaks | 250          | BS         | WBG        |

| Electric/Hybrid Vehicle PMAD | 150          | BS         | WBG        |

| Turbine Engine               |              |            |            |

| Sensors, Telemetry, Control  | 300          | BS & SOI   | SOI & WBG  |

| •                            | 600          | NA         | WBG        |

| Electric Actuation           | 150          | BS & SOI   | WBG        |

|                              | 600          | BS         | WBG        |

| Spacecraft                   |              |            |            |

| Power Management             | 150          | BS & SOI   | WBG        |

| _                            | 300          | NA         | WBG        |

| Venus & Mercury Exploration  | 550          | NA         | WBG        |

| Industrial                   |              |            |            |

| High Temperature Processing  | 300          | SOI        | SOI        |

|                              | 600          | NA         | WBG        |

| Deep-Well Drilling Telemetry |              |            |            |

| Oil and Gas                  | 300          | SOI        | SOI & WBG  |

| Geothermal                   | 600          | NA         | WBG        |

building blocks of these integrated sensing modules.

Table 1-1 categorizes these applications and lists the peak temperature requirement for each of them. Silicon (Si) based devices cannot survive at high temperatures (> 300 °C) mainly due to the high intrinsic carrier concentration which exceeds the intentional doping, and high leakage currents. Silicon-on-insulator (SOI) technology enables silicon devices to approach their theoretical limits by cutting off leakage paths. At temperatures higher than 300 °C, wide bandgap semiconductors provide solutions capable of exceeding the limits of Si. They are listed as future technologies in Table 1-1.

#### 1.2 Material Properties of Silicon Carbide

SiC-based semiconductor electronic devices and circuits are being developed for working under extreme conditions, such as high temperature, high power, and high radiation, thanks to its superior material properties compared to Si and other semiconductors. This section briefly surveys the basic properties and advantages of SiC material.

#### 1.2.1 Crystal Structure

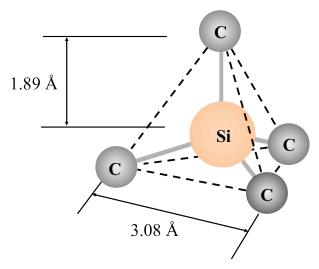

SiC is a group IV-IV compound semiconductor. Each silicon (Si) atom is tetrahedrally bonded with four carbon (C) atoms, and vice versa. The approximate distance between Si-C atoms is 1.89 Å, and the distance between Si-Si or C-C atoms is 3.08 Å. The tetrahedrally bonded Si-C cluster is shown in Figure 1-1 [1], [13].

SiC exists in many different crystal structures with the same chemical composition, called polytypes [1], [13]-[15]. There are over 100 known polytypes of SiC, and the most common polytypes of SiC that have been developed for electronic applications are 3C-

Figure 1-1. Tetrahedrally bonded Si-C cluster [1], [13].

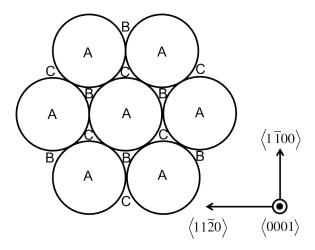

Figure 1-2. Hexagonal close packing positions of Si-C bilayers [1], [15].

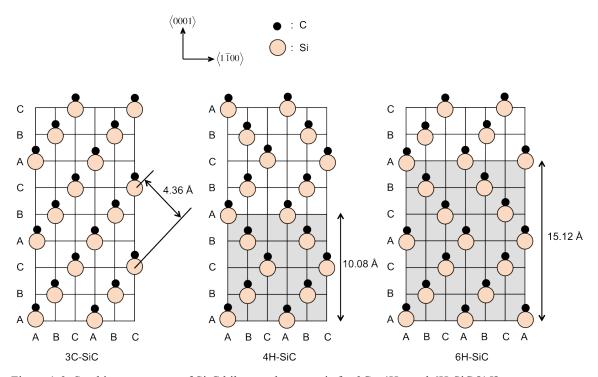

#### SiC, 4H-SiC, and 6H-SiC.

Considering the Si-C pair as a sphere, they form hexagonal patterns when packed closely in a plane as a Si-C bilayer. The positions of the spheres in the first plane are denoted as A-site positions. For the next layer packed on top of the first layer, it can take either B-site positions or C-site positions. The hexagonal packing positions of Si-C bilayers are shown in Figure 1-2. Different polytypes are composed of different stacking sequences of Si-C bilayers. For instance, 4H-SiC has a stacking sequence of ABCB and it

Figure 1-3. Stacking sequences of Si-C bilayers along c-axis for 3C-, 4H-, and 6H-SiC [15].

| Table 1-2. Material properties of Si | GaAs and SiC [14]. ⊥ indicates | perpendicular to c-axis, and |

|--------------------------------------|--------------------------------|------------------------------|

| indicates parallel to c-axis.        |                                |                              |

| Property                                                                     | Si   | GaAs | 3C-SiC | 6H-SiC        | 4H-SiC         |

|------------------------------------------------------------------------------|------|------|--------|---------------|----------------|

| Energy Bandgap [eV]                                                          | 1.12 | 1.42 | 2.3    | 3.0           | 3.2            |

| Critical Field at $N_D = 10^{17} \text{ cm}^{-3} \text{ [MV/cm]}$            | 0.6  | 0.6  | 1.8    | ∥ 3.2<br>⊥ >1 | ∥ 3.0<br>⊥ 2.5 |

| Thermal Conductivity [W/cmK]                                                 | 1.5  | 0.5  | 3-5    | 3-5           | 3-5            |

| Saturated Electron Drift<br>Velocity [10 <sup>7</sup> cm/s]                  | 1.0  | 1.2  | 2.5    | 2.0           | 2.0            |

| Electron Mobility at $N_D = 10^{16} \text{ cm}^{-3} [\text{cm}^2/\text{Vs}]$ | 1200 | 6500 | 750    | ∥ 60<br>⊥ 400 | ∥ 800<br>⊥ 800 |

| Hole Mobility at $N_A = 10^{16} \text{ cm}^{-3} [\text{cm}^2/\text{Vs}]$     | 420  | 320  | 40     | 90            | 115            |

| Relative Dielectric Constant                                                 | 11.9 | 13.1 | 9.7    | 9.7           | 9.7            |

repeats every four layers throughout the crystal. Similarly, 6H-SiC has a stacking sequence of ABCACB. Both 4H-SiC and 6H-SiC have hexagonal crystal structures. 3C-SiC, sometimes referred to as  $\beta$ -SiC, has a stacking sequence of ABC and it is the only form of SiC with a cubic crystal structure. The schematic structures of common polytypes of SiC are shown in Figure 1-3.

#### 1.2.2 Material Properties

SiC is a promising semiconductor for harsh environment sensing applications due to its excellent electrical and physical properties [1]-[15]. The wide bandgap energy and low intrinsic carrier concentration allow SiC based semiconductor devices to be functional at much higher temperatures. Moreover, high breakdown field, high-saturated electron velocity, and high thermal conductivity enable SiC devices to work under extreme conditions. The basic material properties of three SiC polytypes are summarized in Table 1-2 [14]. The critical field and mobility of SiC are anisotropic, and they strongly depend on crystallographic directions of applied electric field and current flow. For comparison, the properties of Si and gallium arsenide (GaAs) are also included in Table 1-2. 4H-SiC is used in this work since it has the widest energy bandgap.

## 1.3 High Temperature SiC Electronics

Si semiconductor devices are usually confined to operate at temperatures < 300 °C. The intrinsic carrier concentration increases exponentially with temperature, and these free carriers could exceed the intentional doping concentration and govern the device operation in Si devices. Furthermore, the undesired junction reverse-bias leakage currents are closely related to the intrinsic carrier concentration. As the temperature increases, the

undesired leakage current will grow unacceptably large. SiC semiconductor devices can function at much higher temperatures than Si mainly due to the wide bandgap energy and low intrinsic carrier concentration of SiC. High temperature operation of SiC-based devices and ICs has been reported for several technologies.

The gate-insulator reliability is a critical issue for high temperature operation of SiC metal-oxide-semiconductor field effect transistors (MOSFETs), which limits the highest operating temperatures under 350 °C for SiC MOSFETs. The first high temperature depletion-mode n-channel MOSFET was fabricated and characterized by Palmour *et al.* from North Carolina State University in 1987. Later, Brown *et al.* [16][17] from General Electric (GE) reported the development of the first SiC analog IC, a monolithic MOSFET operational amplifier, based on a 6H-SiC depletion-mode n-channel MOSFET technology. In that research, stable device operation was demonstrated up to 300 °C. However, circuit drift instabilities occurred at 350 °C. Complimentary metal-oxide-semiconductor (CMOS) technologies for SiC based devices have also been investigated. Recently, Clark *et al.* from Raytheon UK demonstrated SiC CMOS technologies that operate at elevated temperatures up to 350 °C with low gate leakage [18].

6H-SiC junction field effect transistors (JFETs) have been also investigated notably by NASA Glenn Research and Case Western Reserve University [19]-[21]. Prolonged stable operation of 6H-SiC JFETs for thousands of hours at 500 °C has been demonstrated. The devices have also been tested at low temperatures down to -125 °C. SiC JFET differential amplifier circuits capable of operating at up to 600 °C were demonstrated by Case Western Reserve University [22]. Subsequently, basic logic gates based on 6H-SiC JFETs were reported to work at temperatures up to 550 °C [23].

6H-SiC metal-semiconductor field effect transistors (MESFETs) have also been demonstrated for high temperature operation up to 500 °C [24]. However, they suffer from significant leakage currents at the Schottky gate electrodes at higher temperatures, which limits the duration of high temperature operation.

The research on 4H-SiC bipolar junction transistors (BJTs) originally focused on high power applications. The first high voltage NPN BJT in 4H-SiC was demonstrated by Ryu et al. from Cree, Inc. in 2001 [25]. Subsequently, many efforts have been made to develop SiC power BJTs from Purdue University, Rutgers University, and Royal Institute of Technology [26]-[30]. Recently, there are growing interests on developing high temperature integrated circuits using 4H-SiC BJTs. SiC BJTs are not as strongly affected by oxide quality as SiC MOSFETs. In addition, SiC BJTs are normally-off devices and have higher transconductance compared with SiC JFETs. 4H-SiC is used due to the fact that it has the widest energy bandgap compared with other SiC polytypes, which is preferred for high temperature applications. BJTs on semi-insulating 4H-SiC was demonstrated to operate up to 355 °C by Singh et al. in 2011 [31], [32]. In this dissertation, 4H-SiC NPN BJTs for low voltage applications are presented. The devices are capable of stable operation up to 400 °C [33].

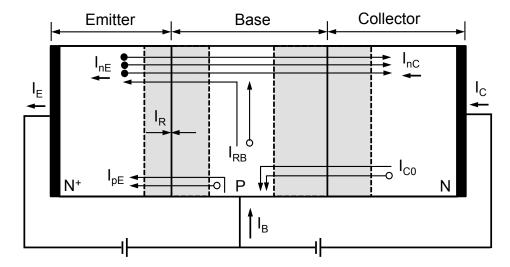

Figure 1-4. Schematic of a NPN BJT biased at forward active region [34].

#### 1.4 Fundamentals of Bipolar Junction Transistors

A bipolar junction transistor is a three-terminal semiconductor device [34]. The middle region is referred to as the *base* and it is very narrow compared with the minority carrier diffusion length in this region. The other two regions are known as the *emitter* and the *collector*. Due to the fact that electron mobility is usually higher than hole mobility, NPN BJTs are more widely used than PNP BJTs. The schematic of a NPN BJT biased in the forward active mode with carrier flux components is shown in Figure 1-4 [34]. The two junctions are referred to as the emitter-base (E-B) junction and the collector-base (C-B) junction respectively.

As pictured in Figure 1-4, the E-B junction is forward biased and the C-B junction is reverse biased in the forward active mode. The E-B junction is an  $n^+$ -p one-sided junction. Therefore, more electrons are injected from the emitter to the base than holes injected from the base to the emitter. Since the quasineutral base width is much smaller than the minority carrier diffusion length, the vast majority of injected electrons that diffuses through the base can reach the depletion region of the reverse biased C-B junction. The electrons are then swept to the collector by the accelerating electrical field. The electrons injected from the emitter to the base constitute the current  $I_{nE}$ , and the holes injected from the base to the emitter give rise to the current  $I_{pE}$ . For the one-sided  $n^+$ -p junction,  $I_{pE} << I_{nE}$ . Some electrons are lost through recombination with holes in the base ( $I_{RB}$ ). The current  $I_{nC}$  is associated with the injected electrons successfully cross the base and reach the collector.  $I_{C0}$  is the current of the minority carrier holes in the collector that are swept into the base in the reversed biased C-B junction. Since  $I_{C0}$  is a reverse biased current,  $I_{C0}$  <<  $I_{nC}$ . The recombination-generation current associated with the depletion region of the

E-B junction is identified as  $I_R$ . The total currents of the emitter, base and collector regions are given by

$$I_E = I_{nE} + I_{nE} + I_R, (1.1)$$

$$I_B = I_{vE} + I_{RB} + I_R - I_{C0}, (1.2)$$

$$I_C = I_{pF} - I_{RR} + I_{C0}. (1.3)$$

The three currents can be related by

$$I_E = I_B + I_C. ag{1.4}$$

In the common-base mode, the emitter current  $(I_E)$  is the input variable while the collector current  $(I_C)$  is the output variable.  $\alpha$  is the common base current gain, which is defined as the ration of  $I_C/I_E$ . It can be calculated as

$$\alpha = \gamma_E \alpha_T \delta = \left(\frac{I_{nE}}{I_{nE} + I_{pE}}\right) \left(\frac{I_{nC}}{I_{nE}}\right) \left(\frac{I_{nE} + I_{pE}}{I_{nE} + I_{R} + I_{pE}}\right). \tag{1.5}$$

In Equation (1.5),  $\gamma_E$  is the emitter injection efficiency factor,  $\alpha_T$  is the base transport factor, and  $\delta$  is the recombination factor [35]. The emitter injection efficiency factor is a measure of the ability of the emitter to inject electrons into the base. The base transport factor illustrates the capability of the injected electrons to diffuse through the base without recombination. The recombination factor takes into account the recombination-generation current in the forward biased B-E junction.

In the common-emitter mode, the base current  $(I_B)$  is the input variable and the collector current  $(I_C)$  is the output variable. The common-emitter current gain  $\beta$  is defined as the ratio of  $I_C/I_B$ , which can be calculated as

$$\beta = \frac{\alpha}{1 - \alpha}.\tag{1.6}$$

The common-emitter mode is the most widely used circuit configuration. Therefore, current gain is often referred to as the common-emitter current gain  $\beta$ .

#### 1.5 Thesis Organization

This work focuses on the development and characterization of 4H-SiC NPN BJTs for high temperature sensing applications. This dissertation consists of six chapters including

this introduction. In Chapter 2, physical models of the device behaviors are studied. Chapter 3 presents the development of microfabrication technologies for SiC-based electrical devices. Chapter 4 discussed the simulation and characterization results of the fabricated 4H-SiC BJTs. In Chapter 5, the development and characterization of a high-performance temperature sensor based on 4H-SiC pn diode are presented. Finally, the contributions of this work are summarized and suggestions for future research directions are outlined in Chapter 6.

# Chapter 2

# **Physical Models**

Numerical device simulators are powerful tools to investigate electrical behaviors of semiconductor devices. They can provide information of internal physical parameters that are difficult or impossible to measure. Therefore, numerical device simulators are widely used to predict and explain device performance. A real semiconductor device is represented in the simulator as a non-uniform two-dimensional (2D) or three-dimensional (3D) grid of nodes. Physical properties of the real device are discretized onto the grid. By iteratively solving a set of coupled nonlinear partial differential equations, the transport of carriers through the structure under external fields can be described. The governing equations are Poisson equation, carrier continuity equations and drift-diffusion equations. In order to obtain accurate simulation results, it is essential to utilize appropriate physical models with proper material properties. In this chapter, important physical models applied in the device simulation are introduced and discussed. Temperature dependences of the models are investigated.

#### 2.1 Band Structure

Energy band structure is the most fundamental property of a semiconductor. Realistic band structures are complicated. For device simulation, the band structure is described by energy bandgap, effective masses and effective density of states.

#### 2.1.1 Energy Bandgap and Temperature Dependence

Energy bandgap is the difference between the lowest energy in the conduction band and the highest energy in the valance band. As we have discussed in Chapter 1, SiC has a wider bandgap compared with Si. The bandgap of 4H-SiC is 3.23 eV at 300 K. It is not a constant value when temperature varies, and the temperature dependence of the 4H-SiC bandgap can be modeled by Equation (2.1) from [36]:

$$E_g(T) = E_g(0) - 6.5 \times 10^{-4} \times \frac{T^2}{T + 1300} \text{ eV},$$

(2.1)

where  $E_g(0)$  is the bandgap at 0 K, and T is the temperature in Kelvin.

#### 2.1.2 Bandgap Narrowing

It has been reported that the bandgap of a semiconductor material shrinks when the impurity concentration is particularly high. This effect is called the *bandgap narrowing effect*. In a device containing adjacent regions with different doping concentrations, the displacements of band edges induced by the doping concentrations may heavily influence the device behavior. This is because the shifts of the band edges change the potential barriers in the device, which alters the carrier transport behavior across the junctions. In BJTs, the emitters are heavily doped, and therefore the bandgap narrowing effect in the emitters have to be considered in the device simulation.

Considering the bandgap narrowing effect, the effective bandgap  $E_{g,eff}$  can be written as

$$E_{g,eff} = E_{g0} - \Delta E_{bng}, \tag{2.2}$$

where  $E_{g0}$  is the bandgap at a low doping concentration, and  $\Delta E_{bng}$  is the shift of the bandgap due to the bandgap narrowing effect.

The intrinsic carrier concentration  $n_i$  for a lightly doped semiconductor is given by Equation (2.3)

$$n_i^2 = N_c N_v \exp\left(\frac{-E_{g0}}{kT}\right),\tag{2.3}$$

where  $N_c$  and  $N_v$  are the effective density of conduction and valence band states, k is Boltzmann constant, and T is the temperature in Kelvin [37]. For BJTs, the emitter is heavily doped. The effect of bandgap narrowing on the intrinsic carrier concentration in the emitter region is given by

$$n_{i,eff}^2 = n_i^2 \exp\left(\frac{\Delta E_{bng}}{kT}\right),\tag{2.4}$$

which changes exponentially with  $\Delta E_{bng}$ . For a NPN BJT, the minority carrier concentration  $p_{E0}$  in the emitter region can be written as

$$p_{E0} = \frac{n_{i,eff}^2}{N_E} = \frac{n_i^2}{N_E} \exp\left(\frac{\Delta E_{bng}}{kT}\right),\tag{2.5}$$

|        | $\mathbf{A}_{\mathbf{nc}}$ | $\mathbf{B}_{\mathbf{nc}}$ | $\mathbf{A}_{\mathbf{n}\mathbf{v}}$ | $\mathbf{B}_{\mathbf{nv}}$ |

|--------|----------------------------|----------------------------|-------------------------------------|----------------------------|

| n-type | -1.50×10 <sup>-2</sup>     | -2.93×10 <sup>-3</sup>     | 1.90×10 <sup>-2</sup>               | 8.74×10 <sup>-3</sup>      |

|        | $A_{ m pc}$                | B <sub>pc</sub>            | $\mathbf{A}_{\mathbf{pv}}$          | $\mathbf{B}_{\mathrm{pv}}$ |

| p-type | -1.57×10 <sup>-2</sup>     | -6.64×10 <sup>-4</sup>     | 1.30×10 <sup>-2</sup>               | 1.14×10 <sup>-3</sup>      |

Table 2-1. Parameters for bandgap narrowing model of 4H-SiC in Equation (2.6)-(2.9) [38].

where  $N_E$  is the doping concentration in the emitter region. Equation (2.5) shows that the bandgap narrowing effect increases the minority carrier concentration in the emitter region, which leads to a reduction of the emitter injection efficiency.

The doping-induced bandgap displacements and the bandgap narrowing effect in 4H-SiC have been modeled by Lindefelt [38]. The model is based on the theory of Jain and Roulston and is made applicable to 4H-SiC by considering the three electron effective mass components associated with hexagonal lattices. The band edge displacements for n-type and p-type semiconductors can be expressed as

$$\Delta E_{nc} = A_{nc} \left( \frac{N_D^+}{10^{18}} \right)^{1/3} + B_{nc} \left( \frac{N_D^+}{10^{18}} \right)^{1/2}, \tag{2.6}$$

$$\Delta E_{nv} = A_{nv} \left( \frac{N_D^+}{10^{18}} \right)^{1/4} + B_{nv} \left( \frac{N_D^+}{10^{18}} \right)^{1/2}, \tag{2.7}$$

$$\Delta E_{pc} = A_{pc} \left( \frac{N_A^-}{10^{18}} \right)^{1/4} + B_{pc} \left( \frac{N_A^-}{10^{18}} \right)^{1/2}, \tag{2.8}$$

$$\Delta E_{pv} = A_{pv} \left( \frac{N_A^-}{10^{18}} \right)^{1/3} + B_{pv} \left( \frac{N_A^-}{10^{18}} \right)^{1/2}. \tag{2.9}$$

The coefficients  $A_{nc}$ ,  $B_{nc}$ ,  $A_{nv}$ ,  $B_{nv}$ ,  $A_{pc}$ ,  $B_{pc}$ ,  $A_{pv}$ , and  $B_{pv}$  are listed in Table 2-1, with the band edge displacements given in eV.

#### 2.1.3 Effective Masses and Effective Density of States

For 4H-SiC, the effective density of states in the conduction band  $N_c$  can be calculated from

$$N_c = 4.82 \times 10^{15} \times M \times \left(\frac{m_c}{m_0}\right)^{3/2} \times T^{3/2} = 3.25 \times 10^{15} \times T^{3/2} \text{ cm}^{-3},$$

(2.10)

where M = 3 is the number of equivalent valleys in the conduction band, and  $m_c = 0.37m_0$  is the effective mass of the density of states in one valley of conduction band [36]. The effective density of states in the valance band is given by

$$N_v = 4.85 \times 10^{15} \times T^{3/2} \text{ cm}^{-3}.$$

(2.11)

#### 2.2 Mobility

The carrier mobilities are basic inputs for expressing currents in semiconductor devices. They are dependent on doping concentration and temperature. Using the empirical relation suggested by Caughey and Thomas [39], the electron mobility  $\mu_n$  and hole mobility  $\mu_p$  at low electric field can be modeled as

$$\mu_{n,p} = \mu_{n,p}^{\min} + \frac{\mu_{n,p}^{delta}}{1 + \left(\frac{N_A + N_D}{N_{n,p}^{\mu}}\right)^{\gamma_{n,p}}} \left(\frac{T}{300}\right)^{\alpha_{n,p}}, \tag{2.12}$$

where  $N_A$  and  $N_D$  are local impurity concentrations, and the parameters are listed as below:

$$\begin{split} \mu_n^{\text{min}} &= 0 \text{ cm}^2 / V \cdot S, & \mu_p^{\text{min}} &= 15.9 \text{ cm}^2 / V \cdot S, \\ \mu_n^{\text{delta}} &= 947 \text{ cm}^2 / V \cdot S, & \mu_p^{\text{delta}} &= 108.1 \text{ cm}^2 / V \cdot S, \\ N_n^{\mu} &= 1.94 \times 10^{17} \text{ cm}^{-3}, & N_p^{\mu} &= 1.76 \times 10^{19} \text{ cm}^{-3}, \\ \gamma_n &= 0.61, & \gamma_p &= 0.34, \\ \alpha_n &= -2.15, & \alpha_p &= -2.15. \end{split}$$

The parameters for the doping and temperature dependences of 4H-SiC mobilities are from the work of Schaffer *et al.* [40].

#### 2.3 Incomplete Ionization

In Si, most impurity levels are shallow enough so that the dopants can be considered fully ionized at room temperature. However, this is not the case in SiC because the donor level  $(E_D)$  for nitrogen (N) and acceptor level  $(E_A)$  for aluminum (Al) in SiC are relatively deep compared to the thermal energy kT. Therefore, the incomplete ionization of the impurities in SiC has to be considered even at high temperatures.

The concentration of the ionized impurity atoms is given by

$$N_D^+ = \frac{N_D}{1 + g_D \exp\left(\frac{E_{Fn} - E_D}{kT}\right)},$$

(2.14)

$$N_{A}^{-} = \frac{N_{A}}{1 + g_{A} \exp\left(\frac{E_{A} - E_{Fp}}{kT}\right)},$$

(2.15)

where  $N_D^+$  and  $N_A^-$  are the ionized donor and acceptor concentrations,  $N_D$  and  $N_A$  are the (active) donor and acceptor concentrations,  $g_D = 2$  and  $g_A = 4$  are the degeneracy factors for the donor and acceptor levels,  $E_D$  and  $E_A$  are the donor and acceptor ionization energies, and  $E_{Fn}$  and  $E_{Fp}$  are the quasi-Fermi levels [41].

Impurity atoms in SiC can substitute on either the silicon or carbon sublattice. Nitrogen atoms substitute on the carbon sites, while aluminum atoms occupy the silicon sites [42]. Due to the long unit cells, inequivalent lattice sites exist in many SiC polytypes, such as 4H-, 6H- and 15R-SiC. These inequivalent lattice sites are divided into two kinds: one is hexagonal-like atomic configuration (h) and the other one is cubic-like atomic configuration (k).

For nitrogen doped n-type 4H-SiC, two inequivalent lattice sites of nitrogen (h, k) have been identified by Hall-effect and IR absorption measurements with ground state  $1s(A_I)$  binding energies of  $E_D(h) = 52.1 \text{ meV}$  and  $E_D(k) = 91.8 \text{ meV}$  [43]. The number of k-type donor sites is the same as k-type donor sites. It is worth noting that a simplification of a single donor level,  $E_D = 65 \text{ meV}$  below the conduction band edge, is assumed in Equation (2.14), which can be obtained by [44]

$$N_{D_{-}^{-}4H-SiC}^{+} = \frac{0.5N_{D}}{1 + g_{D} \exp\left(\frac{E_{Fn} - E_{D}(h)}{kT}\right)} + \frac{0.5N_{D}}{1 + g_{D} \exp\left(\frac{E_{Fn} - E_{D}(k)}{kT}\right)}$$

$$= \frac{N_{D}}{1 + g_{D} \exp\left(\frac{E_{Fn} - E_{D}}{kT}\right)}.$$

(2.16)

For aluminum-doped p-type 4H-SiC, two inequivalent lattice sites should generate two energy levels in theory. However, the difference between the two acceptor levels are too small to be readily detected. Therefore, only one acceptor energy level  $E_A = 191 \text{ meV}$  is assumed in the calculation [45].

#### 2.4 Generation-Recombination

Generation-recombination processes are processes that create and eliminate mobile carriers (electrons and holes). They are very important to the operation of many semiconductor devices, especially for bipolar devices. There are several mechanisms that are crucial in SiC BJTs.

#### 2.4.1 Shockley-Read-Hall Recombination

In the indirect-bandgap semiconductors, such as Si and SiC, indirect recombination process through localized states or recombination centers is dominant. This recombination process was originally modeled by Shockley and Read [47] and later by Hall [48], and the process is commonly called Shockley-Read-Hall (SRH) recombination. The rate of SRH recombination is given by

$$R_{SRH} = \frac{np - n_{i,eff}^2}{\tau_p(n + n_1) + \tau_n(p + p_1)},$$

(2.17)

with  $n_1$  and  $p_1$  defined by

$$n_1 = n_{i,eff} \exp\left(\frac{E_{trap}}{kT}\right),\tag{2.18}$$

$$p_1 = n_{i,eff} \exp\left(\frac{-E_{trap}}{kT}\right),\tag{2.19}$$

where n and p are the electron and hole concentrations,  $n_{i,eff}$  is the effective intrinsic carrier concentration,  $\tau_n$  and  $\tau_p$  are the lifetimes of electrons and holes, and  $E_{trap}$  is the energy difference between the defect level and the intrinsic level.

The lifetimes  $\tau_n$  and  $\tau_p$  depend on doping level and temperature. The doping dependence of the carrier lifetimes is described by the Scharfetter relation, and the temperature dependence is modeled by the power law.

$$\tau_{n,p} = \frac{\tau_{n,p}^{\text{max}}}{1 + \left(\frac{N_A + N_D}{N_{n,p}^{\text{ref}}}\right)^{\gamma_{n,p}}} \left(\frac{T}{300}\right)^{\alpha_{n,p}},$$

(2.20)

where  $\tau^{max}_{n,p}$  is the carrier lifetime in the material without impurities at 300 K, and the other parameters are listed as follows,

$$N_n^{ref} = 3 \times 10^{17} \text{ cm}^{-3},$$

$N_p^{ref} = 3 \times 10^{17} \text{ cm}^{-3},$   $\gamma_n = 0.3,$   $\gamma_p = 0.3,$   $\alpha_n = 1.72,$   $\alpha_n = 1.72.$

The parameters for the doping dependences of 4H-SiC career lifetimes are reported in [41] and [49], and the parameters for temperature dependence are taken from [41] and [50]. Since very limited studies on the doping dependence of carrier lifetimes in 4H-SiC have been reported, it is assumed that the parameters  $N_{ref}$  and  $\gamma_{n,p}$  from Si can be applied to 4H-SiC.

#### 2.4.2 Surface SRH Recombination

At surfaces or interfaces, an additional equation is used to describe the surface SRH recombination rate, which is structurally equivalent to expression of the bulk SRH recombination rate:

$$R_{SRH}^{surface} = \frac{np - n_{i,eff}^{2}}{(n + n_{1})/s_{p} + (p + p_{1})/s_{n}},$$

(2.21)

where  $s_n$  and  $s_p$  are the surface recombination velocities for electrons and holes,  $n_1$  and  $p_1$  are defined in Equation (2.18) and Equation (2.19).

Surface recombination rate has strong impact on the current gain of SiC BJTs. It depends on the quality of the interface between silicon dioxide (SiO<sub>2</sub>) and SiC. Some methods have been reported to reduce the interface state density at the SiO<sub>2</sub>/SiC interface, which will be discussed in detail in Chapter 3.

#### 2.4.3 Auger Recombination

In the Auger recombination process, the transition of an electron from the conduction band to the valance band is by transferring the energy to another free electron or hole by collision. Therefore, Auger recombination is a process in which three particles are involved: the recombining electron and hole, and the carrier by which the energy is absorbed. The highly energetic carrier, which gained the energy during the collision, then loses the energy in small steps through heat-producing collisions with the semiconductor

lattice. Auger recombination is typically important when the carrier densities are very high. Therefore, it is only likely to occur in highly doped semiconductor material or under high injection condition. The rate of Auger recombination can be modeled by [46]

$$R_{Auger} = \left(C_n n + C_p p\right) \left(np - n_{i,eff}^2\right),\tag{2.22}$$

where

$$C_n = 5 \times 10^{-31} \text{ cm}^{-6} \text{s}^{-1}$$

and  $C_p = 2 \times 10^{-31} \text{ cm}^{-6} \text{s}^{-1}$  [36].

# Chapter 3

# **Microfabrication Technology of SiC Bipolar Junction Transistors**

SiC single crystal material growth was first developed by Acheson process as byproducts for manufacturing industrial abrasives [51]. In 1955, Lely presented a sublimation method for SiC single crystal growth with higher quality [52]. However, Acheson process and Lely process can only produce small (~ 1 cm<sup>2</sup>) and irregular shaped SiC crystal pieces. In the late 1970s, Tairov and Tzvetkov developed a modified seeded sublimation process for growth of single crystal 6H-SiC [53], [54]. This method is also known as modified Lely method. It was a big breakthrough in the SiC industry because it made mass-production of single crystalline SiC wafers possible. After years of development of the SiC crystal growth technology, Cree, Inc. became the first company to sell 2.5 cm diameter 6H-SiC wafers in 1989, and majority of the development of SiC semiconductor electronics took place afterwards. One of the main advantages of SiC fabrication technology is that many Si process techniques can be applied to SiC process. This chapter presents an overview of the microfabrication process technology of SiC BJT devices. A baseline six-mask fabrication process is described to manufacture the proposed devices. Some issues with SiC dry etching, metallization and surface passivation are addressed. It is worth noting that some fabrication limitations described here are due to the technological limits of the semiconductor fabrication tools used in the microfabrication process. Advanced tools would allow better fabrication process in the future.

## 3.1 Fabrication Process Flow of SiC Bipolar Junction Transistors

The devices were fabricated on 4° off-axis Si-face n-type 4H-SiC wafer purchased from SiCrystal AG. The fabrication process for manufacturing the SiC BJTs is based on surface micromachining techniques, and a baseline six-mask fabrication process is described as follows. The cross-sectional process flow is shown in Figure 3-1.

Figure 3-1. Cross-sectional process flow of the SiC BJT.

- 1. The process starts with a 4H-SiC wafer with designed epitaxial layers on top. The epitaxial layers were grown by Ascatron AB using chemical vapor deposition (CVD). The diffusion coefficients of impurities in SiC are negligible at temperatures below approximately 1800 °C [42]. Therefore, diffusion process is not considered as a doping method for SiC devices. To get the proper doping concentration, ion implantation and epitaxial growth are generally used in SiC devices. In this work, the doping profiles are formed by epitaxial growth to avoid the post-annealing step for ion implantation at extremely high temperatures (> 1600 °C) [55], [56].

- 2. There are three SiC etching steps in the fabrication process. The first one is used to

define the emitter mesa. First, a 1-µm-thick oxide layer was deposited by plasma enhanced chemical vapor deposition (PECVD) method. Next, the oxide layer was patterned using standard photolithography step and etched by reactive ion etching (RIE) method. A positive photoresist OiR 10i (I-Line) was used. Before spin casting the photoresist, wafers were dried and treated with hexamethyldisilazane (HMDS) vapor coating to promote adhesion of the photoresist. A Karl Suss MA6 Mask Aligner was used for the photolithography step. The patterned oxide layer acted as a hard mask for the following SiC etching step. Then, the first dry etching step of SiC was performed by a transformer coupled plasma (TCP) etcher using hydrogen bromide (HBr) and chlorine (Cl<sub>2</sub>) as process gases. This step is to pattern the first N+SiC epitaxial layer, which forms the emitter regions of SiC BJTs. The standard etch rate of SiC is around 90 nm/minute and the selectivity of SiC over oxide is about 3:1. Finally, the oxide mask was removed by 5:1 buffered hydrogen fluoride (HF) solution. It is worth noting that no etch stop layers exist in between different epitaxial 4H-SiC layers. Therefore, the etching thickness is controlled by doing a timed etch.

- 3. The second TCP etching of SiC is similar to step 2. It is used to etch through the second and the third SiC epitaxial layers to form the base and collector mesa for the SiC BJT.

- 4. The third TCP etching of SiC is also similar to step 2. It is used to etch through the fourth SiC epitaxial layer to isolate the devices.

- 5. A 50-nm-thick oxide layer was deposited using PECVD method. The process gases were nitrous oxide (N<sub>2</sub>O), silane (SiH<sub>4</sub>) and argon (Ar). This thin oxide layer is used to passivate the device. It has been shown that the interface traps existing between SiC patterns and the oxide layer have a large impact on the device performance. The trap density can be reduced if dry oxidation is used or a high temperature annealing step is performed after the oxide deposition. PECVD oxide is used in this work due to limitations of the equipment in our lab.

- 6. The passivation oxide layer was then patterned. First, photoresist was spin casted onto the wafer and standard photolithography step was used to pattern the photoresist. Then the oxide layer was etched by RIE using tetrafluoromethane (CF<sub>4</sub>) and trifluoromethane (CHF<sub>3</sub>). The standard etch rate of the oxide is about 300 nm/minute and the selectivity of oxide over photoresist is around 5:1.

- 7. The first metallization step is used to form good ohmic contacts for n-type SiC. A 100-nm-thick nickel (Ni) layer was deposited using E-beam evaporation. Then it was patterned by photolithography and lift-off processes. To obtain good ohmic contacts with low resistivity, a rapid thermal annealing (RTA) step was performed for 1 minute in Ar ambient at 1000 °C.

- 8. The second metallization step is used to form good ohmic contacts for p-type SiC. A nickel/titanium/aluminum metal stack was deposited using E-beam evaporation. Then

it was patterned by photolithography and lift-off processes. To obtain good ohmic contacts with low resistivity, a RTA step was performed for 1 minute in Ar ambient at 800 °C.

#### 3.2 Fabrication Challenges

There are three main challenging steps in the fabrication process. It is important to overcome these challenges for enhancing device functionality and performance. These steps are dry etching of SiC, metallization and surface passivation. In this section, these fabrication challenges are first introduced and then addressed.

#### 3.2.1 Etching of Silicon Carbide

The strong chemical bond between Si and C makes SiC very hard to be etched. There are no known wet chemicals that can etch single crystal SiC at room temperature. The wet etching of SiC has to be done using high-temperature (> 300 °C) and corrosive mixtures, which are hard to handle. Also, only a few materials can be used as masks. Therefore, dry

Figure 3-2. Schematic of TCP etching system (Lam Research) [63].

etching is the commonly used method to pattern SiC to fabricate SiC electronic devices.

In the early years, reactive ion etching (RIE) was commonly used to etch SiC using fluorinated plasmas [57], [58]. However, rough surfaces were often observed due to the high dc self-bias. With the advent of high-density plasma etching systems, such as electron cyclotron resonance (ECR) etcher, and transformer/inductively coupled plasma (TCP/ICP) etcher, significant improvements of the etching rate and the etching profile of SiC materials were obtained [59]-[62]. The key advantage of these high-density plasma systems is the decoupling of ion density and ion energy. In a TCP/ICP etcher, the high-density plasmas are generated by an inductive coil where RF power is applied. For TCP etchers, the inductive coils are mounted on the top of the plasma chamber. Whereas for ICP etchers, the inductive coils are mounted on the outside of the chamber. The ion energy is controlled by a separate RF power source that is connected to the wafer platen. Therefore, high-density and low-energy ion flux can be obtained, which is expected to achieve high etch rates and low surface damage at the same time. In this work, a TCP etcher from Lam Research is used. A schematic of the TCP etching system is shown in Figure 3-2.

Conventional mask materials for dry etching, such as hard-baked photoresist, SiO<sub>2</sub> and silicon nitride (Si<sub>3</sub>N<sub>4</sub>), are usually etched at higher rates than SiC in fluorine-based plasma chemistries. This is the reason why metal mask was used in some SiC etching processes. However, the residual metal leads to contamination in the subsequent process steps. As a result, etching process using a metal mask is not allowed in most laboratories. In addition, it has also been observed that due to sputtering of metal material onto the surface of SiC sample, grass-like structures are formed during the etching process. This is known as the *micromasking phenomenon*. Hence, it is of great importance to develop a

Figure 3-3. Scanning electron microscopy (SEM) image of the etching profile showing the trench effect.

Figure 3-4. SEM image of the etching profile without trench effect.

dry etching process with high selectivity and nonmetallic mask. Hydrogen bromide (HBr) and chlorine (Cl<sub>2</sub>) based dry etching chemistry has been widely used to etch Si material with high etch rate and high selectivity to SiO<sub>2</sub>. Therefore, HBr and Cl<sub>2</sub> based chemistry is studied to etch SiC using SiO<sub>2</sub> as the mask material in this work. By changing the percentage of Cl<sub>2</sub> in the gas mixture, different etch rate, selectivity and etch profile can be obtained. Based on the previous study of dry etching of polycrystalline 3C-SiC by Gao et al. [61], [62], two etching recipes for crystalline 4H-SiC have been developed and tested. One common problem of TCP etching of SiC material is the so-called trench effect. which occurs at the bottom of the etched features along the sidewalls. The scanning electron microscopy (SEM) image of the etching profile in Recipe 1 is shown in Figure 3-3. Though a considerably high etch rate of about 120 nm/minute, a high selectivity of 2.3:1 and a profile angle of 80.8° have been achieved, the trench effect cannot be ignored. As shown in Figure 3-3, a trench of 250 nm in depth is observed after the crystalline SiC material has been etched for 1.28 um. This recipe is preferred in many MEMS process due to the high etch rate and steep profile angle, but the deep trenches will cause many problems in electronic devices. Recipe 2 is then developed for fabricating SiC electronic devices. In Recipe 2, the gas flow of Cl<sub>2</sub> is reduced to 0, which completely removes the trenches. The SEM image of the etching profile using Recipe 2 is shown in Figure 3-4. An etch rate of around 90 nm/minute, a high selectivity of 3:1 and a profile angle of 72° have been achieved using Recipe 2. The two etching recipes are summarized in Table 3-1. As mentioned in the previous section, no etch stop layers exist in between different epitaxial 4H-SiC layers. The etching thickness is controlled by doing a timed etch. Therefore, an etch rate of about 90nm/minutes is preferred though a higher etch rate can be obtained by using a higher bias power.

| Table 3-1. Summary | of the etching  | recipes of c   | rystalline 4H-SiC   |

|--------------------|-----------------|----------------|---------------------|

| Tuoto 5 1. Summing | or the eterning | , recipes or c | i journine ill bic. |

|                                      | Recipe 1 | Recipe 2 |

|--------------------------------------|----------|----------|

| Chamber Pressure [mtorr]             | 12       | 12       |

| TCP Source Power [W]                 | 300      | 300      |

| Bias Power [W]                       | 150      | 150      |

| Bottom Electrode Temperature [°C]    | 40       | 40       |

| HBr Gas Flow Rate [sccm]             | 125      | 200      |

| Cl <sub>2</sub> Gas Flow Rate [sccm] | 75       | 0        |

| Etch Rate [nm/minute]                | ~ 120    | ~ 90     |

| Selectivity of SiC/SiO <sub>2</sub>  | ~ 2.3:1  | ~ 3:1    |

| Profile Angle                        | 81       | 72       |

#### 3.2.2 Metallization

For SiC-based devices, one of the critical challenges is to develop chemically and electrically stable ohmic contacts with low electrical resistance. Some important factors need to be taken into consideration, such as surface preparation, choice of metal and annealing temperature. The quality of ohmic contacts is very important for the performance and operation of the devices at high temperature.

Surface preparation is required because the metal needs to be intimately in contact with the semiconductor. Therefore, the sample surface needs to be free of photoresist residue and native oxide. A descum process using oxygen (O<sub>2</sub>) plasma was performed after developing exposed photoresist to eliminate any residual scum. Then the sample was dipped in buffered hydrogen fluoride solution for 30 seconds right before it was sent into the chamber for metal deposition. There are different techniques for depositing metal layers. E-beam evaporation is used in this work, which provides high deposition rate, precise control of film thickness and low as-deposited sheet resistance. Sputtering is an alternative option that has better step coverage and good adhesion of the metal to the substrate, but it is hard to precisely control the deposited film thickness. Lift-off process was used to pattern the metal contact. High temperature annealing process was performed at temperatures around 700 – 1050 °C in an oxygen-free ambient for reaction between metal and SiC to form silicides. The choices of metal and high temperature annealing condition are both critical for obtaining good ohmic contacts with low resistivity. For ntype SiC, Ni based metal stacks are commonly used and the typical specific contact resistance is in the range of  $10^{-4} - 10^{-5} \Omega \text{cm}^2$  [64]-[69]. For p-type SiC, the specific contact resistance is usually higher than that of n-type. Al based metal stacks are commonly used for p-type SiC and the typical specific contact resistance is in the range of  $10^{-3} - 10^{-4} \Omega \text{cm}^2$  [67]-[71].

#### Transfer Length Method (TLM)

For an ohmic contact with a total contact resistance of  $R_c$ , it is usually characterized by specific contact resistance  $\rho_c$  given by

$$\rho_c = R_c A, \tag{3.1}$$

where A is the contact area. The benefit of using  $\rho_c$  instead of  $R_c$  is the capability of evaluating contacts with different contact area.

Transfer length method (TLM) is widely used for the characterization of ohmic contacts. A typical TLM test structure consists of several contacts with unequal spacing between them. The total resistances between adjacent contacts are measured and have a linear dependence on the contact spacing. A schematic of a TLM test structure and a plot of total resistance as a function of contact spacing are shown in Figure 3-5 [72]. TLM test structures are fabricated on the same die together with SiC BJT devices.

For contacts with  $L \ge 1.5L_T$ , the total resistance  $R_T$  between any two contacts can be expressed as

$$R_T = \frac{R_{sh}d}{Z} + 2R_c \approx \frac{R_{sh}}{Z} (d + 2L_T), \tag{3.2}$$

where  $R_{sh}$  is the sheet resistance of the semiconductor, Z is the width of contacts, d is the spacing between any two adjacent contacts and  $L_T$  is the transfer length that can be determined as the intercept value with x-axis in Figure 3-5.  $R_c$  can also be determined from the TLM measurement as the intercept value with y-axis:

Figure 3-5. Schematic of a transfer length method test structure and a plot of total resistance  $(R_T)$  vs. contact spacing (d) [72].

$$R_T(d=0) = 2R_c = 2\frac{R_{sh}}{Z}L_T. {(3.3)}$$

The sheet resistance can be obtained by solving Equation (3.3):

$$R_{sh} = \frac{R_c Z}{L_T}. ag{3.4}$$

The potential distribution under the contact is such that the voltage is the highest near the contact edge and drops nearly exponentially with distance. The transfer length  $L_T$  is defined as the "1/e" distance of the voltage curve:

$$L_T = \sqrt{\rho_c / R_{sh}}. ag{3.5}$$

Thus, the specific contact resistance  $\rho_c$  can also be obtained by TLM:

$$\rho_c = L_T^2 R_{sh}. \tag{3.6}$$

#### Characterization Results for Ohmic Contacts