# Ultra-low Power Wake-up Radio for Low Activity Wireless System

Wenting Zhou

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-177 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-177.html

December 1, 2016

# Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Ultra-low Power Wake-up Radio for Low Activity Wireless System

By

#### Wenting Zhou

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Jan M. Rabaey, Chair

Professor Elad Alon

Professor Paul K. Wright

Fall 2014

# The dissertation of Wenting Zhou is approved.

| Chair | Date |

|-------|------|

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       | Date |

University of California, Berkeley

Fall 2014

## Ultra-low Power Wake-up Radio for Low Activity Wireless System

Copyright ©2014 by Wenting Zhou

#### **Abstract**

Ultra-low Power Wake-up Radio for Low Activity Wireless System

by

#### Wenting Zhou

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Science

University of California, Berkeley

Professor Jan M. Rabaey, Chair

Recent advances in low power radio design have enabled a broad range of low activity applications such as smart utilities, health monitoring, building and industry automation, automotive control and monitoring, wireless control and etc. The key challenge to implement these applications is to reduce the average power consumption spent on wireless communications. A traditional way to solve this is to implement protocol based duty cycling which leads to a tradeoff between reduced average power consumption and increased system latency. A smarter solution is to use a dedicated wake-up receiver continuously monitoring the channel and activating the main receiver upon detection of a wake-up signal. The use of a wake-up receiver helps to improve the overall power performance while keeping the system latency bounded.

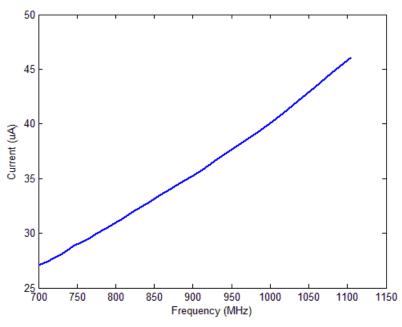

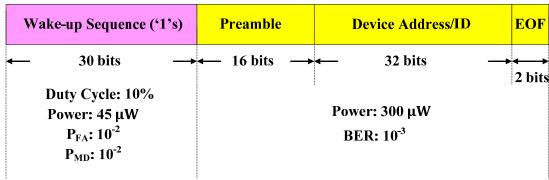

This dissertation addresses challenges and concerns of designing an ultra-low power high performance wake-up radio. It proposes a two-step wake-up architecture including energy detection mode and address detection mode to reduce the active power dissipation meanwhile improving the robustness and reliability of the system. Design metrics has been provided to serve as a guideline for detailed circuit implementations. Based on that, a wake-up radio prototype has been built in TSMC 65nm standard CMOS targeting 915MHz band for IEEE 802.15.4g. This prototype focuses on improving the sensitivity performance at an ultra-low power level. It consumes only 45 $\mu$ W in energy detection mode. With 20 $\mu$ s detection time, it is able to achieve a sensitivity of -90dBm at 10-2 error rates. In address detection mode, it consumes 300  $\mu$ W and is able to achieve a sensitivity of -74.5dBm at 10-3 BER.

To my beloved parents and husband

# **Contents**

# List of Figures

### List of Tables

| Chapter 1 I | ntroduction                                           | 1  |

|-------------|-------------------------------------------------------|----|

| 1.1 Mo      | tivation                                              | 1  |

| 1.2 Pro     | tocol Based Duty-Cycling Vs Reactive Wake-up Receiver | 2  |

|             | sertation Outline                                     |    |

| Cht 2 C     | and and I are Decim                                   | 7  |

| 2.1 Des     | ystem Level Design                                    | /  |

|             | sign Consideration                                    |    |

| 2.1.1       | System Integration                                    |    |

| 2.1.2       | Active Power Oriented                                 |    |

| 2.1.3       | Performance Metrics                                   |    |

| 2.1.4       | Sensitivity                                           |    |

|             | posed Two-Step WuRx                                   |    |

|             | sign Metrics                                          |    |

| 2.4 Sur     | nmary                                                 | 17 |

| Chapter 3 F | Receiver for Energy Detection Mode                    | 18 |

| _           | hitecture Development                                 |    |

| 3.1.1       | Passive Rectifier                                     | 18 |

| 3.1.2       | Tuned Radio Frequency (TRF) Receiver                  | 19 |

| 3.1.3       | Super-Regenerative Receiver                           | 20 |

| 3.1.4       | Superheterodyne Receiver                              |    |

| 3.1.5       | Proposed Architecture                                 |    |

| 3.2 Ser     | sitivity Analysis                                     |    |

| 3.2.1       | Theoretical Model for Energy Detection                |    |

| 3.2.2       | Simulation Result                                     |    |

| 3.2.3       | Performance Boundary                                  |    |

|             | cuit Design                                           |    |

| 3.3.1       | Input Matching Network                                |    |

| 3.3.2       | Passive Mixer                                         |    |

| 3.3.3       | Current Starved Oscillator                            |    |

| 3.3.4       | IF Amplifiers                                         |    |

| 3.3.5       | Envelope Detector                                     |    |

| 3.3.6       | Integrator                                            |    |

| 5.5.0       |                                                       |    |

| 3.4       | Summary                                            | 57 |

|-----------|----------------------------------------------------|----|

|           |                                                    |    |

| Chapter 4 | Receiver for Address Detection Mode                | 58 |

|           | Architecture Development                           |    |

| 4.2 (     | Circuit Design                                     |    |

| 4.2.1     | Injection Locked Oscillator                        | 61 |

| 4.2.2     | IF Stages                                          | 64 |

| 4.2.3     | Digital Demodulator                                | 66 |

| 4.2.4     | <del>-</del>                                       |    |

| 4.2.5     | Baseband Synchronization                           | 69 |

| 4.3       | Gummary                                            |    |

| Chapter 5 | Measurement Result                                 | 71 |

| 5.1 I     | Frequency Response                                 | 71 |

| 5.2 I     | LO Measurement                                     | 73 |

| 5.3 I     | Receiver Sensitivity in Energy Detection Mode      | 75 |

|           | Receiver Sensitivity in Address Detection ModeMode |    |

|           | Performance Summary                                |    |

| Chapter 6 | 6 Conclusions and Future Work                      | 84 |

| 6.1 I     | Research Summary                                   | 84 |

|           | Future Work                                        |    |

| Bibliogra | phy                                                | 87 |

# **List of Figures**

| Figure 1.1 Protocol Based Duty-Cycling Example: CSL for 802.15.4e                              | 2  |

|------------------------------------------------------------------------------------------------|----|

| Figure 1.2 Protocol Based Duty-Cycling Example: RIT for 802.15.4e                              |    |

| Figure 1.3 Communication with Reactive Wake-up Receiver                                        |    |

| Figure 1.4 Performance Comparison between Protocol Based Duty-Cycling and Rea                  |    |

| Wake-up Receiver                                                                               |    |

| Figure 2.1 System Integration with WuRx                                                        | 8  |

| Figure 2.2 Performance of Recently Published Low Power Receivers                               |    |

| Figure 2.3 Wake-up Scheme with Simple Energy Detection                                         | 11 |

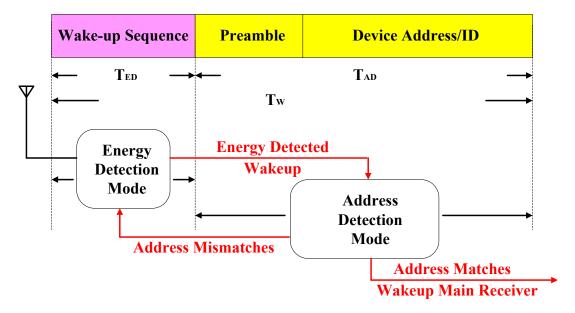

| Figure 2.4 Wake-up Scheme with Proposed Two-Step WuRx                                          |    |

| Figure 2.5 Wake-up Frame for Proposed Two-Step WuRx                                            |    |

| Figure 2.6 Six Different Working Categories for WuRx                                           | 13 |

| Figure 2.7 Six Different Working Categories for WuRx                                           | 16 |

| Figure 2.8 Six Different Working Categories for WuRx                                           |    |

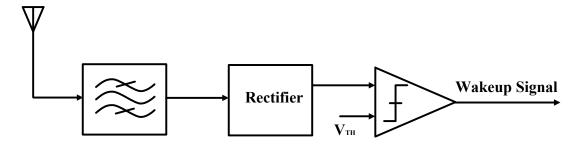

| Figure 3.1 Passive Rectifier Based Receiver                                                    | 19 |

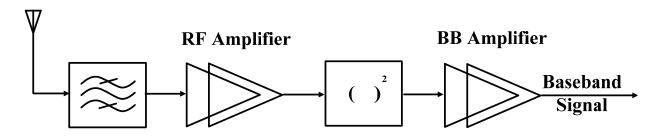

| Figure 3.2 Tuned Radio Frequency (TRF) Receiver                                                | 19 |

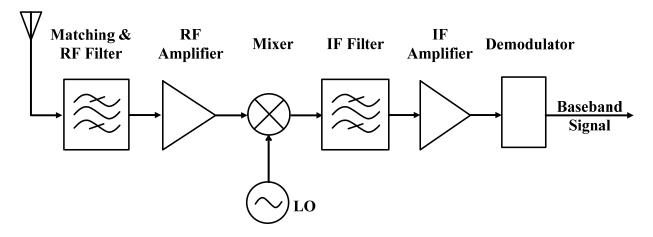

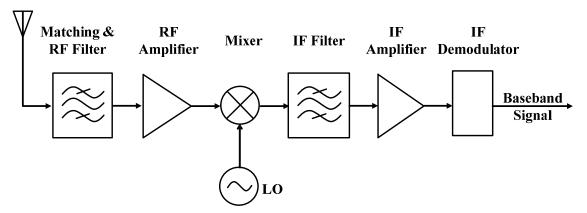

| Figure 3.4 Single Conversion Superheterodyne Receiver                                          | 21 |

| Figure 3.5 Wideband-IF Receiver                                                                | 22 |

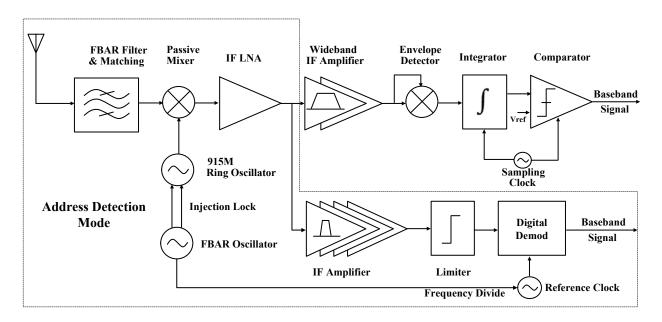

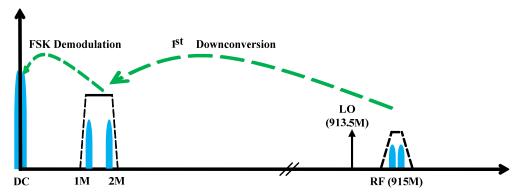

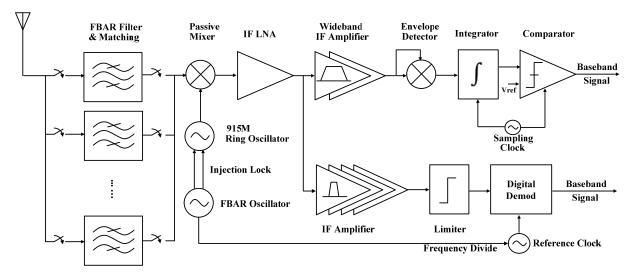

| Figure 3.6 Proposed Receiver Architecture in Energy Detection Mode                             | 24 |

| Figure 3.7 Frequency Planning for Receiver in Energy Detection Mode                            | 24 |

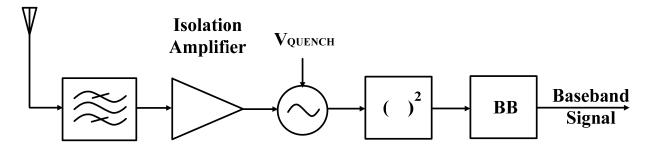

| Figure 3.3 Super-Regenerative Receiver                                                         | 20 |

| Figure 3.8 Theoretical Model for Energy Detection                                              | 26 |

| Figure 3.9 Probability of Miss Detection ( $P_m$ ) and Probability of False Alarm ( $P_f$ ) Vs |    |

|                                                                                                |    |

| Figure 3.10 Detection Error Rate (DER) Vs Decision Threshold Factor $\beta$ for                |    |

| Figure 3.11 Detection Error Rate Vs Decision Threshold Factor β for                            |    |

| Figure 3.12 Detection Error Rate Vs SWNR for Various Integration Time                          |    |

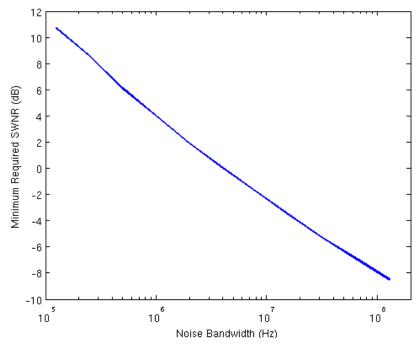

| Figure 3.13 Minimum Required SWNR Vs Noise Bandwidth for 0.1% DER                              |    |

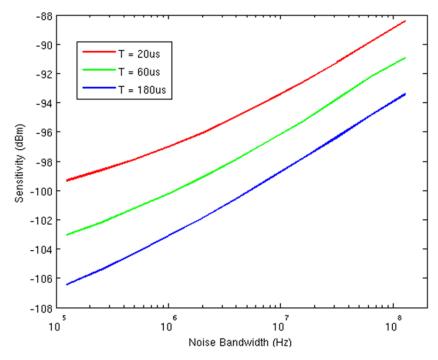

| Figure 3.14 Receiver Sensitivity@ 0.1% DER Vs Noise Bandwidth for Various Integ                |    |

| Time                                                                                           |    |

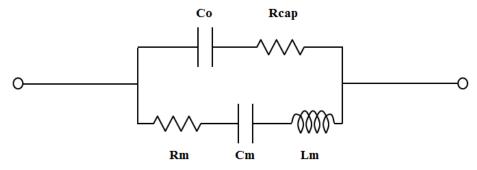

| Figure 3.15 FBAR Resonator Circuit Equivalent Model                                            | 38 |

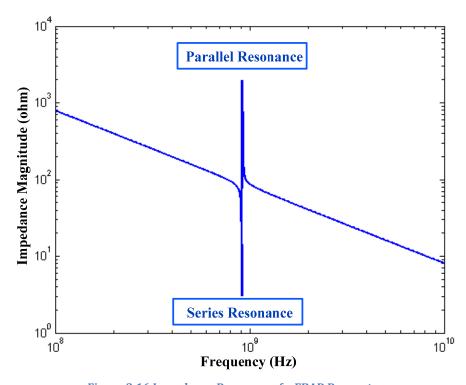

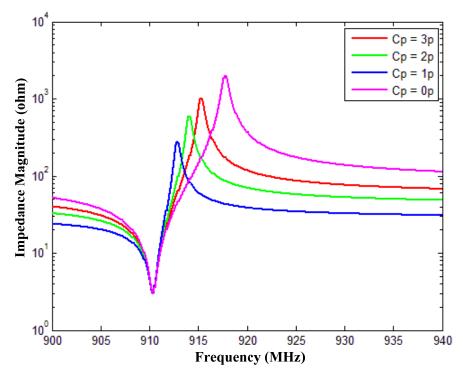

| Figure 3.16 Impedance Response of a FBAR Resonator                                                      | 39       |

|---------------------------------------------------------------------------------------------------------|----------|

| Figure 3.17 Impedance Response of FBAR resonator with Different Shunt Capacitan                         |          |

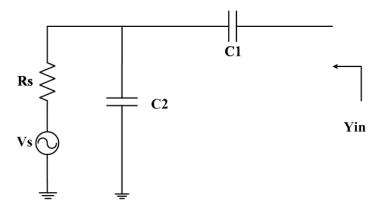

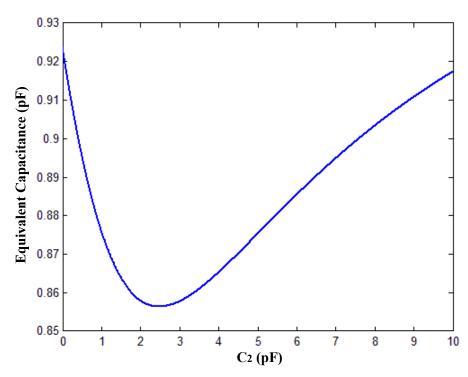

| Figure 3.18 Schematic of Capacitive Transformer                                                         |          |

| Figure 3.19 Equivalent Capacitance from Capacitive Transformer Network with C <sub>1</sub> <sup>2</sup> |          |

| f=915M                                                                                                  |          |

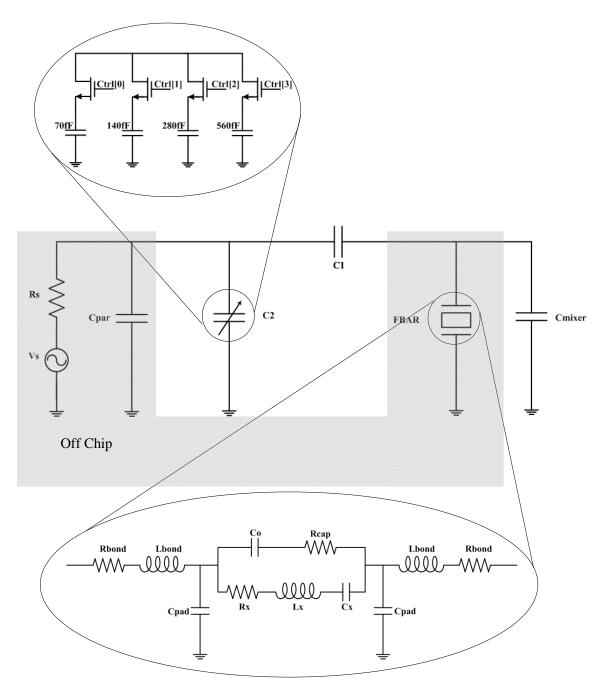

| Figure 3.20 Complete schematic of FBAR resonate input matching network with pa                          | rasitics |

|                                                                                                         | 43       |

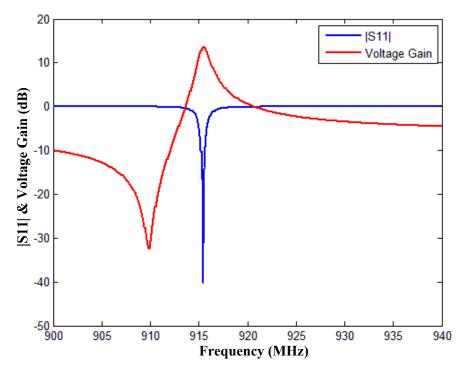

| Figure 3.21 Simulated S11 and voltage gain                                                              | 44       |

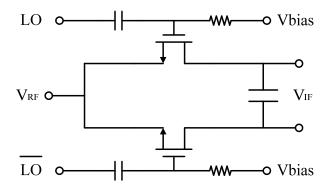

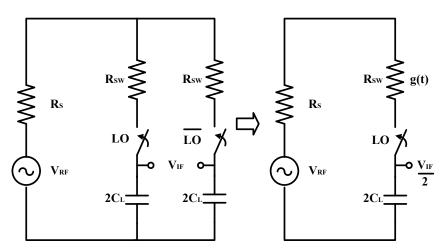

| Figure 3.22 Schematic of single balanced passive mixer                                                  |          |

| Figure 3.23 Equivalent circuit model for single-balanced passive mixer                                  |          |

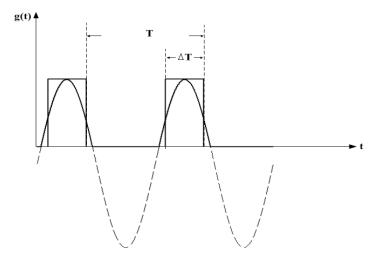

| Figure 3.24 Switching conductance waveform                                                              | 46       |

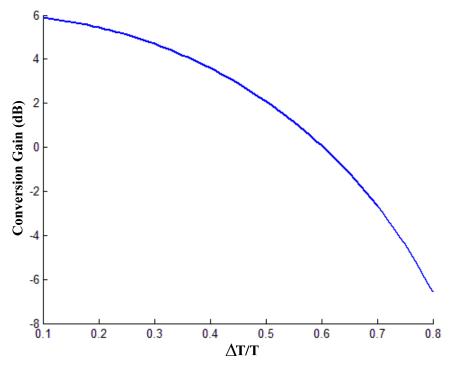

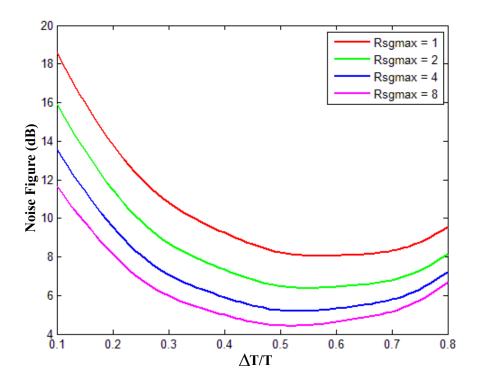

| Figure 3.25 Conversion gain of a single balanced passive mixer with different $\Delta T/T$              |          |

| Figure 3.26 Noise figure of a single balanced passive mixer with different ΔT/T and                     |          |

|                                                                                                         | _        |

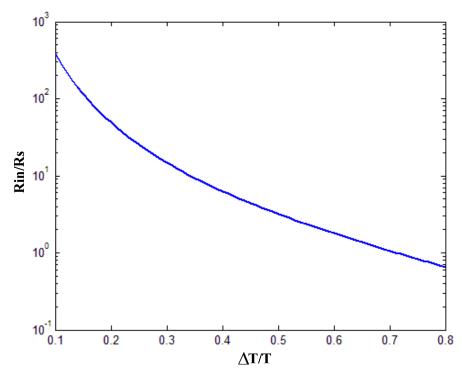

| Figure 3.27 Input impedance of a single balanced mixer with different ΔT/T                              | 50       |

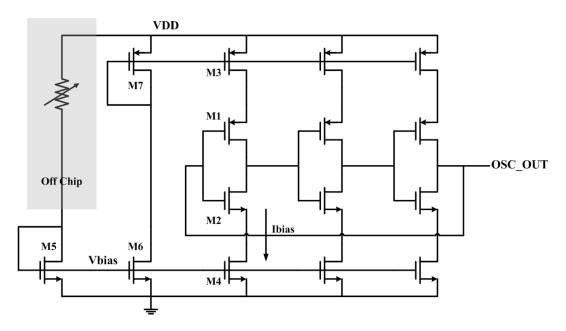

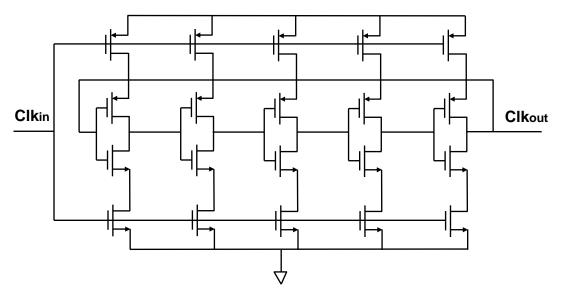

| Figure 3.28 Schematic of current starved ring oscillator                                                | 51       |

| Figure 3.29 Schematic of differential oscillator                                                        | 51       |

| Figure 3.30 Schematic of IF Amplifiers                                                                  | 53       |

| Figure 3.31 Simulated IF Amplifier Frequency Response                                                   | 53       |

| Figure 3.32 Schematic of Envelope Detector                                                              |          |

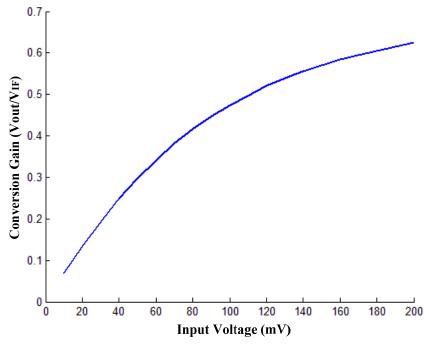

| Figure 3.33 Conversion Gain of Envelope Detector                                                        | 55       |

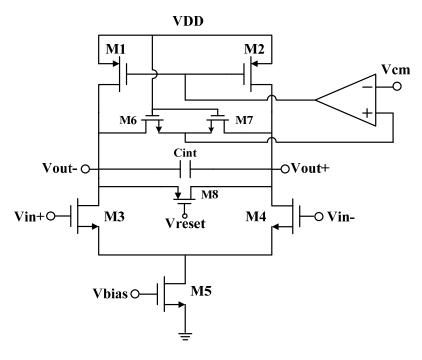

| Figure 3.34 Schematic of Integrator                                                                     | 55       |

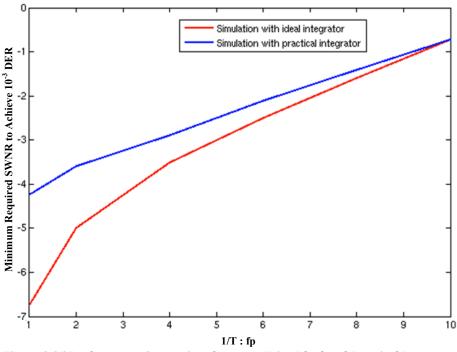

| Figure 3.35 Performance Comparison between Using Ideal and Practical Integrator                         | ·57      |

| Figure 4.1 Direct Conversion Architecture                                                               | 59       |

| Figure 4.2 Low-IF Architecture                                                                          |          |

| Figure 4.3 Proposed Receiver Architecture in Address Detection Mode                                     |          |

| Figure 4.4 Frequency Planning for Receiver in Address Detection Mode                                    |          |

| Figure 4.5 Model of an Oscillator                                                                       | 61       |

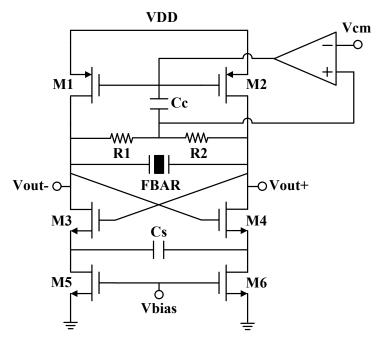

| Figure 4.6 Schematic of Differential FBAR Oscillator                                                    | 61       |

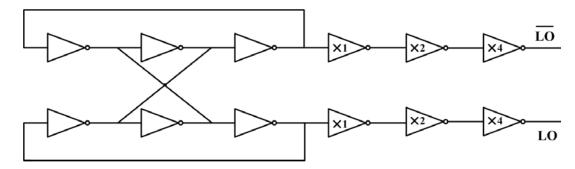

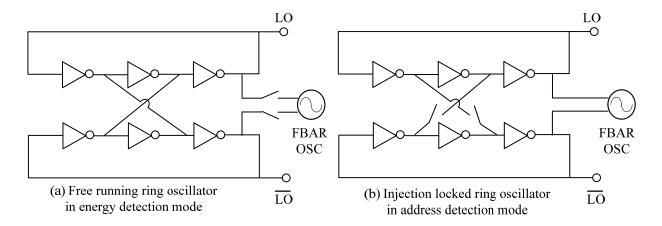

| Figure 4.7 Ring Oscillator in Different Working Mode                                                    |          |

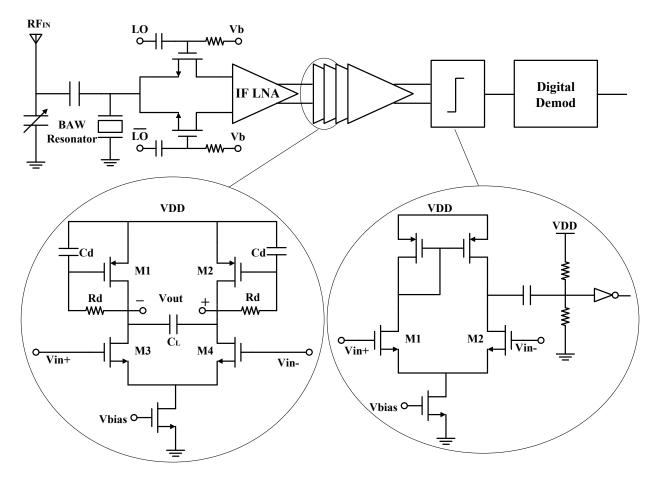

| Figure 4.8 Schematic of IF Stages                                                                       | 64       |

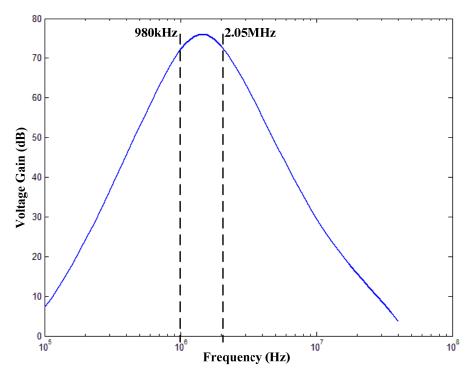

| Figure 4.9 Simulated IF Amplifier Frequency Response                                                    | 65       |

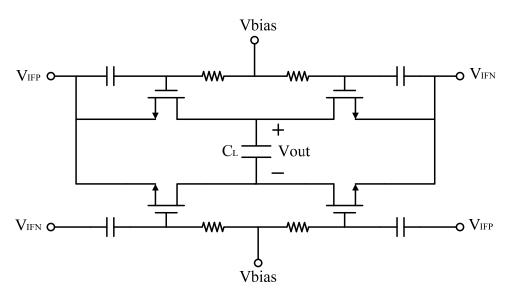

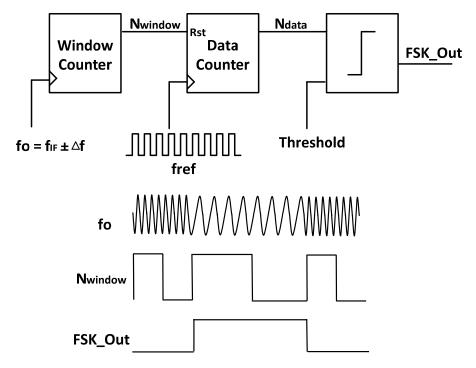

| Figure 4.10 Digital FSK Demodulator                                                                     | 66       |

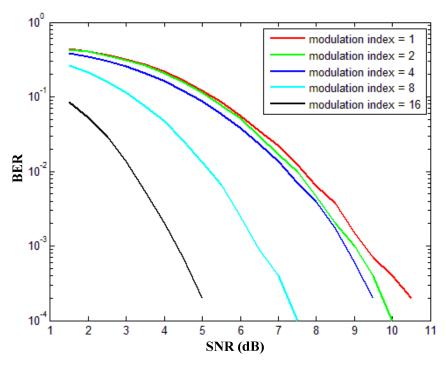

| Figure 4.11 BER Vs SNR for FSK Demodulator with Different Modulation Index                              | 67       |

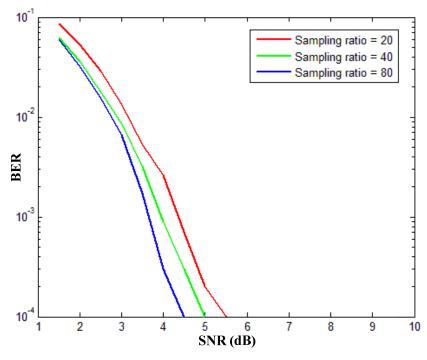

| Figure 4.12 BER Vs SNR for FSK Demodulator with Different Sampling Ratio                                |          |

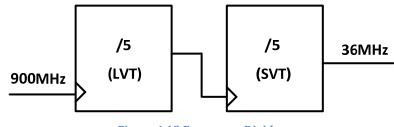

| Figure 4.13 Frequency Divider                                                                           | 69       |

| Figure 4.14 Schematic of Dividing by 5 Core                                                             | 69       |

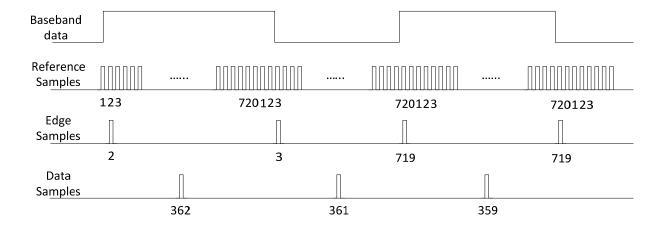

| Figure 4.15 Scheme of Digital Synchronization                                                           | 70       |

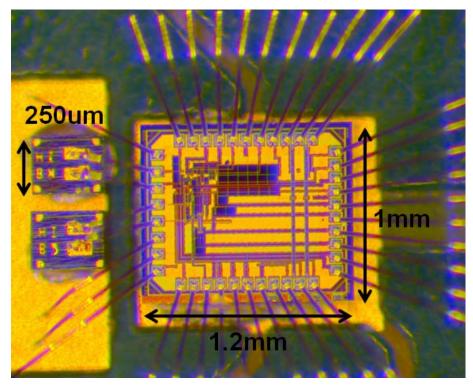

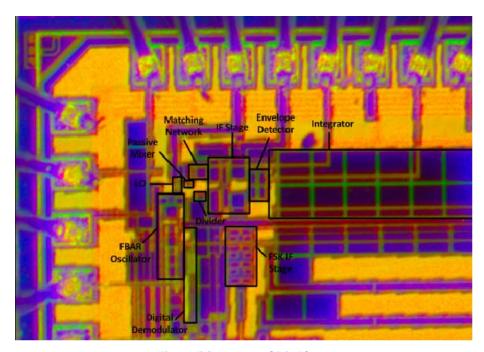

| Figure 5.1 Die Photo of Receiver Prototype Bonded to Packaged FBAR Resonators        | 72   |

|--------------------------------------------------------------------------------------|------|

| Figure 5.2 Annotated Die Photo                                                       | 72   |

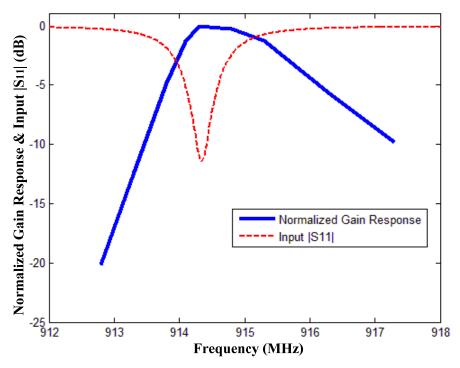

| Figure 5.3 Measured  S <sub>11</sub>   and Gain Frequency Response                   | 73   |

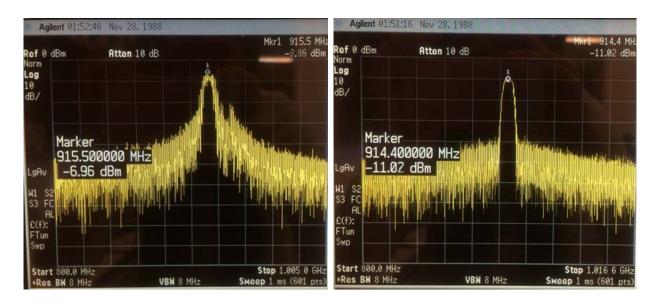

| Figure 5.4 Measurement Result of Three-Stage Ring Oscillator                         | 74   |

| Figure 5.5 Output Spectrum When Oscillator is (left) Free Running and (right) Locked | 74   |

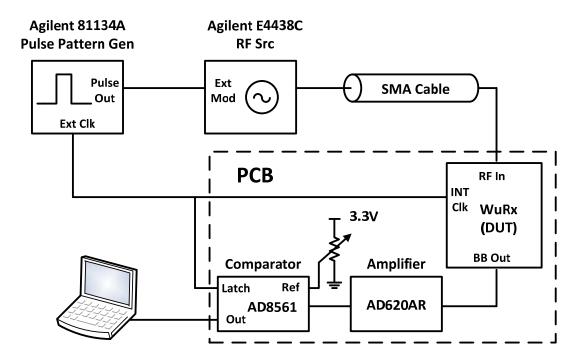

| Figure 5.6 Test Setup for PFA and PMD Measurements in Energy Detection Mode          | 75   |

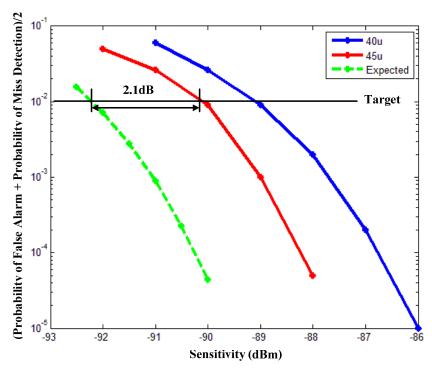

| Figure 5.7 Measured Error Rate versus Sensitivity for Different Power Consumption    | 76   |

| Figure 5.8 Measured Error Rate versus Sensitivity for Different Integration Time     | 76   |

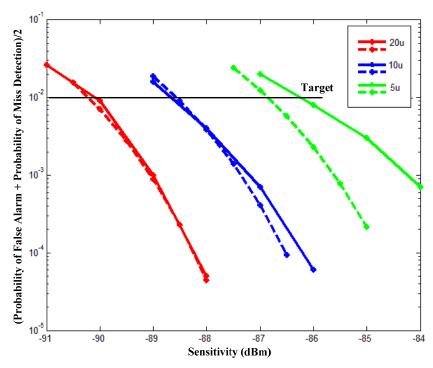

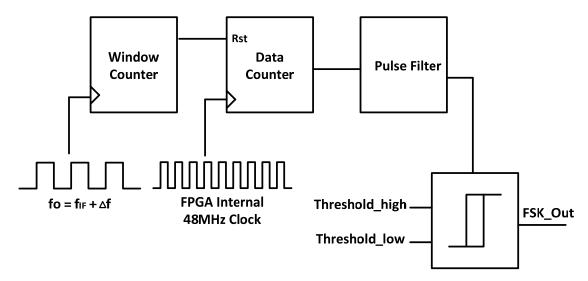

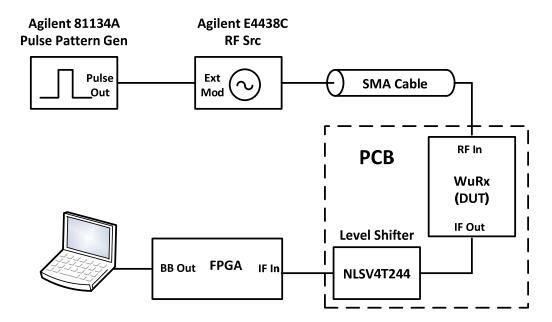

| Figure 5.9 Revised FSK Demodulator Implemented on FPGA                               | 78   |

| Figure 5.10 Test Setup for BER Measurement in Address Detection Mode                 | . 78 |

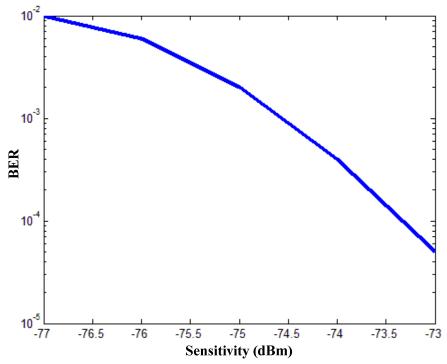

| Figure 5.11 Measured BER versus Sensitivity                                          | 79   |

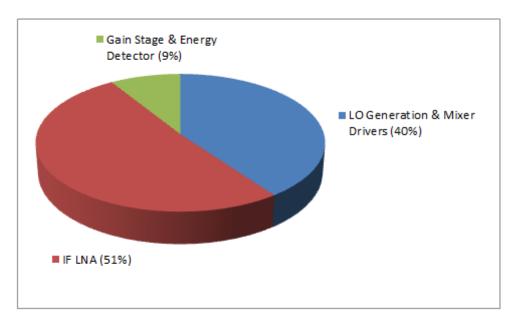

| Figure 5.12 Receiver Power Breakdown in Energy Detection ModeMode                    | 80   |

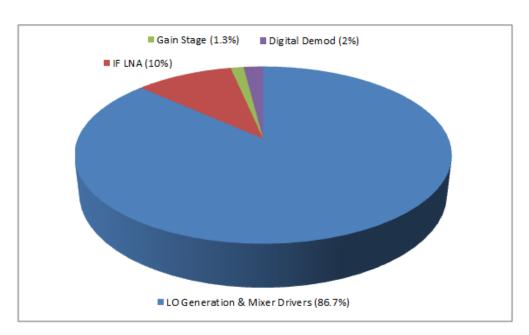

| Figure 5. 13 Receiver Power Breakdown in Address Detection Mode                      |      |

| Figure 6.1 A Novel Wake-up Frame Design Example                                      | 85   |

| Figure 6.2 MEMS Based Multi-channel Wake-up Radio                                    | 86   |

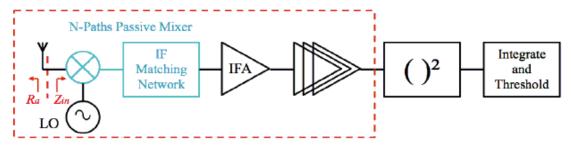

| Figure 6.3 Crystal-less Energy Detection Receiver                                    | 86   |

# **List of Tables**

| Table 2.1 Specification of WuRx Prototype                           | 9  |

|---------------------------------------------------------------------|----|

| Table 2.2 Specification of Proposed WuRx in Different Modes         |    |

| Table 3.1 Typical Parameter Values for a 920MHz FBAR Resonator      | 38 |

| Table 3.2 Performance Summary of a 920MHz FBAR Resonator            |    |

| Table 5.1 Performance Summary of Receiver in Energy Detection Mode  | 80 |

| Table 5.2 Performance Comparison of Energy Detection Receiver       |    |

| Table 5.3 Performance Summary of Receiver in Address Detection Mode |    |

| Table 5.4 Performance Comparison of Address Detection Receiver      |    |

#### **Acknowledgments**

I would like to take this opportunity to express my gratitude to many people who have supported me throughout my graduate career, and without whom this thesis would not have been possible.

First and foremost, my sincere gratitude goes to my advisor, Professor Jan M. Rabaey for his consistent support and guidance during my study at Berkeley. I benefited tremendously from his vision and ability to dream big. His unwavering high standard has been admirable. I am also grateful to Professor Elad Alon and Professor Paul K. Wright for being my committee, giving valuable feedbacks and reviewing my dissertation. I would like to thank Professor Anant Sahai to serve as my qualify exam chair.

Many BWRC member companies have given great support for this research project. Thanks to Lori Callaghan at Avago Technologies for providing MEMS resonators. Thanks to TSMC for chip donation. Thanks to Samsung and Panasonic for funding this project.

I would also like to appreciate many students and staffs from BWRC; more specifically, Jesse Richmond, Camilo Salazar for helpful discussion on project ideas; Yue Lv, Wen Li, Steven Callender for help in chip taping out and broad design; Fred Burghardt, Brian Richard for CAD tools and lab measurement support; fellow classmates: Lingkai Kong, Paul Liu, Jiashu Chen, Yida Duan, Hanh-Phuc Le, Ping-Chen Huang, Namseog Kim for being through the challenges together.

Apart from research life, I would like to thank Jing Yang, Shan Li, Yue Liu, Yaping Li, Hai Lin, Jenny Zhu for their contribution and support to make my life in Berkeley enjoyable and colorful.

I give special thanks to my master advisor Alex Lee at my days in Shanghai Jiaotong University. He guided me into the analog integrated circuit design and gave strong support for my graduate application. Without him, I could never come to my dream school.

Finally, I am forever grateful to my parents and my husband. My parents have always believed in whatever I do and given me endless love, encouragement and support in this long journey in Berkeley. My husband Feng is so kind, caring, loving and tremendously supportive when I made a decision to go overseas to pursue my Ph.D. degree. He has taken every opportunity and flown more than 300,000 miles in the past year to visit me despite of his busy career in Shanghai. I love him from the bottom of my heart and look forward to starting a new chapter in our story together.

# **Chapter 1**

# Introduction

#### 1.1 Motivation

Recent advances in low-power radio design have enabled a broad range of new applications, such as wireless senor networks (WSNs) [Rabaey02], wireless body area networks (WBANs) [IEEE12-1], wireless personal area networks (WPANs) [IEEE03] and etc. In many of these applications, the wireless nodes are used to monitor certain events which occur at low activity rate. The radio link remains inactive until events occurs and then information is gathered, processed and exchanged among nodes or between nodes and central hub with limited protocol overhead and communication delay. Such scenarios can be found in smart utilities, health monitoring, building and industry automation, automotive control and monitoring, wireless control, and many other applications. All these applications require extremely low power wireless nodes so as to last for years without battery recharge or replacement. Some applications require usage of energy harvesters to supplement or completely replace the battery, yet state-of-the-art energy harvesters, for example, sub-mm solar cells under moderate illumination can only provide up to 100µW power [Ingram11] for a wireless node. Therefore the key challenge to implement these low activity applications remains in designing a wireless node consuming the lowest amount of energy possible.

A classic wireless node implementation includes radios, sensing interfaces, memory, a processor and power management. Among all the functions, the dominant component is the wireless communication energy which is usually spent on data exchanging, idle monitoring, collision avoidance, control packet overhead, overhearing [Lin05]. For a typical low activity application, communications are sparse, in other words, the packet traffic load is usually light and packets are usually short. With such traffic characteristics, nodes will spend most of the time idle monitoring the channel. Therefore, the high-level goal of this research is to reduce the energy dedicated to the idle monitoring.

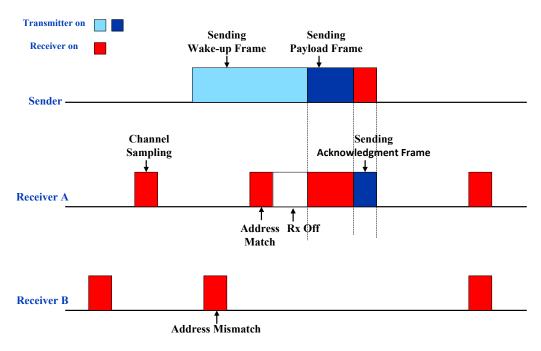

Figure 1.1 Protocol Based Duty-Cycling Example: CSL for 802.15.4e

### 1.2 Protocol Based Duty-Cycling Vs Reactive Wake-up Receiver

A traditional way to reduce the energy for idle monitoring is to implement protocol-based duty-cycling. Depending on the protocol, communication could be initiated by either the transmitting device or the receiving one. Taking 802.15.4e as an example, it provides two low-energy mechanisms: coordinated sampled listening (CSL) and receiver initiated transmission (RIT) [IEEE12-2].

Figure 1.1 shows an example of CSL. It allows the receiving device to periodically sample the channel for incoming transmissions at low duty cycles. If the channel sample does not detect energy on the channel, CSL disables the receiving device until the next channel sample. If the channel sample receives a wake-up frame, CSL checks the destination address in the wake-up frame. If it does not match, CSL disables receiver until the next channel sample. Otherwise, CSL disables receiving devices until the Rendezvous Time in the wake-up frame from now and then enables receiving device to receive the payload frame, send back a secure acknowledgment frame and return back to periodical channel sampling.

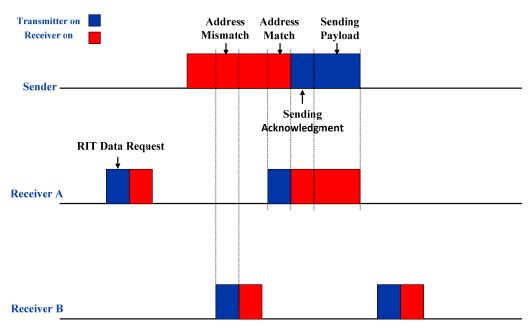

Figure 1.2 Protocol Based Duty-Cycling Example: RIT for 802.15.4e

Figure 1.2 shows another example of RIT. In RIT mode, a receiving device periodically transmits a RIT data request command and then listens to the channel for a while for an incoming frame at low duty cycles. If no incoming frame is detected, the device goes back to idle state till the next periodic transmission of RIT data request command. If an acknowledgment frame is received, the device stops periodic transmission and prepares to receive the payload frame. The transmitting device stays awake until it receives a RIT data request packet from the destination, and then sends out a secure acknowledgment and payload frames.

Both CSL and RIT utilize low duty-cycling of receiving node to reduce the energy dedicated to idle monitoring so as to reduce the total energy consumed by each node. CSL and RIT are used under different latency requirements. CSL is suitable for applications with a relatively low latency requirement, e.g., less than 1 second while RIT is suitable for applications with a high latency tolerance, e.g., tens of seconds. Although CSL and RIT are low energy mechanisms, significant energy may still be wasted on sender's side by sending long wake-up sequence or monitoring the channel long time for data request and on receiver's side by periodic channel sampling or sending data request. More importantly, there exists an inherent trade-off between average power consumption and average network latency. For many low latency applications, the protocol must be adjusted to increase duty-cycling of receiving node, thus increasing average power consumption.

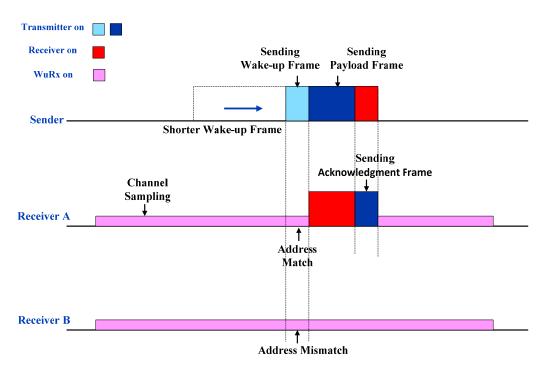

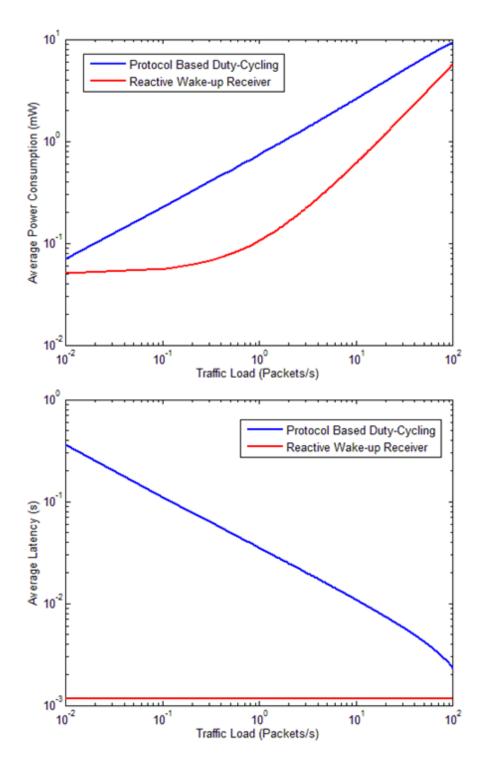

Figure 1.3 Communication with Reactive Wake-up Receiver

An alternative to protocol-based duty-cycling is to add an auxiliary receiver called wake-up receiver (WuRx) to each node. As shown in figure 1.3, during idle monitoring, the main transceiver is off and only WuRx is on. It continuously monitors the channel for incoming transmissions. When it detects a wake-up sequence, it will wake up the main receiver for data communication immediately. Figure 1.4 compares the performance of average power consumption and average network latency between protocol-based duty-cycling (CSL mechanism) and reactive wake-up receiver by using the power numbers from WuRx literature [Pletcher09] and Atmel AT86RF233 [Atmel14]. It assumes the control packets (ACK, Wake-up Frame) are 40 bits long and the data packet is 200 bits long, all with an 18bit preamble. The transceiver data rate is 50k bits per second and each device has 5 neighbors. It can be clearly seen from the figure that the use of a wake-up receiver breaks the trade-off between network latency and average power consumption. It can help to effectively reduce the average power consumption of each node while keeping the latency bounded. However, when traffic load (network activity) becomes low, the power consumption of WuRx starts to dominate the energy consumed by each node. Therefore, it is crucial to keep the power budget of WuRx at really low level.

Figure 1.4 Performance Comparison between Protocol Based Duty-Cycling and Reactive Wake-up Receiver

### 1.3 Dissertation Outline

This dissertation investigates the possibility of designing an ultra-low power, low latency receiver for low activity wireless links. It provides system level analysis methodology as well as circuit level design techniques for implementation of a practical wake-up receiver. It is organized in six chapters. After this introduction, Chapter 2 presents a high level overview of the design considerations and functional specifications for the wake-up receiver. It also proposes a two-step wake-up architecture including energy detection mode and addressing mode for the wake-up receiver and discusses its system level design metrics in details. Chapter 3 describes the design and implementation of energy detection mode. It proposes an effective technique to achieve high sensitivity with limited power budget. Following that, Chapter 4 details the design and implementation of addressing mode. Chapter 5 presents the measurement results. Finally, Chapter 6 concludes with a brief summary of this dissertation and discussion of future research directions. A bibliography is included in the appendix.

# **Chapter 2**

# **System Level Design**

# 2.1 Design Consideration

The specifications and implementation of the wake-up receiver rely heavily on the intended applications. In this research, our goal is to design a wake-up receiver for low activity wireless network and to build a prototype compatible with 802.15.4g [IEEE10].

### 2.1.1 System Integration

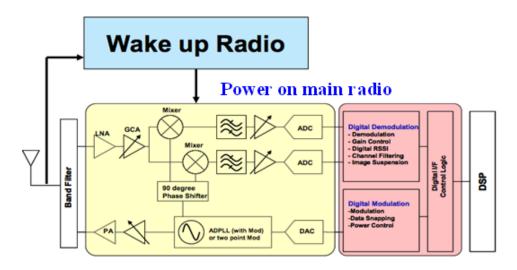

At the system level, the wake-up receiver must integrate conveniently with the main transceiver. The overall system architecture together with WuRx is shown in figure 2.1. The WuRx shares the same antenna with the main transceiver for minimum size and easy integration. To reduce hardware cost, it is desirable for the WuRx to receiver signals from the same transmitter used for data communications, such that no additional wake-up transmitter is required. Therefore, the implementation of WuRx will use the same carrier frequency, modulation scheme and data rate as the main transceiver. In 802.15.4g, it specifies nine different frequency bands for narrow band operation including 450 MHz, 470 MHz, 863 MHz, 896/901 MHz, 901/902 MHz, 915 MHz, 928/960 MHz, 1427/1518 MHz and 2450 MHz as well as ultra-wideband (UWB) operation; It also specifies three different modulation schemes including FSK, OFDM and QPSK and various data rate ranging from 10kbps up to 200kbps. In this research, we target to build a WuRX prototype for 915MHz ISM band with FSK modulation scheme and 50kbps data rate. When implementing the WuRx, compatibility with 802.15.4g at the MAC layer is not necessary. A dedicated wake-up command or sequence can be designed and used, as it only add one additional instruction set to DSP or one additional state to the state machine. Its power overhead is negligible.

Figure 2.1 System Integration with WuRx

#### 2.1.2 Active Power Oriented

For a general purpose low power transceiver design, the energy efficiency is usually the most important metric it targets for, as it is typically used in data driven applications where energy per transferred bit is more closely tied to the battery life of a wireless device. During its communication, protocol-based duty cycling is implemented. As previously mentioned, with extremely low duty cycling, high active power consumption can be tolerated as long as the data rate is high enough to result in an overall low energy per bit. However, a WuRx is essentially an event driven receiver that detects whether there is communication in the channel and asserts a signal to wake up the main data receiver. At the most basic level, it is just a one bit RF energy detector. Therefore, energy per bit is meaningless to WuRx and active power consumption is the most critical metric for WuRx design. Moreover the WuRx needs to listen to the channel continuously and cannot take advantage of duty-cycling. This means that transceiver architecture such as UWB is not suitable for WuRx since it depends on heavy duty-cycling and synchronization to achieve low energy per pit.

The active power consumption specification depends heavily on the application. Energy harvesters instead of battery become more attractive for recent applications, yet state-of-the-art energy harvesters, for example, sub-mm solar cells under moderate illumination can only provide up to  $100\mu W$  power [Ingram11] for a wireless device. From the previous simulation shown in figure 1.4, considering the overall wireless system has an activity rate as low as one packet per second, the power consumption of WuRx needs to be less than  $50\mu W$  so as to meet the total  $100\mu W$  power budget.

#### 2.1.3 Performance Metrics

Another important difference between a general purpose low power transceiver and a WuRx is the performance metrics. For a general purpose receiver, bit error rate (BER) performance is the most important as they are mainly used in data communications. However, BER is not a proper metric to measure the WuRx from its functional perspective. Instead, the performance metrics of interest are probability of miss detection and probability of false alarm. These two errors have strong relationship with the power dissipation. Miss detection means that the WuRx misses the current wake-up request and the transmitter must re-transmit the request which increases both the power and the system latency. False alarm means that the WuRx wakes up the main data receiver unnecessarily which also costs additional power consumption. Detailed analysis for the specification of miss detection rate and false alarm rate will be discussed in a later section.

### 2.1.4 Sensitivity

The sensitivity requirement is typically related to communication distance, transmitted power and antenna gain. As discussed previously, the WuRx and the main transceiver will share the same antenna and use the same transmitter. Besides, the WuRx should be able to communicate over the same distance as the main transceiver. Therefore, for WuRx design, it is desirable to achieve sensitivity comparable to that of the main data transceiver. Otherwise, it may either decrease the communication range which limits the applications or require an additional power amplifier at the transmitter side to increase the transmitted power which costs extra power consumption. In 802.15.4g protocol [IEEE10] it specifies the receiver sensitivity to be at least -90dBm, therefore in this research our target receiver sensitivity should be better than -90dBm.

From the above discussion, the overall WuRx specifications are summarized in table 2.1.

| Parameter                | Specification |

|--------------------------|---------------|

| Architecture             | Narrow Band   |

| Carrier Frequency        | 915MHz        |

| Modulation Scheme        | FSK           |

| Data Rate                | 50k           |

| Sensitivity              | -90dBm        |

| Active Power Consumption | < 50μW        |

**Table 2. 1 Specification of WuRx Prototype**

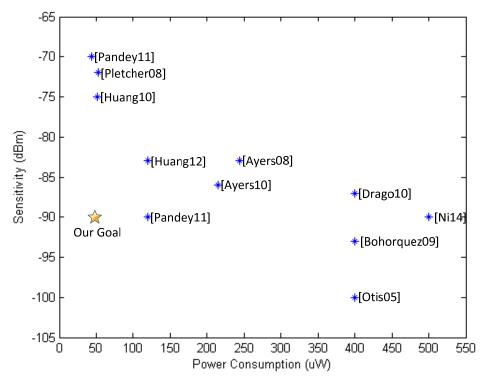

Figure 2.2 Performance of Recently Published Low Power Receivers

Figure 2.2 shows the performance comparison of previously published low power receivers. Although several implementations achieve high level of sensitivity, their power consumption is more than 2 to 10 times higher than the power budget for the WuRx. On the other hand, some implementations are able to consume within the power budget, yet their achievable sensitivity is more than 15dBm away from the sensitivity requirement for the WuRx. Obviously, the feasibility of implementing a high sensitivity receiver with less than  $50\mu W$  of power consumption represents the most critical challenge for the WuRx design.

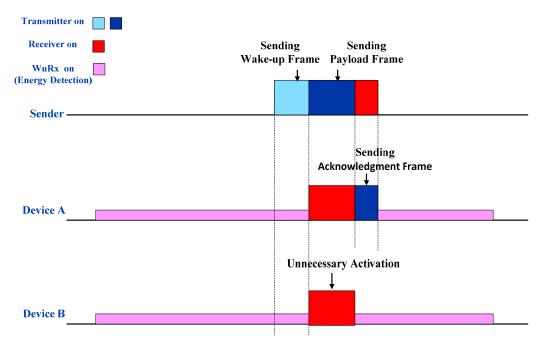

## 2.2 Proposed Two-Step WuRx

The most basic way to design a WuRx is to build a simple RF energy detector. However from reliability and power saving purpose, a more sophisticate practical implementation should be considered. Figure 2.3 shows an example wake-up scheme with only simple energy detection. In this example, the sender wants to communicate with device A. As A and B are neighboring devices, both WuRx A and WuRx B can detect energy from the wake-up frame transmitted by the sender and will wake up the data receiver of A and B simultaneously. This means that the data receiver B is unnecessarily activated which results in an additional energy waste. Therefore to avoid false alarms triggered by regular

Figure 2.3 Wake-up Scheme with Simple Energy Detection

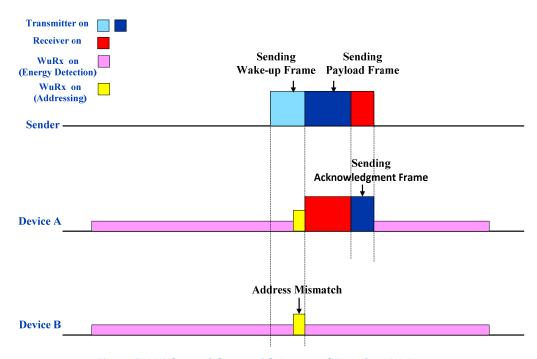

Figure 2.4 Wake-up Scheme with Proposed Two-Step WuRx

Figure 2.5 Wake-up Frame for Proposed Two-Step WuRx

data communication between neighboring devices, the WuRx design should contain the functionality of selective wake-up among different devices which means unique device ID/address detection should be included. Upon this principle, we propose a two-step WuRx architecture. The wake-up strategy and corresponding wake-up frame design is shown in figure 2.4 and figure 2.5. The WuRx has two operation modes: energy detection mode and address detection mode. Most of time, it is in energy detection mode monitoring whether there is communication energy in the channel. After it detects energy, it switches to address detection mode checking whether the address required in the wake-up frame matches the device address. If matches, it will wake up the main data receiver for data communication, otherwise it switches back to energy detection mode for channel monitoring. Obviously, due to the function complexity, the power dissipation in energy detection mode is smaller than in address detection mode. According to some previous literature, an RF energy detector dissipates tens of microwatts [Pletcher07], while an FSK demodulator dissipates hundreds of microwatts [Lont12]. Yet both of them consume much less power than the main data receiver whose typical power consumption is a few milliwatts. Therefore, by using the two-step wake up strategy, the unnecessary wake-up of main data receiver due to the communication initiated by neighboring devices has been avoided. Commands destination checking has been released from main data receiver to the WuRx which results in a huge amount of power saving. The average power consumption of the proposed WuRx is mainly dominated by the power dissipated in energy detection mode, yet it is also related to the power consumption of address detection mode and probabilities of error rates. Detailed analysis will be described in next section.

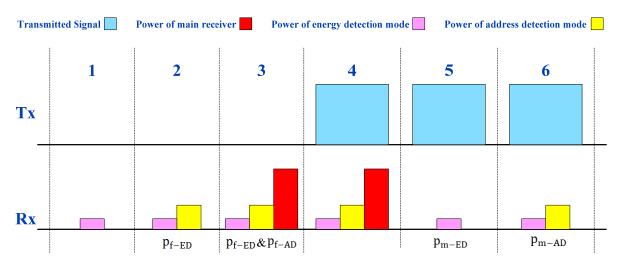

Figure 2.6 Six Different Working Categories for WuRx

### 2.3 Design Metrics

As mentioned in chapter 1, there are two major design metrics when comparing the WuRx aided wireless system with the traditional protocol-based duty-cycling system: average power consumption and average latency. These two metrics are not only related to the power consumption in different modes and the length of wake-up frame, but also related to the probabilities of errors. Before going through details of the design metrics, we first list the main notations that are used in the analysis.

- P<sub>ED</sub>: power consumption in energy detection mode

- p<sub>f-ED</sub>: probability of false alarm in energy detection mode

- p<sub>m-ED</sub>: probability of miss detection in energy detection mode

- T<sub>ED</sub>: total time in energy detection mode

- P<sub>AD</sub>: power consumption in address detection mode

- p<sub>f-AD</sub>: probability of false alarm in address detection mode

- $p_{m-AD}$ : probability of miss detection in address detection mode

- T<sub>AD</sub>: total time in address detection mode

- P<sub>MAIN</sub>: power consumption of main data receiver

- α : receiver wake-up activity rate.

- T<sub>W</sub>: total time of the wake-up frame

As shown in the figure 2.6, the working scheme of a WuRx can be divided into six categories. 1, 2, 3 refer to the scenario where no data communication exists in the channel. 1 is the normal operation. 2 stands for false alarm in energy detection mode which costs extra power for waking up address detection mode. 3 represents false alarm in both modes which triggers an unnecessary wake up of the main data receiver. 4, 5, 6 refer to the scenario where a wake-up frame is sent by the transmitter. 4 is the normal operation. 5 indicates miss detection in energy detection mode and the transmitter needs to resent the wake-up frame which costs additional latency. 6 means miss detection in address detection mode which results in not only additional latency but also additional power dissipation to operate in address detection mode once more. Combining all six of the above categories together, the average power consumption and the average latency of the WuRx can be derived as

$$\begin{aligned} \text{Power} &= P_{ED} + (1 - \alpha)(P_{AD} \cdot p_{f-ED} + P_{MAIN} \cdot p_{f-ED} \cdot p_{f-AD}) \\ &+ \alpha \cdot P_{AD}(1 + p_{m-AD} + p_{m-AD}^2 + p_{m-AD}^3 \dots \dots) \\ &= P_{ED} + (1 - \alpha)(P_{AD} \cdot p_{f-ED} + P_{MAIN} \cdot p_{f-ED} \cdot p_{f-AD}) + \frac{\alpha \cdot P_{AD}}{1 - p_{m-AD}} \end{aligned} \tag{2.1}$$

$$\text{Latency} &= T_W(1 - p_{m-ED})(1 - p_{m-AD}) \times \\ &\qquad (1 + 2p_{m-ED} + 2p_{m-AD} + 3(p_{m-ED}^2 + p_{m-ED} \cdot p_{m-ED} + p_{m-AD}^2) \\ &= \frac{T_W(1 - p_{m-ED} \cdot p_{m-AD})}{(1 - p_{m-ED})(1 - p_{m-AD})} \end{aligned} \tag{2.2}$$

From (2.1) and (2.2), one can figure out that both the average power consumption and the average latency are proportional to the probability of error rates. The higher the error rates, the larger the power dissipation and latency are. As the wake-up activity  $\alpha$  is low, the power consumption is mainly dominated by false alarm errors while the latency is determined by miss detection errors. Therefore, to satisfy the desired power budget and meanwhile to keep the latency bounded, it is important to set the specification of false alarm rate and miss detection rates in both operation modes.

In address detection mode, the WuRx performs as an ultra-low power FSK receiver. It should be able to correctly demodulate N bits in a wake-up frame used for address/ID matching. In this prototype, N is designed to be 50bits with 16bits of preamble for data synchronization purpose, 32 bits representing device unique address and 2 bits indicating the end of the wake-up frame. As the required FSK data rate ( $f_{data}$ ) is 50kbps, the total time spent on address detection mode is

$$T_{AD} = N \times \frac{1}{f_{data}} = 1 ms \tag{2.3}$$

Its probability of false alarm and miss detection are related to the number of bits (N) and its bit error rate (BER).

$$p_{f-AD} = BER_{AD}^{\ \ N} \tag{2.4}$$

$$p_{m-AD} = 1 - (1 - BER_{AD})^N \approx N \cdot BER_{AD}$$

(2.5)

Considering a typical BER requirement for wireless receiver as 10<sup>-3</sup>,

$$p_{f-AD} = (10^{-3})^{50} = 10^{-150}$$

(2.6)

$$p_{m-AD} \approx 50 \times 10^{-3} = 0.02 \tag{2.7}$$

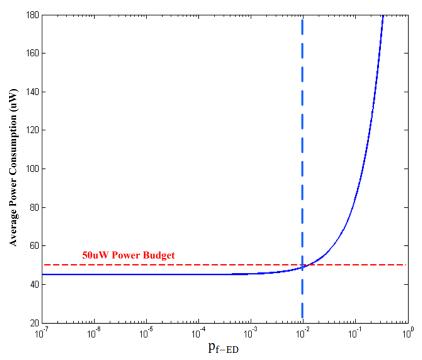

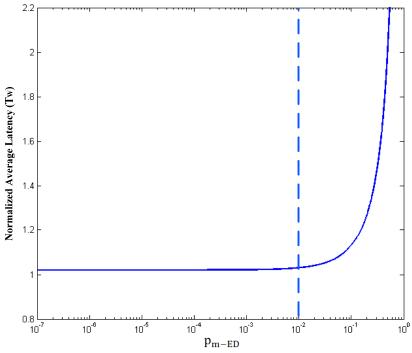

Obviously,  $p_{f-AD}$  is such a small number that it can be neglected. Therefore, the average power consumption of the WuRx heavily depends on the performance of energy detection mode, not only on its power dissipation but also on its probability of false alarm. Figure 2.7 and 2.8 plots the power and the latency performance based on probability of errors. We assume 45uW for energy detection mode, 400uW for address detection mode and 30mW for main receiver. It can be clearly seen from the graph that when  $p_{f-ED}$  becomes smaller, the average power consumption is dominated by the power dissipation in energy detection mode and would not be further reduced by decreasing  $p_{f-ED}$ . Therefore it is unnecessary to require a low  $p_{f-ED}$ . Rather  $10^{-2}$  roughly the corner probability of the graph is a reasonable requirement for our prototype design to satisfy 50µW power budget. Similarly,  $p_{m-ED}$  also targets for  $10^{-2}$ , which results in extra 4% average latency. For  $T_{ED}$  requirement, it is at least 1 bit long (20us) for energy detection as the transmitter can only send out data based on a fixed data rate. Yet analysis in chapter 3 will prove that T<sub>ED</sub> has a strong relationship with the achievable sensitivity. The longer the T<sub>ED</sub>, the higher the sensitivity that can be achieved. Therefore, considering a reasonable overhead to the whole wake –up frame,  $T_{ED}$  is designed to be 1/10 of  $T_{AD}$  which is about 5 bits length (100us).

Based on the previous discussion of design metrics, table 2.2 summarizes the specification of WuRx in different modes.

| Modes                         | Energy Detection Mode | Address Detection Mode |

|-------------------------------|-----------------------|------------------------|

| Power                         | < 45µW                | < 400µW                |

| Frame Length                  | < 5bits (100us)       | 50bits (1ms)           |

| Probability of False Alarm    | 10-2                  | 10-150                 |

| Probability of Miss Detection | 10-2                  | 0.02                   |

| BER                           | N/A                   | 10-3                   |

Table 2. 2 Specification of Proposed WuRx in Different Modes

Figure~2.7~Six~Different~Working~Categories~for~WuRx

Figure 2.8 Six Different Working Categories for WuRx

# 2.4 Summary

This chapter presents a system level design for the wake-up receiver. It has proposed a two-step wake-up architecture to avoid the unnecessary activation of main data receiver to achieve an ultra-low power budget. It also provides design metrics in terms of power and latency performance optimization. Based on that, wake-up receiver specifications have been discussed in details for both working modes which can be served as a guideline for circuit designs in later chapters.

# **Chapter 3**

# **Receiver for Energy Detection Mode**

# 3.1 Architecture Development

As described in Chapter 2, in energy detection mode, the main function of receiver is to perform a simple energy detection of the input RF signal. The major performance specification of the receiver remains to be ultra-low power consumption (45 $\mu$ W) and high sensitivity (-90dBm). There are a wide variety of ways to implement the energy detection receiver ranging from simple passive rectifier to complex super-heterodyne receiver. Before developing a suitable architecture, it is worth to make a performance comparison among different receiver architectures in terms of power consumption and sensitivity.

#### 3.1.1 Passive Rectifier

The passive rectifier is a typical circuit used in AC to DC conversion and is able to derive power from the incoming RF waveform. This performs exactly the desired functionality of the receiver in energy detection mode. Therefore, passive rectifier based receiver is the simplest and lowest power architecture. As shown in figure 3.1, the input RF signal passes through the frontend filter and the rectifier and is then compared with a given threshold to decide whether there is enough energy received in the channel. Since frontend filter and rectifier do not consume power and comparator operates at really low frequency, the power consumption of rectifier based receiver is extremely low, typically less than  $1\mu W$ . However due to the nature of rectifier, the sensitivity of this receiver is very poor. [Roberts12] reports a 98nW wake-up receiver with only -41dBm sensitivity. In [0h13], the authors add a 31-bit correlator after comparator for better interference rejection and sensitivity boosting. With 116nW power consumption, it is able to achieve -45dBm sensitivity. Although the active power consumption of the passive rectifier based receiver is well below our power budget, its achievable RF sensitivity is far away from the

Figure 3.1 Passive Rectifier Based Receiver

Figure 3.2 Tuned Radio Frequency (TRF) Receiver

desired specification. This architecture is not suitable to build the receiver for energy detection mode.

### 3.1.2 Tuned Radio Frequency (TRF) Receiver

The tuned radio frequency (TRF) receiver is another type of simple receiver which was invented and commonly used in the early nineteen century. As shown in figure 3.2, it is implemented with a frontend filter, RF amplification stages, a nonlinear envelop detector and baseband amplifiers. As implied by the name, the envelope detection process discards all frequency and phase content of the input signal and simply detects the amplitude of the RF carrier which implies the energy of the RF input. The TRF receiver is actually an enhanced version of the passive rectifier based receiver which is shown earlier to have poor sensitivity. It includes high frequency gain stages which are expensive from power perspective to improve the receiver sensitivity, thus it suffers from the tradeoff between power consumption and sensitivity performance. In [Pletcher08], the author proves that within a certain power budget, it is beneficial to increase gain in the front-end of a TRF receiver to achieve better sensitivity, even if the increase in gain results in degraded front-end noise performance. With this principle, the author builds a receiver with  $65\mu W$  power consumption, 75% of which is spent on RF amplification and achieves a sensitivity of

Figure 3. 3 Super-Regenerative Receiver

50dBm. Some following up researches have tried different techniques to improve the sensitivity without increasing the power consumption of RF amplification. [Huang10] has adopted double sampling technique applied to the down-converting envelope detector to suppress the offset and 1/f noise, although it means that the receiver is sensitive to the RF signal only half of the time. By flattening out the output noise floor, the receiver is able to achieve an improved sensitivity of -75dBm with 51 $\mu$ W power consumption, 58% of which is burnt on RF amplifiers. [Cheng12] implements a  $\Sigma\Delta$ ADC after the baseband amplifier. This first-order low-pass  $\Sigma\Delta$ ADC oversamples the wake-up request to enhance SNR and lessen the false detection, thus the receiver is able to achieve a sensitivity of -65dBm. Although all different techniques have been tried, yet limited sensitivity can be improved for a TRF receiver. The fundamental problem to use TRF architecture lies in providing sufficient gain at RF requires large amount of power. It limits the achievable sensitivity of a TRF receiver within a certain budget of power consumption.

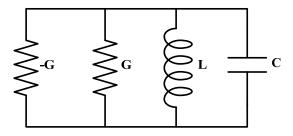

### 3.1.3 Super-Regenerative Receiver

One technique to enhance RF gain so as to improve sensitivity is the use of positive feedback, or regeneration, in the amplifier. This super-regenerative concept was first introduced by Armstrong in the 1920s and was used in the early days of wireless communication due to its ability to reach a high RF gain from active devices (vacuum electron tubes) and to operate at high RF frequencies above the  $f_T$  of RF devices [Whitehead50]. Figure 3.3 shows the typical architecture of a super-regenerative receiver. The frontend consists of a passive matching network, an isolation amplifier, a quenched oscillator, a RF envelop detector and a baseband demodulator. The oscillator is periodically turned on and off by a quenched signal. The start-up time of the oscillator is exponentially dependent upon the initial voltage of the oscillator tank and this dependency provides a large amount of gain achievable by a single stage. The resulting high RF gain in front of the envelope detector improves the receiver sensitivity substantially, to better than -99dBm

Figure 3.4 Single Conversion Superheterodyne Receiver

[Bohorquez09], [Otis05]. The super-regenerative receiver is fundamentally a TRF architecture using the quenched oscillator as a super-regenerative amplifier to achieve large RF gain and impressive performance. The drawback of this architecture is that a high accuracy local oscillator (LO) is now required. This stringent frequency accuracy typically requires a resonant LC oscillator, yet the limited quality factor (Q) of the integrated passive elements leads to a power floor of a few hundred microwatts. For example, in [Bohorquez09] the LC oscillator consumes  $315\mu$ W which is more than 78% of the total receiver power. Thus for super-regenerative architecture, the high power consumption of accurate LO generation makes it difficult to meet the power budget of the wake-up receiver.

### 3.1.4 Superheterodyne Receiver

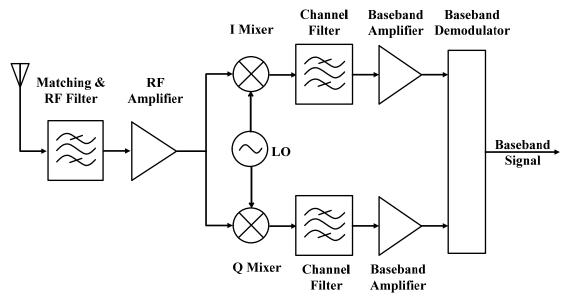

The superheterodyne receiver was first invented by Edwin Armstrong in 1918 during World War I. It is the most widely used architecture in nowadays wireless communication and almost all modern radio receivers use the superheterodyne principle. The basic idea of superheterodyne is to use frequency mixing to convert a received signal to an intermediate frequency (IF) which can be more conveniently processed than the original radio carrier frequency. At the cost of an extra frequency converter stage, the superheterodyne receiver provides superior selectivity and sensitivity compared with simpler designs described previously. Figure 3.4 shows an example of a single-conversion superheterodyne receiver design. The input RF signal passes through the matching network and is amplified by a low noise amplifier (LNA) so as to relax the noise requirement of the rest of the receiver chain. Then, the RF signal is down-converted to IF with a high-accuracy LO. The resulting IF signal is amplified and filtered to remove the image and interferers. Finally, the demodulator uses

Figure 3. 5 Wideband-IF Receiver

the IF signal to recreate a copy of the original data information. In the superheterodyne architecture, an RF LO with high frequency accuracy and spectral purity is required to drive the mixer. Similar to previous super-regenerative receiver, it almost invariably requires an LC oscillator embedded in a phase-locked loop and it is difficult to design a low power LC oscillator with on-chip low Q integrated components. Thus, the power consumption of this architecture is often limited by the power consumption of the LO.

Recently researchers have adopted different techniques to reduce the power consumption of LO generation. One technique is to apply duty-cycling either on LO blocks or on the whole receiver. For example, in [Drago10] the author duty-cycles the digital control oscillator (DCO) based PLL (DCPLL) at 10% (turned on 100ns every 1us) and the DCPLL still draws an average current of 180uA from a 1.2V supply. In [Milosiu13], the whole receiver is duty-cycled heavily to as low as 0.8% (turned-on  $4\times250ns$  every 125us). In this way, the power consumption of the receiver is brought down to  $217\mu W$  and can be reduced further with even more duty-cycling (e.g.  $27\mu W$  with 0.1% duty-cycling). Duty-cycling helps to reduce the power of a receiver, yet it either requires a novel design of fast settling oscillator/amplifier so as to decrease the minimum turned-on time or suffers from a tradeoff between detection rate and average power consumption.

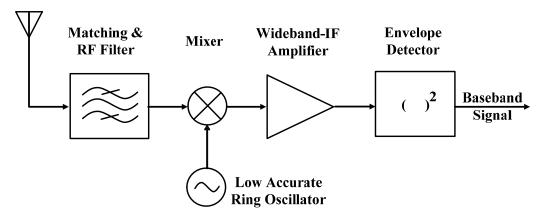

Another technique is to replace the LC oscillator with a CMOS ring oscillator whose power would be 20X smaller than its LC counterpart [Pletcher09]. The drawback of this replacement is that the frequency accuracy and phase noise of the ring oscillator is pretty poor, usually prohibit its use as the LO. Yet, in [Pletcher09], the author has overcome this fundamental disadvantage at the architectural level by proposing a superheterodyne receiver with wideband-IF as shown in figure 3.5. Due to the frequency inaccuracy of the ring oscillator, the RF input signal is converted down to a wideband IF instead of a fixed IF

and this wideband IF signal could be further converted to baseband by an envelope detector which is similarly used in a TRF receiver. Compared to a TRF receiver, this wideband-IF receiver utilizes a low quality ring oscillator to generate the LO so as to bring the gain amplification before the envelope detector from RF side to IF side which results in a major power saving. The proposed receiver is able to achieve a sensitivity of -72dBm with  $52\mu W$  power consumption.

## 3.1.5 Proposed Architecture

From previous architecture reviewing, the TRF receiver and the superheterodyne receiver with wideband-IF could be two potential choices for designing a receiver for energy detection mode. Both of them eliminate the power hungry and high precision timing element which make it possible to bring the total power of receiver down within our tight budget, yet the published achievable sensitivity of these two type receivers is still far away from our target, with the best performance around -75dBm [Huang10]. For a TRF receiver, the bottleneck of performance improvement remains in the tradeoff between achievable sensitivity and expensive power spent on the front-end RF gain stages. For example, in [Huang14] the TRF receiver is able to reach a sensitivity of -61dBm with 64uW power consumption and can be improved to -86.5dBm with extra 82µW spent on the RF amplification. For a wideband-IF receiver, the dominant noise contribution comes from the noise folding from wideband IF to baseband when performing envelope detection [Pletcher09]. As the bandwidth of IF is several orders larger than that of baseband, by envelope detection, this wideband IF noise will be superposed on top of the baseband signal which largely degrades the achievable SNR at the receiver output. Therefore, to improve the sensitivity performance of a wideband-IF receiver, one need to find an effective way to eliminate the contribution from wideband IF noise.

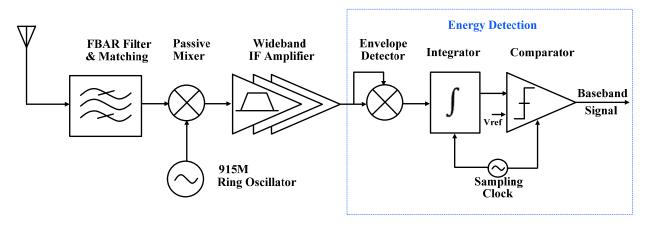

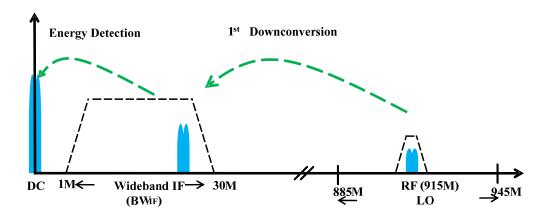

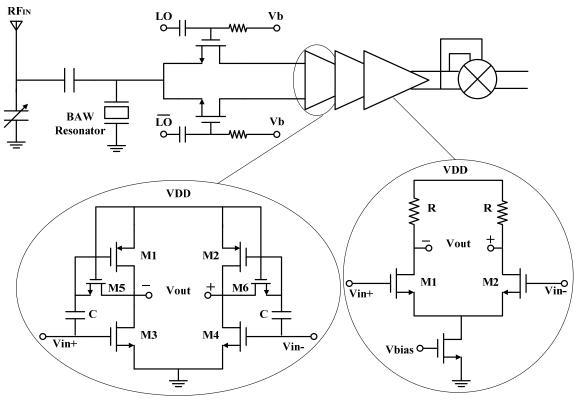

True circuit noise is a random process following Gaussian distribution and is still a random process following a certain distribution after a square operation. If a random process is averaged for sufficient time, it converges to its mean value which can be estimated depending on its distribution. Based on this principle, we propose a receiver architecture for energy detection mode based on "wideband-IF" and "noise averaging". Figure 3.6 shows the proposed receiver architecture and its frequency planning. The input RF signal first passes through a matching network which contains a FBAR resonator to simultaneously filter the input with a sharp band-pass response. With the MEMS resonator embedded, the frontend network provides a high selectivity and helps to eliminate interfering signals that lie close to the desired channel. Then the RF signal is down-converted to the wideband IF with a mixer and a low power ring oscillator which can be calibrated within 30MHz of the desired frequency. The resulting IF signal is amplified with gain blocks that cover the entire IF bandwidth (BW<sub>IF</sub>) and is further down-converted to baseband through energy detection

Figure 3.6 Proposed Receiver Architecture in Energy Detection Mode

Figure 3.7 Frequency Planning for Receiver in Energy Detection Mode

which consists of a self-driven mixer (envelope detector), an integrator and a comparator. As the integrator performs averaging functionality, it also helps to shape the wideband noise to its mean value which can be effectively eliminated by turning the threshold at the comparator. The proposed receiver architecture adopts the "wideband-IF" concept to utilize a low power ring oscillator instead of a LC oscillator for LO generation which results in huge power saving to satisfy the power budget. Meanwhile, it also adopts the "noise averaging" concept to eliminate the effect of wideband noise caused by "wideband-IF" so as to improve the sensitivity to the desired number. Detailed sensitivity analysis is provided in next section.

## 3.2 Sensitivity Analysis

Traditionally, the sensitivity of a receiver is calculated as:

$$Sens = -174dBm + 10logBW + NF + SNR_{MIN}$$

(3.1)

where SNR<sub>MIN</sub> is the minimum required signal to noise ratio for a certain detection. Typically, energy detection performed by using envelope detector needs around 11 dB SNR<sub>MIN</sub> for a decent error rate [Proakis01]. NF is the noise figure of the whole receiver which is typically proportional to the bias current and could not be easily reduced without increasing the power budget significantly. BW is the noise bandwidth in Hz, usually comparable to the bandwidth of baseband data. Yet, due to the nonlinear nature of the envelope detector, it is not straightforward to analyze the noise figure directly. Therefore we modify the sensitivity equation from (3.1) to

$$Sens = -174dBm + 10logBW_{IF} + NF_{FE} + SWNR_{MIN}$$

(3.2)

where  $BW_{IF}$  is the noise bandwidth of wideband IF.  $NF_{FE}$  is the linear noise figure of the receiver frontend including matching network, mixer and IF gain stages.  $SWNR_{MIN}$  is the minimum required signal to wideband noise ratio needed for energy detection to achieve a certain error rate. In this calculation, the noise generated by energy detection circuitry itself is neglected as the frontend gain stages can easily achieve  $60 \sim 70$  dB of gain. This makes the noise contribution of energy detection a trivial factor of the total noise performance [Gambini08]. In this section, we will build a theoretical model for energy detection so as to analyze  $SWNR_{MIN}$  it needs to achieve a certain error rate. Then we use this  $SWNR_{MIN}$  together with  $NF_{FE}$  and  $BW_{IF}$  to calculate the sensitivity of receiver.

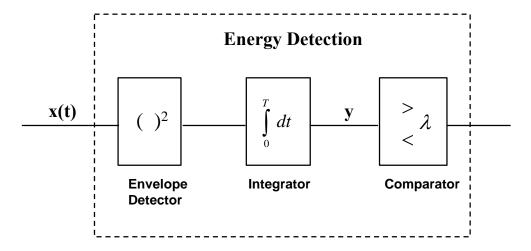

## 3.2.1 Theoretical Model for Energy Detection

Before calculate SWNR<sub>MIN</sub>, we first list the main notations that are used to describe the theoretical model for energy detection shown in Figure 3.8.

- x(t): input waveform of energy detection

- y: integrator output

- s(t): IF signal waveform

- n(t): noise waveform which is modeled as zero-mean, white Gaussian random process with variance  $\sigma_N^2$ .

- B: noise bandwidth which is equal to BW<sub>IF</sub>

Figure 3. 8 Theoretical Model for Energy Detection

- N<sub>0</sub>: noise power spectrum density

- SWNR: signal to wideband noise ratio at the input of energy detection

- T: integration time also the energy detection latency.

- λ: energy threshold used by comparator

- H<sub>0</sub>: hypothesis corresponding to no signal transmitted.

- H<sub>1</sub>: hypothesis corresponding to signal transmitted.

- Pf: probability of false alarm

- Pm: probability of miss detection

- Fn(x): cdf of normalized chi-squared distribution with n degree of freedom

- Fn,s(x): cdf of non-central chi-squared distribution with n degree of freedom and a non-central parameter of s.

The input signal of energy detection takes the form

$$x(t) = h \times s(t) + n(t) \tag{3.4}$$

where h = 0 or 1 under hypotheses  $H_0$  or  $H_1$  respectively. The output of the integrator  $y_0$  and  $y_1$  will act as the test statistic to test the two hypotheses  $H_0$  or  $H_1$  respectively.

Let us first start with hypotheses H<sub>0</sub> when there is no signal transmitted

$$x_0(t) = n(t) \tag{3.4}$$

$$y_0 = \int_0^T x_0^2(t)dt = \int_0^T n^2(t)dt$$

(3.5)

As the noise signal has bandwidth B, according to the sampling theorem [Shannon49], it can be expressed as

$$n(t) = \sum_{i=-\infty}^{\infty} a_i \operatorname{sinc}(2Bt - i)$$

(3.6)

where

$$\operatorname{sinc} = \frac{\sin(\pi x)}{\pi x}$$

,  $a_i = n\left(\frac{i}{2B}\right)$

Clearly, each  $a_i$  is the sample of zero-mean white Gaussian random process n(t), so it is a Gaussian random variable with zero mean and with the same variance  $\sigma_N^2$ , which is the variance of n(t).

$$\sigma_{\rm N}^2 = N_0 B \tag{3.7}$$

$$\mathbf{a}_{\mathbf{i}} \sim \mathsf{N}(\mathsf{0}, \mathsf{N}_{\mathbf{0}}\mathsf{B}) \tag{3.8}$$

$$\frac{a_i}{\sqrt{N_0 B}} \sim N(0,1) \tag{3.9}$$

Using the fact that

$$\int_{-\infty}^{\infty} \operatorname{sinc}(2Bt - i)\operatorname{sinc}(2Bt - j)dt = \begin{cases} \frac{1}{2B} & (i = j) \\ 0 & (i \neq j) \end{cases}$$

(3.10)

We may write

$$\int_{-\infty}^{\infty} n^2(t)dt = \frac{1}{2B} \sum_{i=-\infty}^{\infty} a_i^2$$

(3.11)

[Urkowitz67] has proved that if 1/T is small enough compared to B, on the interval (0, T), signal can be approximated by a finite sum of 2BT. This assumption is exactly true for our energy detection, since the noise bandwidth B is much larger than the desired data bandwidth 1/T. It also means the integration time T needs to be long enough to make the assumption work. Therefore

$$y_0 = \int_0^T n^2(t)dt = \frac{1}{2B} \sum_{i=0}^{2BT} a_i^2$$

(3.12)

According to (3.9) and (3.12), the test statistic  $y_0$  can be rewritten as

$$\frac{2y_0}{N_0} = \sum_{i=1}^{2BT} \left(\frac{a_i}{\sqrt{N_0 B}}\right)^2 \tag{3.13}$$

$\frac{2y_0}{N_0}$  is a sum of the squares of 2BT Gaussian variables with zero mean and unit variance, thus following central chi-squared distribution with 2BT degree of freedom.

Next, let us focus on with hypotheses  $H_1$  when there is signal present.

$$x_1(t) = s(t) + n(t)$$

(3.14)

$$y_1 = \int_0^T x_1^2(t)dt = \int_0^T (s(t) + n(t))^2 dt$$

(3.15)

As signal bandwidth is much smaller than noise bandwidth, according to the sampling theorem [Shannon49], the signal can be expressed as

$$s(t) = \sum_{i=-\infty}^{\infty} b_i \operatorname{sinc}(2Bt - i)$$

(3.16)

$$x_1(t) = \sum_{i=-\infty}^{\infty} (a_i + b_i) \operatorname{sinc}(2Bt - i)$$

(3.17)

where

$$\operatorname{sinc} = \frac{\sin(\pi x)}{\pi x}, b_i = s\left(\frac{i}{2B}\right)$$

By using the fact (3.10)

$$\int_{-\infty}^{\infty} s^{2}(t)dt = \frac{1}{2B} \sum_{i=-\infty}^{\infty} b_{i}^{2}$$

(3.18)

$$\int_{-\infty}^{\infty} x_1^2(t)dt = \frac{1}{2B} \sum_{i=-\infty}^{\infty} (a_i + b_i)^2$$

(3.19)

Similarly, on the interval (0, T), signal can be approximated by a finite sum of 2BT.

$$\int_{0}^{T} s^{2}(t)dt = \frac{1}{2B} \sum_{i=0}^{2BT} b_{i}^{2}$$

(3.20)

$$y_1 = \int_0^T x_1^2(t)dt = \frac{1}{2B} \sum_{i=0}^{2BT} (a_i + b_i)^2$$

(3.21)

According to (3.9), (3.20) and (3.21), the test statistic  $y_1$  can be rewritten as

$$\frac{2y_1}{N_0} = \sum_{i=1}^{2BT} \left(\frac{a_i + b_i}{\sqrt{N_0 B}}\right)^2$$

(3.22)

$$\sum_{i=i}^{2BT} \left( \frac{b_i}{\sqrt{N_0 B}} \right)^2 = \frac{2BT \cdot \frac{1}{T} \int_0^T s^2(t) dt}{N_0 B} = 2BT \cdot SWNR$$

(3.23)

Similar to  $\frac{2y_0}{N_0}$ ,  $\frac{2y_1}{N_0}$  follows non-central chi-squared distribution with 2BT degree of freedom and a non-central parameter of 2BT · SWNR.

The probability of miss detection (P<sub>m</sub>) and false alarm (P<sub>f</sub>) can be generated by

$$P_{m} = P(y < \lambda | H_{1}) = P\left(\frac{2y_{1}}{N_{0}} < \frac{2\lambda}{N_{0}}\right)$$

(3.24)

$$P_f = P(y > \lambda | H_0) = P\left(\frac{2y_0}{N_0} > \frac{2\lambda}{N_0}\right)$$

(3.25)

where  $\lambda$  is the decision threshold and it is reasonable to assume that  $\lambda$  is proportional to noise power BN $_0$  and integration time T

$$\lambda = \beta \cdot BN_0 \cdot T \tag{3.26}$$

where  $\beta$  is the normalized factor. Using (3.13), (3.22) and (3.26) to evaluate (3.24) and (3.25) yields

$$P_{\rm m} = F_{\rm 2BT,2BT \cdot SWNR}(2BT \cdot \beta) \tag{3.27}$$

$$P_f = 1 - F_{2BT}(2BT \cdot \beta) \tag{3.28}$$

From the above analysis, we can figure out that the probability of miss detection  $(P_m)$  of the proposed energy detection is related to the cumulative distribution function (cdf) of noncentral chi-squared distribution while the probability of false alarm  $(P_f)$  is related to the cdf of chi-squared distribution. They are determined by four parameters: 1) Decision threshold  $(\beta)$  2) Noise bandwidth (B) 3) Integration time (T) 4) Signal to wideband noise ratio (SWNR). Noise bandwidth, integration time and decision threshold together determine the amount of noise reduction that can be achieved by "noise averaging" and the effect of each parameter will be explored further in the next section.

#### 3.2.2 Simulation Result

Simulations based on (3.27) and (3.28) are done in matlab to verify the performance of the proposed energy detection. Effects of different design parameters - decision threshold  $\beta$ , noise bandwidth B and integration time T will be discussed respectively and an estimation of receiver sensitivity will also be provided.

#### **Decision Threshold**

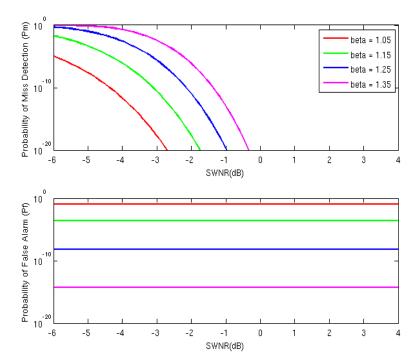

Figure 3.9 plots the probability of detection errors ( $P_m$  and  $P_f$ ) versus SWNR with fixed noise bandwidth, fixed integration time and various decision threshold. It can be clearly viewed from the figure that  $P_f$  is always flat with different SWNR as it is only related to hypothesis  $H_0$  when there is no signal presented while  $P_m$  is effected by SWNR and could be improved with an increasing of SWNR. It is also obvious that when decision threshold is low, one can get better miss detection rate. On the contrast, when the decision threshold is high, one can achieve better false alarm rate. To take both  $P_m$  and  $P_f$  into account, we define energy detection error rate (DER) as

$$DER = \alpha \cdot P_m + (1 - \alpha) \cdot P_f \tag{3.29}$$

Figure 3.9 Probability of Miss Detection ( $P_m$ ) and Probability of False Alarm ( $P_f$ ) Vs SWNR for Various Threshold Factor  $\beta$  with 30MHz Noise Bandwidth and 10us Integration Time.

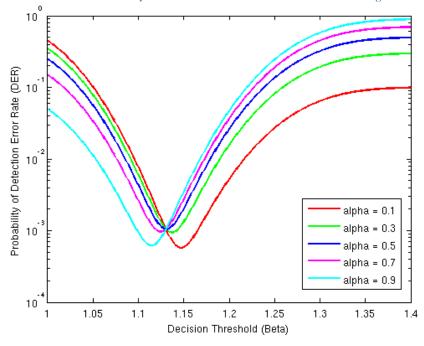

Figure 3.10 Detection Error Rate (DER) Vs Decision Threshold Factor  $\beta$  for Various Wake-up Activity Rate  $\alpha$  with 30MHz noise bandwidth, 10us integration time and -5.5dB SWNR

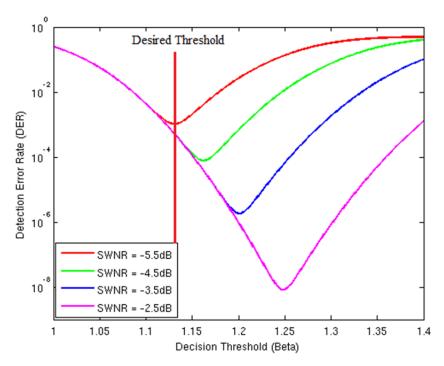

Figure 3.11 Detection Error Rate Vs Decision Threshold Factor  $\beta$  for Various SWNR with 30MHz noise bandwidth and 10us integration time

where  $\alpha$  is receiver wake-up activity rate. As by varying decision threshold  $\beta$ ,  $P_m$  and  $P_f$  are varied accordingly, the most effective way to achieve minimum DER is to set  $\beta$  at the point where  $\alpha \cdot P_m$  and  $(1-\alpha) \cdot P_f$  equal to each other. Figure 3.10 plots detection error rate versus decision threshold with various wake-up activity rate, fixed noise bandwidth, fixed integration time and fixed SWNR. It shows that with different  $\alpha$  one can always achieve an optimum DER by changing  $\beta$  and the worst optimum DER occurs at the point when  $\alpha$  equals 0.5. Therefore in later simulations we only consider the worst case scenario when  $\alpha$  equals 0.5. One thing to notice is that when  $\alpha$  equals 0.5, DER has the same definition as bit error rate (BER) for OOK demodulation. Thus our energy detector could also be used as OOK demodulator for an ultra-low power receiver.

Figure 3.11 plots the detection error rate versus decision threshold for different SWNR with fixed noise bandwidth and fixed integration time. Obviously, for each SWNR, there always exists a different optimum  $\beta$  to achieve the minimum DER and when SWNR is increased, the optimum  $\beta$  shifts to a larger value which helps to reduce the probability of false alarm and yields a lower DER. In our design, for a desired setting of noise bandwidth and integration time, we only choose a fixed  $\beta$  located at the optimum point (as shown in the red straight line) where with SWNR<sub>MIN</sub>, it can achieve a DER less than  $10^{-3}$ . Thus for any SWNR larger than SWNR<sub>MIN</sub>, a better DER can always be guaranteed.

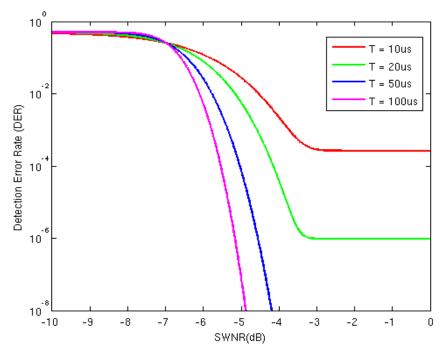

Figure 3.12 Detection Error Rate Vs SWNR for Various Integration Time with Fixed Decision Threshold Factor  $\beta=1.2$  and 30MHz noise bandwidth

Figure 3.13 Minimum Required SWNR Vs Noise Bandwidth for 0.1% DER with 20us Integration Time and Optimum Decision Threshold

#### **Integration Time**

Figure 3.12 plots the detection error rate versus SWNR for different integration time with a fixed decision threshold. It demonstrates the effect of integration time that the system performance can always be improved by increasing the time of integration, yet this also leads to an increase in wake-up latency. For example, the minimum required SWNR for  $10^{-3}$  DER can be reduced by more than 2dB when increasing integration time from 10us to 100us. This presents a tradeoff between achievable sensitivity and system latency. Another noticeable thing is that when SWNR increases to a certain level, DER saturates and could no longer be improved. This is because the decision threshold is fixed and the probability of false alarm starts to dominate DER with higher SWNR.

#### Noise Bandwidth

From the definition of  $P_m$  (3.27) and  $P_f$  (3.28), we can figure out that the noise bandwidth has the same effect as the integration time. This means that the larger the noise bandwidth, the lower the required SWNR<sub>MIN</sub> to achieve a certain DER as shown in figure 3.13. Yet this does not imply that by increasing the noise bandwidth a better sensitivity can be achieve as the sensitivity needs to take noise power into account. When the noise bandwidth is increased, although SWNR<sub>MIN</sub> is reduced, the noise power is increased much faster which leads to an even worse performance. Figure 3.13 actually demonstrates the effectiveness of wideband noise reduction by performing "noise averaging". For example, for 30MHz noise bandwidth, with 20us integration time, it only requires a SWNR of -4dB to achieve 0.1% DER. Compared with theoretical 11dB SNR for non-coherent energy detection [Proakis01], our proposed strategy helps to remove more than 15dB excess noise power, thus it improves the sensitivity performance substantially. However when noise bandwidth decreases, "noise averaging" becomes less effective in noise reduction because more portion of noise is correlated with desired signal and could not be removed by average function. Especially, when noise bandwidth is close to data bandwidth (1/T), SWNR<sub>MIN</sub> reaches its theoretical value and "noise averaging" is no longer useful.

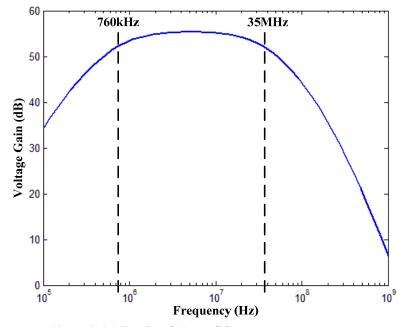

#### Receiver Sensitivity

Combining (3.2), (3.27), (3.28) and previously discussed design parameter together, figure 3.14 shows the simulation result for receiver sensitivity versus noise bandwidth with an estimated 13dB frontend noise figure. Considering IF bandwidth of 30 MHz to provide an adequate level of precision for a low power ring oscillator, the receiver could achieve better than -91.2dBm sensitivity with 20us integration time (one bit period) and sensitivity could be improved to around -96dBm with 180us integration time (nine bits period). One could also reduce the noise bandwidth to get better performance, yet this requires a more precisely controlled ring oscillator that may lead to a high power budget. This result

Figure 3.14 Receiver Sensitivity@ 0.1% DER Vs Noise Bandwidth for Various Integration Time

presents a tradeoff among achievable receiver sensitivity, latency (integration time) and power consumption.

# 3.2.3 Performance Boundary

It has been observed that by either increasing integration time T or decreasing noise bandwidth B, the sensitivity of the proposed energy detection receiver can be improved. In this section, we will prove this observation theoretically and quantify the performance improvement in terms of various design parameters.

Firstly, recall the definition of false alarm rate from (3.28),  $P_f$  is related to chi-squared distribution with n degree of freedom ( $\chi_n^2$ ) where n = 2BT. Let us define random variables  $Y_i$  which follows chi-squared distribution with one degree of freedom ( $\chi_1^2$ )

$$Y_i \sim \chi_1^2 \quad (i = 1, 2, \dots, n)$$

(3.30)

$$\sum_{i=1}^{n} Y_i \sim \chi_n^2 \tag{3.31}$$

According to the central limit theorems [Billingsley95]

$$\sum_{i=1}^{n} Y_{i} \stackrel{d}{\rightarrow} N(n \cdot E(Y_{i}), n \cdot Var(Y_{i})) \quad (n \rightarrow \infty)$$

(3.32)

where  $N(\mu, \sigma^2)$  represents normal distribution,  $E(Y_i)$  and  $Var(Y_i)$  represent mean and variance of random variable Yi respectively. Using the fact that

$$E(\chi_1^2) = 1$$

,  $Var(\chi_1^2) = 2$  (3.33)

**Yields**

$$\chi_n^2 \stackrel{d}{\to} N(n, 2n) \quad (n \to \infty)$$

(3.34)

Therefore

$$P_{f} = 1 - F_{2BT}(2BT \cdot \beta) = Q\left(\frac{n \cdot \beta - n}{\sqrt{2n}}\right) \qquad (n \to \infty)$$

(3.35)

where  $Q(\cdot)$  is the Q function of standard normal distribution.

Next, recall the definition of miss detection rate from (3.27),  $P_m$  is related to non-central chi-squared distribution with n degree of freedom and a non-central parameter of s ( $\chi^2_{n,s}$ ) where n = 2BT, s = 2BT·SWNR, similar to previous discussion

$$\chi_n^2 \stackrel{d}{\rightarrow} N(n+s, 2(n+2s)) \quad (n \rightarrow \infty)$$

(3.36)

Therefore

$$P_{m} = F_{2BT,2BT\cdot SWNR}(2BT \cdot \beta) = Q\left(\frac{n(1 + SWNR - \beta)}{\sqrt{2n(1 + 2 \cdot SWNR)}}\right) \qquad (n \to \infty)$$

(3.37)

Consider both of P<sub>m</sub> and P<sub>f</sub> smaller than 10<sup>-3</sup> and use the fact that

$$Q(3.1) < 10^{-3} \tag{3.38}$$

**Yields**

$$\frac{\mathbf{n} \cdot \mathbf{\beta} - \mathbf{n}}{\sqrt{2\mathbf{n}}} > 3.1 \tag{3.39}$$

$$\frac{n(1 + SWNR - \beta)}{\sqrt{2n(1 + 2 \cdot SWNR)}} > 3.1 \tag{3.40}$$

Combining (3.39) and (3.40) together to cancel  $\beta$

SWNR >

$$\frac{6.2\sqrt{2n} + 4 \cdot (3.1)^2}{n} \approx \frac{6.2\sqrt{2}}{\sqrt{n}}$$

$(n = 2BT \to \infty)$  (3.41)

Using sensitivity equation (3.2) and minimum SWNR (3.41)

$$Sens = -166dBm + NF_{FE} + 5\log(B) - 5\log(T)$$

(3.42)

(3.42) illustrates the relation among receiver sensitivity, frontend noise figure, noise bandwidth and integration time. With 13dB NF<sub>FE</sub>, 30MHz noise bandwidth and 20us integration time, the receiver is estimated to achieve a sensitivity of -92dBm which is pretty close to the simulation results. The sensitivity can be further improved by 5dB when increasing integration time or decreasing noise bandwidth by 10 times and this leads to a tradeoff among achievable sensitivity, system latency and power consumption.

## 3.3 Circuit Design

This section presents the detailed design of receiver circuitry shown in figure 3.6. For power considerations, the entire receiver is optimized for sub-threshold operation from a single 0.5V supply.

## 3.3.1 Input Matching Network