# Electronic-Photonic Co-Design of Silicon Photonic Interconnects

Sen Lin Vladimir Stojanovic, Ed.

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2017-208 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-208.html

December 13, 2017

Copyright © 2017, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Electronic-Photonic Co-Design of Silicon Photonic Interconnects

by

#### Sen Lin

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

${\bf Engineering-Electrical\ Engineering\ and\ Computer\ Sciences}$

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanović, Chair Professor Ming C. Wu Professor Xiang Zhang

Fall 2017

#### Abstract

Electronic-Photonic Co-Design of Silicon Photonic Interconnects

by

Sen Lin

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vladimir Stojanović, Chair

Silicon photonic interconnects hold great promise in meeting the high bandwidth and lowenergy demands of next-generation interconnects. System-level driven electronic-photonic co-design is the key to improving the bandwidth density and energy efficiency. In this study, a comprehensive co-optimization framework is developed for high-speed silicon photonic transmitters utilizing compact models and a detailed optical simulation framework. Given technology and link constraints, microring and Mach-Zehnder transmitter designs are optimized and compared based on a unified optical phase shifter model. Non-return-tozero (NRZ) and pulse-amplitude-modulation-4 (PAM-4) modulation schemes are analyzed and compared for microring-based transmitters. Using the co-design approach, a monolithic 40Gb/s optical NRZ transmitter based on microring modulators is designed and demonstrated in zero-change 45nm CMOS SOI process. Electronic-photonic co-design with the high swing driver enables this transmitter to achieve total energy efficiency of 330fJ/b and the photonics and modulator driver area bandwidth density of 6.7 Tb/s/mm<sup>2</sup>. This dissertation also discusses the design and demonstration of the first full silicon photonic interconnect on a 3D integrated electronic-photonic platform. These results make the microring-based silicon photonic transceivers an attractive solution for the next-generation inter and intra-rack photonic interconnects. Finally, a short-reach laser-forwarding coherent link architecture is proposed to further improve the energy efficiency of silicon photonic interconnects. The key concepts of the proposed architecture are verified experimentally with microring-based silicon photonic transmitters. The architecture saves the laser power by 6-7.5x and could enable complex modulation schemes for the future short-reach optical links.

# Contents

| 1        | Intr | roduction                                                         | 1              |

|----------|------|-------------------------------------------------------------------|----------------|

| <b>2</b> | Bac  | kground                                                           | 3              |

|          | 2.1  | Silicon Photonic Interconnects                                    | 3              |

|          |      | 2.1.1 Silicon photonic modulator and photodetector                | 3              |

|          |      | 2.1.2 WDM link architectures                                      | 4              |

|          |      | 2.1.3 Coherent optical links                                      | 5              |

|          | 2.2  | Silicon Photonics Platforms                                       | 6              |

|          |      | 2.2.1 Monolithic silicon photonics platform                       | 6              |

|          |      | 2.2.2 3D integrated silicon photonics platform                    | 7              |

|          | 2.3  | Challenges and Opportunities                                      | 8              |

|          |      | 2.3.1 Co-optimizing photonics and electronics                     | 8              |

|          |      | 2.3.2 Pushing speed limits of photonics transmitters              | 9              |

|          |      | 2.3.3 Reducing the high power consumption of laser sources        | 9              |

|          |      | 2.010 Iteadating the man power companies of labor sources 1.1.1.1 |                |

| 3        | Elec | ctronic-photonic Co-Optimization of Silicon Transmitter           | 11             |

| •        | 3.1  |                                                                   | 11             |

|          | 3.2  |                                                                   | 12             |

|          | J    | 3.2.1 Compact model of optical phase shifter                      | 12             |

|          |      |                                                                   | 16             |

|          | 3.3  | Optimization of Microring-based Transmitter                       | 18             |

|          | 0.0  |                                                                   | 18             |

|          |      |                                                                   | 20             |

|          |      |                                                                   | $\frac{1}{23}$ |

|          |      | 3.3.4 Microring-based NRZ transmitter design                      | 26             |

|          |      | 3.3.5 Microring-based PAM4 transmitter design                     | 28             |

|          | 3.4  | Optimization of Mach-Zehnder Transmitter                          | 32             |

|          | 0.1  |                                                                   | 32             |

|          |      |                                                                   | 34             |

|          |      |                                                                   | 36             |

|          | 3.5  |                                                                   | 38             |

|          | 3.6  |                                                                   | 40             |

|          | 0.0  |                                                                   | 10             |

| 4        | Hig  | h-speed Monolithic Silicon Photonics Transmitters                 | 41             |

| _        | 4.1  |                                                                   | 41             |

|          | 4.2  |                                                                   | 41             |

|          | 4.3  | Design of High-speed Transmitter Circuits                         | 44             |

|          | 1.0  | 4.3.1 NRZ transmitter with AC-coupled driver                      | 44             |

|          |      |                                                                   | 45             |

|          |      |                                                                   | 45             |

|   |     | 4.3.4 Digital PLL                                                    | 47 |

|---|-----|----------------------------------------------------------------------|----|

|   |     | 4.3.5 Overview of the test chip                                      | 48 |

|   | 4.4 | Measurement Results                                                  | 4  |

|   |     | 4.4.1 NRZ transmitter performance                                    | 4  |

|   |     | 4.4.2 PAM4 transmitter performance                                   | 5  |

|   |     | 4.4.3 Comparison to prior works                                      | 5  |

|   | 4.5 | Summary                                                              | 5  |

| 5 | 3D  | Integrated Silicon Photonic Interconnects                            | 5  |

|   | 5.1 | 3D Integration of CMOS and Photonics                                 | 5  |

|   | 5.2 | Circuits and System Implementation                                   | 5  |

|   |     | 5.2.1 Chip architecture                                              | 5  |

|   |     | 5.2.2 Transmitter design                                             | 5  |

|   |     | 5.2.3 Receiver design                                                | 6  |

|   |     | 5.2.4 Thermal Tuner Design                                           | 6  |

|   | 5.3 | Link Measurement Results                                             | 6  |

|   |     | 5.3.1 Link implementation                                            | 6  |

|   |     | 5.3.2 Analysis and comparison                                        | 6  |

|   | 5.4 | Summary                                                              | 6  |

| 6 | Col | nerent Silicon Photonic Links                                        | 6  |

|   | 6.1 | Introduction                                                         | 6  |

|   | 6.2 | Laser-forwarding Coherent Link Architecture                          | 7  |

|   | 6.3 | Modeling of Laser-forwarding Architecture                            | 7  |

|   |     | 6.3.1 Link performance analysis                                      | 7  |

|   |     | 6.3.2 Laser phase noise limitations                                  | 7  |

|   |     | 6.3.3 Microring modulator for the laser-forwarding BPSK architecture | 7  |

|   | 6.4 | Demonstration of Silicon Photonics Coherent Link                     | 8  |

|   |     | 6.4.1 Microring-based laser-forwarding BPSK                          | 8  |

|   |     | 6.4.2 Impact of the random phase drift on coherent detection         | 9  |

|   |     | 6.4.3 Microring-based laser-forwarding QPSK                          | 9  |

|   | 6.5 | Summary                                                              | 9  |

|   | J.J |                                                                      | Ü  |

| 7 | Fin | al Thoughts and Conclusions                                          | 9  |

# List of Figures

| 2.1<br>2.2<br>2.3 | A single channel silicon photonic interconnect based on microrings. [1] System diagram of a microring-based WDM optical link. [1]                                                                                                                                                                                                 | 4<br>5      |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.4<br>2.5        | CMOS process. [1]                                                                                                                                                                                                                                                                                                                 | 6<br>7<br>8 |

| 3.1               | The flowchart of the co-optimization framework for silicon photonics transmitters. The denotations here are used in derivations in the study                                                                                                                                                                                      | 13          |

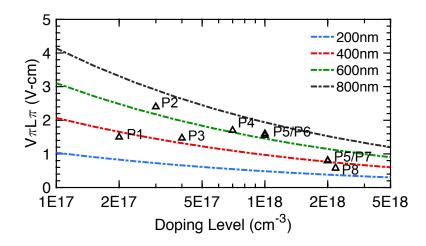

| 3.2               | Mach-Zehnder and microring modulators based on different PN junction phase shifters. Three common types of phase shifters are listed with top view or cross-section view. The corresponding feature lengths $(L_j)$ for these PN junc-                                                                                            |             |

| 3.3               | tions are listed as well                                                                                                                                                                                                                                                                                                          | 14          |

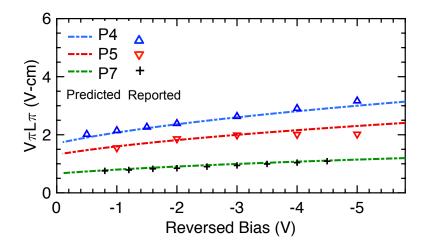

| 3.4               | marked here. Average concentration of n-type and p-type doping is used Modulation efficiency $V\pi L\pi$ vs. reversed bias voltage for phase shifters on three different platforms P4, P5, P7. Detailed information are included in                                                                                               | 16          |

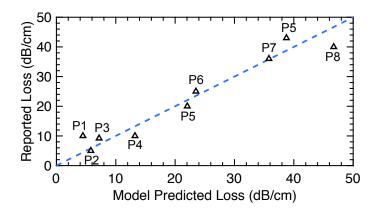

| 3.5               | Table 1. Note that [5] refers to the interleaved phase shifter on that platform. Reported waveguide loss vs. predicted waveguide loss. The references for each                                                                                                                                                                    | 17          |

| 3.6               | date points are labeled in the figure P1-P8                                                                                                                                                                                                                                                                                       | 17          |

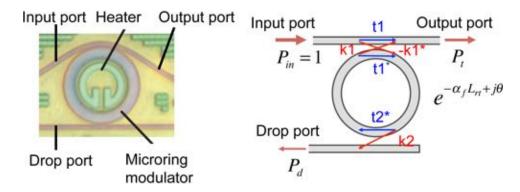

|                   | Model diagram of a microring modulator with drop port, where coupler and propagation coefficients for electric fields are labeled                                                                                                                                                                                                 | 19          |

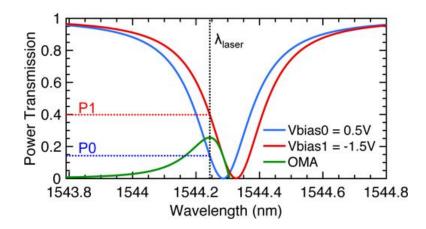

| 3.7               | Modeled power transmission spectra of microring modulator under two different bias voltages. Optimal laser wavelength to maximize OMA is labeled. For phase shifter model, we assumed that $N_A = N_D = 10^{18}$ cm <sup>-3</sup> , $L_j = 500$ nm and $\gamma = 0.75$ . The Q factor of this microring modulator is 7700. FSR of | 19          |

| 3.8               | this microring is around 20nm                                                                                                                                                                                                                                                                                                     | 20          |

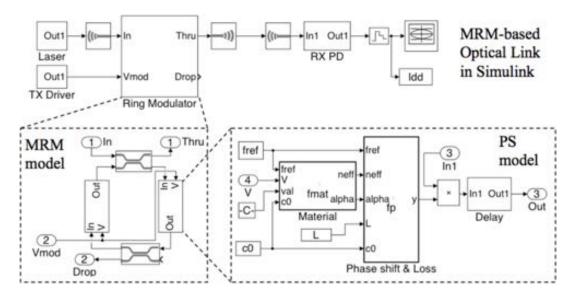

|                   | croring modulator (MRM) block and the phase shifter (PS) block                                                                                                                                                                                                                                                                    | 22          |

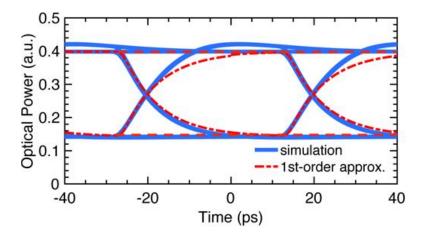

| 3.9               | Simulated eye diagram at 25 Gb/s. Device parameters are the same as the microring in Fig. 3.7 with optical bandwidth of around 25GHz. Laser detuning is set to optimize OMA. A first-order low-pass filter approximation with                                                                                                     |             |

|                   | 3dB bandwidth of 20GHz is represented with red dashed line                                                                                                                                                                                                                                                                        | 22          |

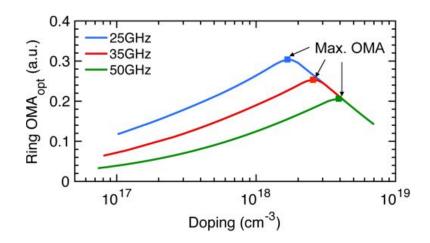

| 3.10 | Optimized OMA for $f_{optical}$ 25GHz, 35GHz and 50GHz versus doping levels in the PN junction. Bias conditions are $V_0 = 0.5 \ V$ and $V_1 = -1.5 \ V$ . |                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|      | Technology constraints: PN junction feature length $L_j = 500$ nm and optical                                                                              |                 |

|      | mode confinement factor $\gamma = 0.75$ . $L_{rt} = 30 \ \mu m$ , intrinsic loss 13 dB/cm [3].                                                             | 0.4             |

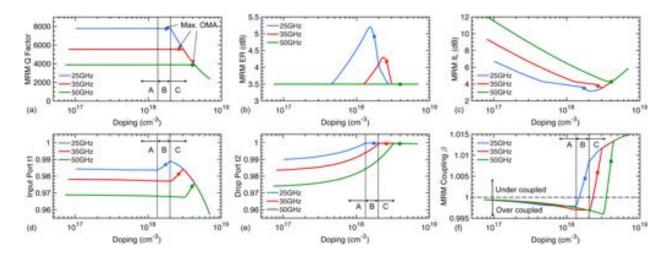

| 3.11 | Symmetric pn-junctions are assumed for simplicity                                                                                                          | 24              |

| 0.11 | els with the design points corresponding to maximum OMAs labeled. The                                                                                      |                 |

|      | optimization constraints corresponds to the curves in the Fig. 3.10. Three                                                                                 |                 |

|      | operation regions (A-C) are labeled for 25GHz operation as an example. A is                                                                                |                 |

|      | coupling-limited region, C is loss-limited region and B is the optimal region.                                                                             |                 |

|      | Note that $t_1$ and $t_2$ are transmission coefficients at the couplers. Stronger                                                                          |                 |

| 0.10 | coupling means smaller $t_1$ and $t_2$                                                                                                                     | 25              |

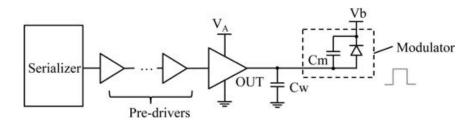

| 3.12 | Transmitter circuits for ring modulator. $C_w$ is the wire and packaging parasitic capacitance, and $C_m$ is the modulator junction capacitance            | 26              |

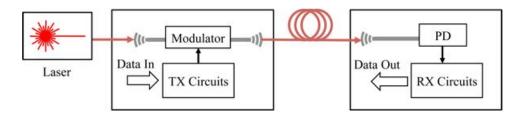

| 3.13 | Diagram of a full optical link with external laser source                                                                                                  | $\frac{20}{27}$ |

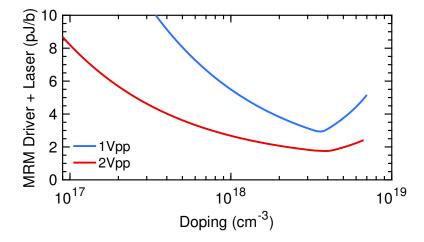

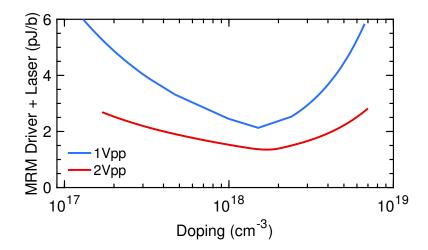

|      | Model-estimated total E/b for microring driver+laser for microring-based                                                                                   |                 |

|      | NRZ transmitter at 50Gb/s. Two different driver swings are considered (1V                                                                                  |                 |

|      | and 2V). The microring is optimized for each doping level, which corresponds                                                                               |                 |

| 9 15 | to the designs in Fig. 3.10 and 3.11                                                                                                                       | 28              |

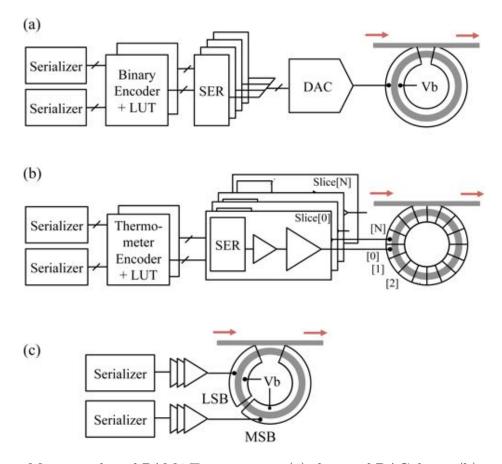

| 5.15 | Microring-based PAM4 Transmitters: (a) electrical DAC driver (b) optical DAC based on segmented microring (c) microring with two segments                  | 30              |

| 3.16 | (a) Linearity comparison between 5-bit electrical DAC and 5-bit optical DAC                                                                                | 90              |

|      | for MRM-based transmitter. (b) Transmission spectra for a microring with                                                                                   |                 |

|      | two binary weighted segments. The microring here has an optical bandwidth                                                                                  |                 |

| 2 17 | of 25GHz.                                                                                                                                                  | 31              |

| 3.17 | Model estimated total E/b for microring driver+laser for microring-based PAM4 transmitter at 50Gb/s. Two different driver swings are considered (1V        |                 |

|      | and 2V). The microring is optimized for each doping levels, which corresponds                                                                              |                 |

|      | to the designs in Fig. 3.10 and 3.11                                                                                                                       | 32              |

| 3.18 |                                                                                                                                                            |                 |

|      | transmitter. The microrings are optimized in each case with the same process                                                                               |                 |

|      | and link constraints. The optical power for y-axis is normalized to the input                                                                              | 0.0             |

| 3.19 | power for microrings                                                                                                                                       | 33              |

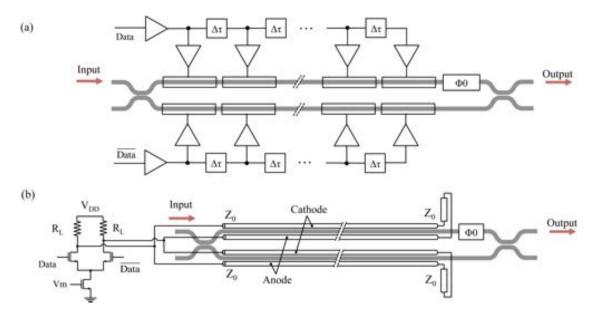

| 5.15 | chitecture of Traveling wave Mach-Zehnder Modulator (TW-MZM)                                                                                               | 34              |

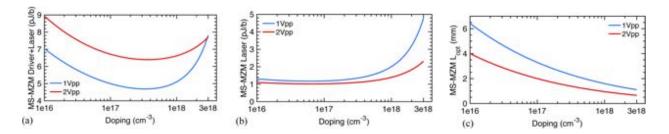

| 3.20 | Optimization results for multi-stage MZM transmitters at 50Gb/s with two                                                                                   | 0.              |

|      | peak-to-peak voltage swings (1V and 2V). (a) the total transmitter E/b, (b)                                                                                |                 |

| 0.01 | laser E/b, (c) the optimal arm length $L_{opt}$                                                                                                            | 35              |

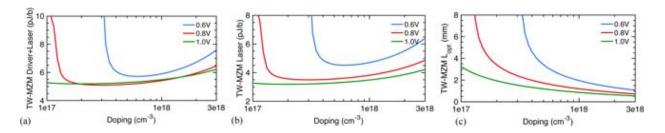

| 3.21 | Optimization results for traveling-wave MZM transmitters at 50Gb/s with                                                                                    |                 |

|      | three differential peak-to-peak voltage swings $V_{TW}$ (0.6, 0.8, 1.0V). (a) the total transmitter E/b, (b) laser E/b, (c) optimal arm length L           | 36              |

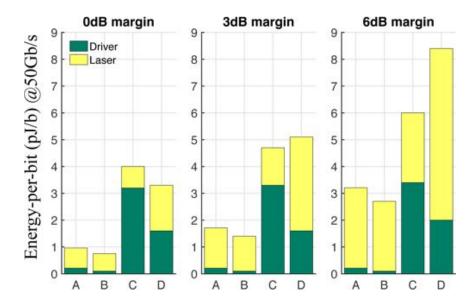

| 3.22 | Detailed energy breakdown and energy efficiency comparison between opti-                                                                                   | 90              |

|      | mized (A) NRZ-MRM, (B) PAM4-MRM, (C) MS-MZM and (D) TW-MZM transmitters at 50Gb/s. Three different link margins are considered: 0dB,                       |                 |

|      | 3dB and 6dB                                                                                                                                                | 39              |

|      | out and out                                                                                                                                                | 9.              |

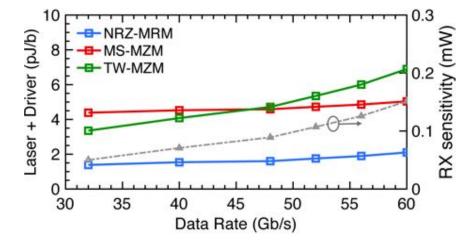

| Energy efficiency comparison between optimized NRZ-MRM, MS-MZM and TW-MZM transmitters at different data-rates. The gray line shows the receiver sensitivity vs data-rate according to measurement in [4] | 39                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

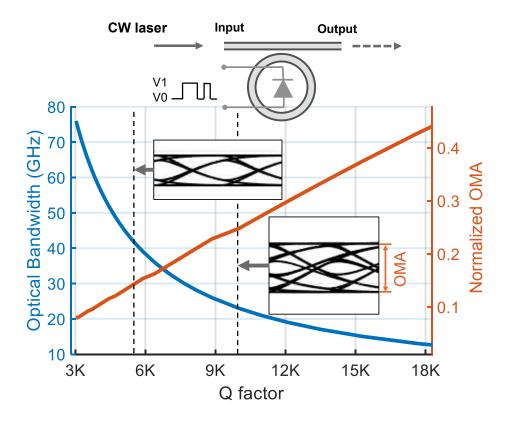

| Bandwidth and OMA trade-off of microring modulator                                                                                                                                                        | 42<br>43                                                        |

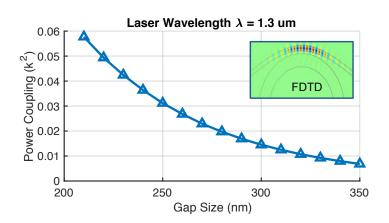

| coefficient extracted from Lumerical FDTD simulation                                                                                                                                                      | 43                                                              |

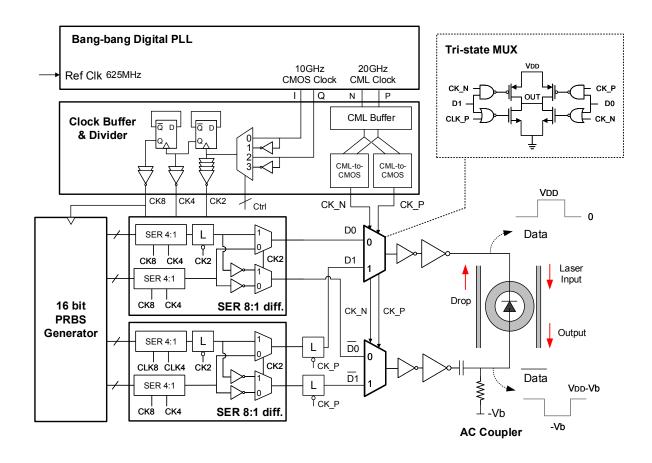

|                                                                                                                                                                                                           | 45                                                              |

| Block diagram of the single-eneded NRZ transmitter                                                                                                                                                        | 46                                                              |

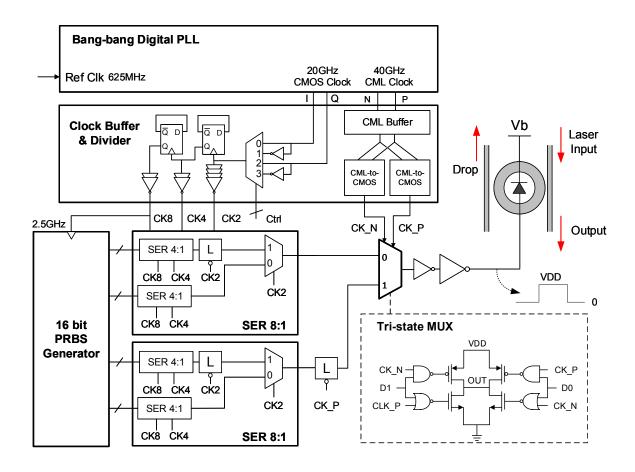

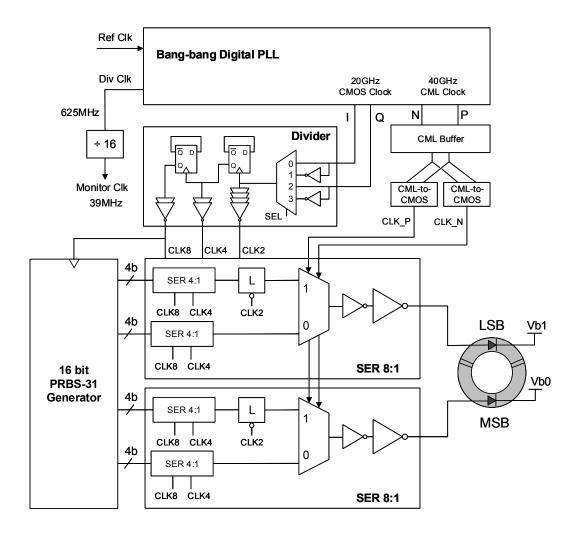

| System diagram of the PAM4 transmitter                                                                                                                                                                    | 47<br>48                                                        |

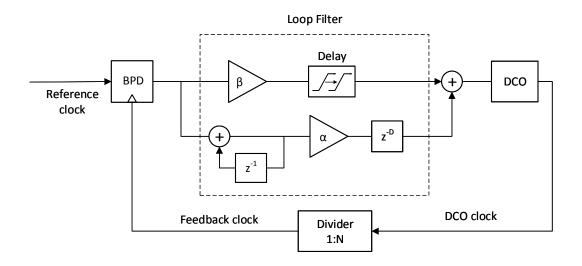

| Block diagram of the digital PLL                                                                                                                                                                          | 49                                                              |

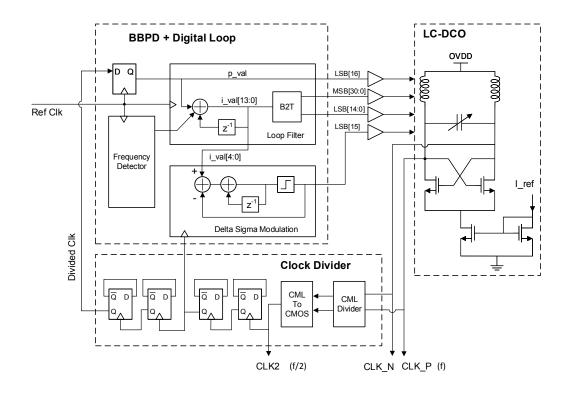

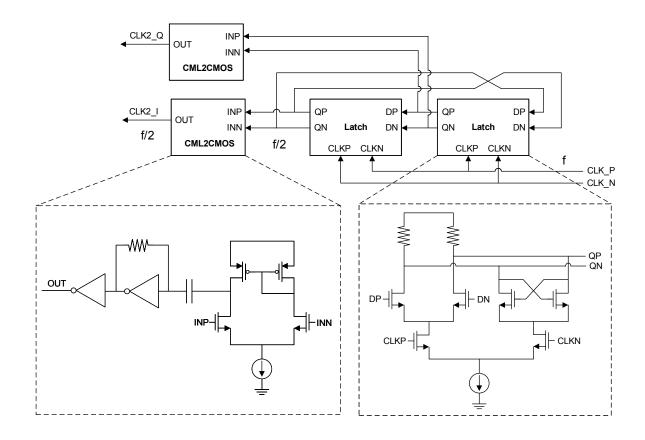

| Block diagram of the high-speed divider of the digital PLL                                                                                                                                                | 50                                                              |

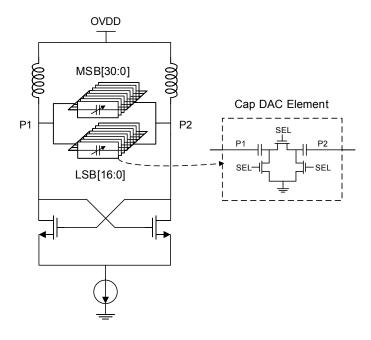

| Block diagram of the DCO of the digital PLL                                                                                                                                                               | 51                                                              |

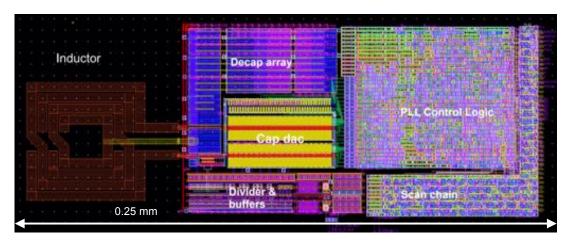

| Layout of the digital PLL and its sub-blocks                                                                                                                                                              | 51                                                              |

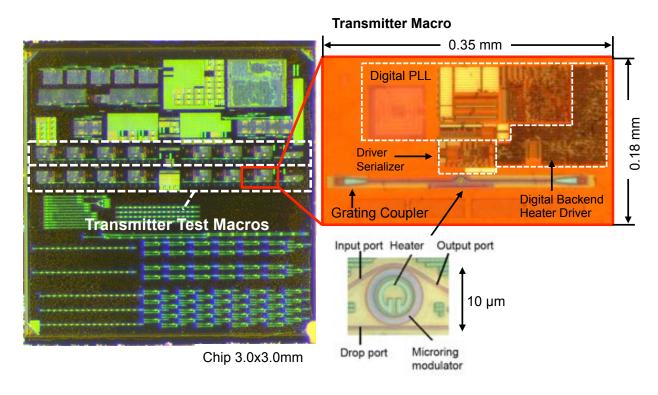

|                                                                                                                                                                                                           | 52                                                              |

|                                                                                                                                                                                                           |                                                                 |

|                                                                                                                                                                                                           | 53                                                              |

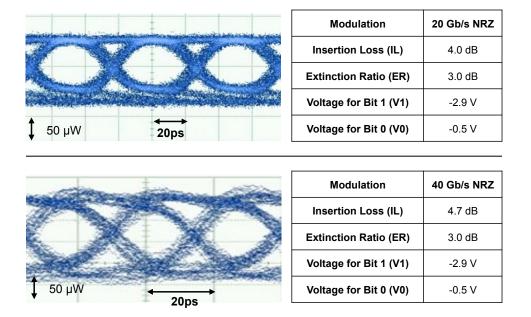

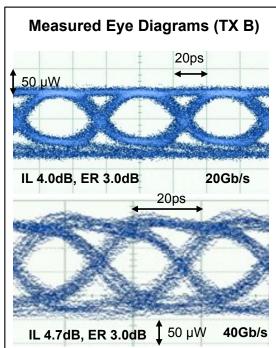

|                                                                                                                                                                                                           | 54                                                              |

|                                                                                                                                                                                                           | $\frac{54}{54}$                                                 |

|                                                                                                                                                                                                           | 94                                                              |

|                                                                                                                                                                                                           | 55                                                              |

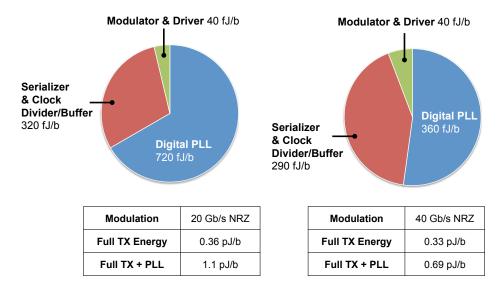

|                                                                                                                                                                                                           |                                                                 |

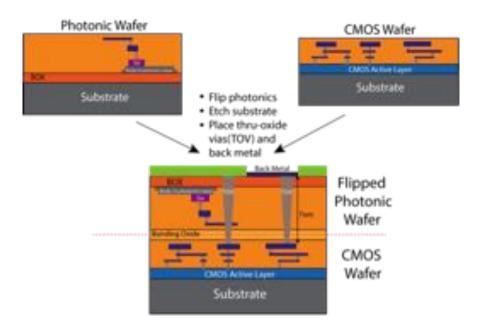

| Cross-section of 3D heterogeneous integration process                                                                                                                                                     | 57                                                              |

|                                                                                                                                                                                                           | 58<br>59                                                        |

|                                                                                                                                                                                                           | 59<br>59                                                        |

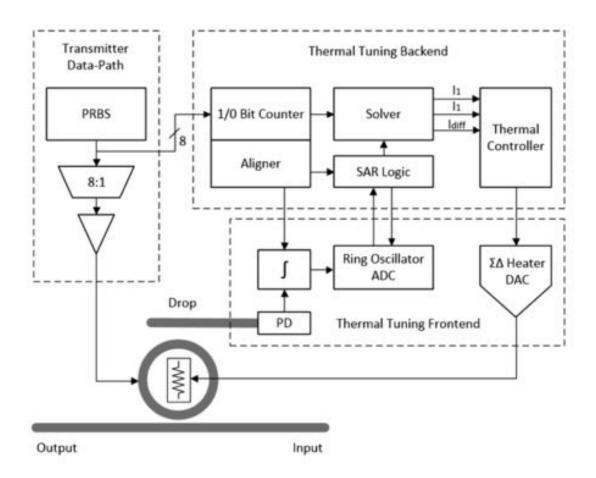

|                                                                                                                                                                                                           | 61                                                              |

|                                                                                                                                                                                                           | 61                                                              |

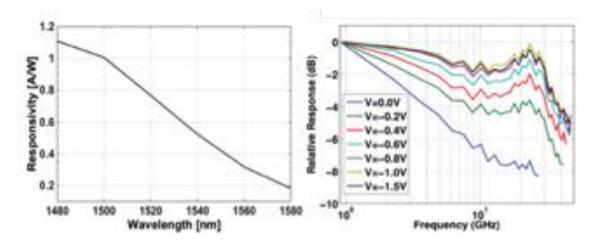

| Measured photodiode responsivity over 100 nm wavelength range and its fre-                                                                                                                                |                                                                 |

| quency response (with 50Ohm load) for different bias voltages                                                                                                                                             | 62                                                              |

| ÿ I                                                                                                                                                                                                       |                                                                 |

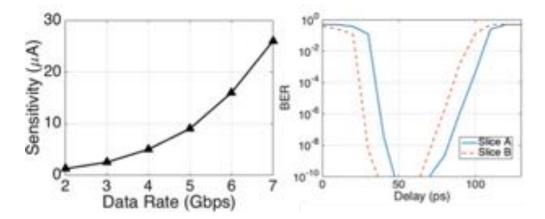

|                                                                                                                                                                                                           | 62                                                              |

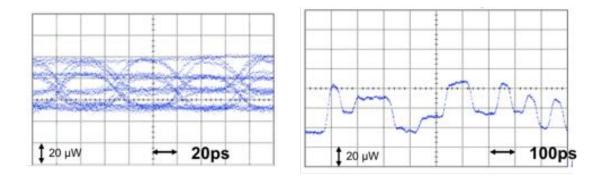

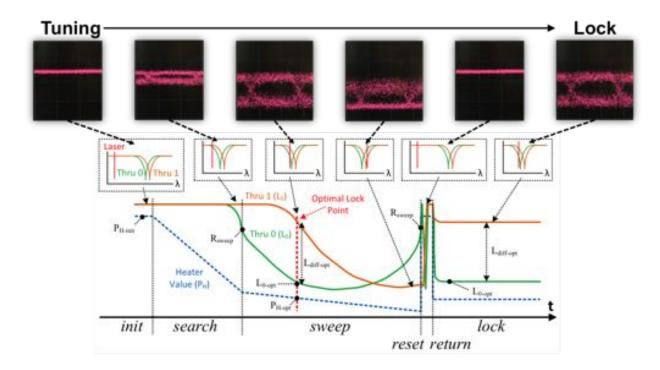

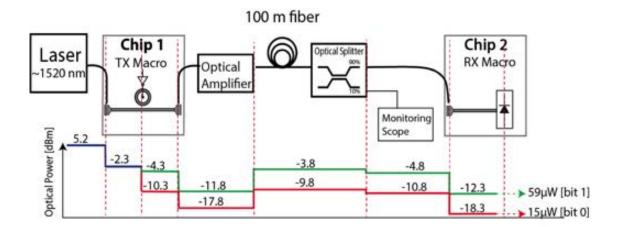

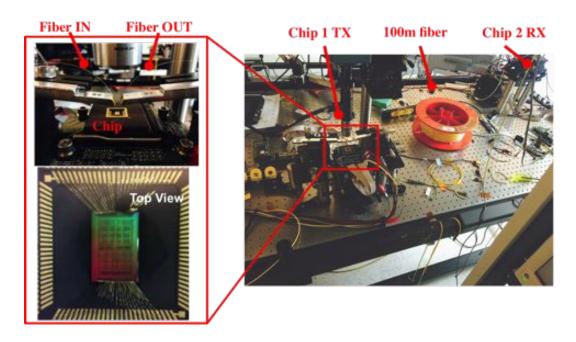

|                                                                                                                                                                                                           | 64                                                              |

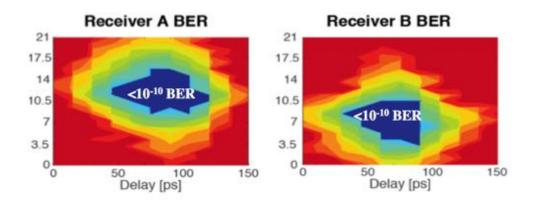

|                                                                                                                                                                                                           | 65<br>66                                                        |

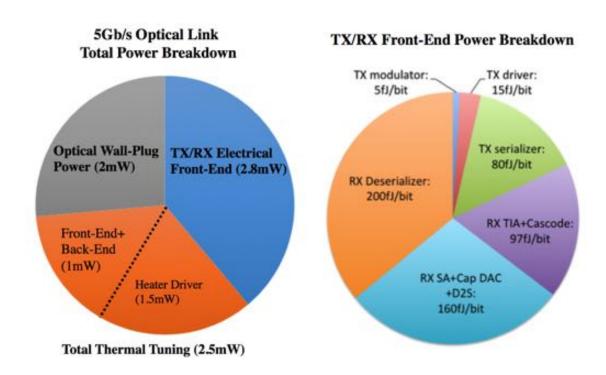

|                                                                                                                                                                                                           | 66                                                              |

|                                                                                                                                                                                                           | 67                                                              |

|                                                                                                                                                                                                           | 67                                                              |

|                                                                                                                                                                                                           | 68                                                              |

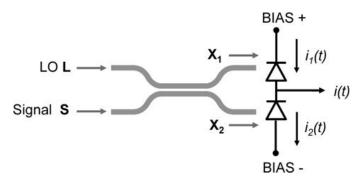

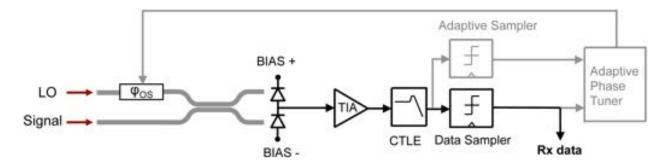

| Schomatic of balanced detection Signals I. C. V. and V. are complex num                                                                                                                                   |                                                                 |

| bers and present the electric field of the lightwave. $i(t)$ is the final output                                                                                                                          |                                                                 |

|                                                                                                                                                                                                           | 70                                                              |

| idontical photodiodos                                                                                                                                                                                     | /!!                                                             |

| identical photodiodes                                                                                                                                                                                     | 70                                                              |

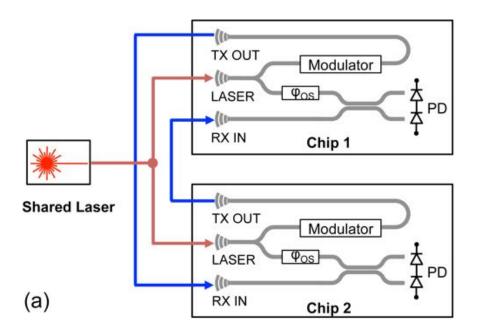

|                                                                                                                                                                                                           | ceiver sensitivity vs data-rate according to measurement in [4] |

| 6.3  | Proposed laser-forwarding architectures (b): each chip has its own co-located               |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | laser source and forwards it to the receiving chip. Blue lines are the signal               |     |

|      | transmission fibers and red lines are the laser distribution fibers                         | 72  |

| 6.4  |                                                                                             | 73  |

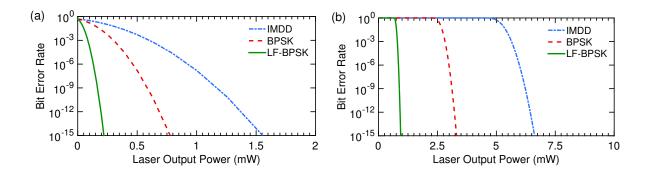

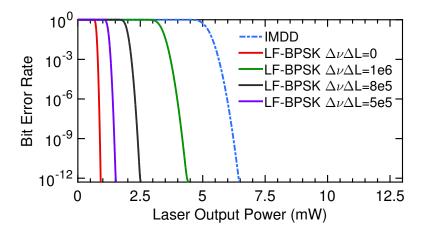

| 6.5  | (a) BER vs. laser output power at 50Gbps in the noise-limited regime. The                   |     |

|      | proposed LF-BPSK architecture could reduce laser power by 7.3x compared                     |     |

|      | with conventional IMDD link. (b) BER vs. laser output power in the swing-                   |     |

|      | limited regime. The proposed LF-BPSK architecture could reduce laser power                  |     |

|      | by 6.8x compared with IMDD. No link margin is considered for optical power                  |     |

|      |                                                                                             | 76  |

| 6 6  | estimation                                                                                  | 76  |

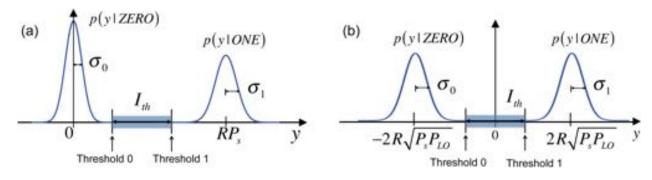

| 6.6  | (a) Probability density function (PDF) of the received signal y in a IMDD                   |     |

|      | receiver, conditioned on the transmitted bit, ZERO or ONE. (b) PDF of $y$ in                |     |

|      | a BPSK link. $I_{th}$ represents the minimum input swing requirement imposed                |     |

|      | by the data sampler                                                                         | 76  |

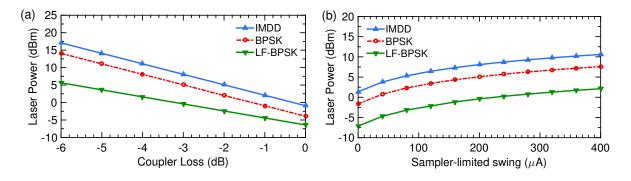

| 6.7  | (a) To achieve $10^{-12}$ BER at 50 Gbps, required laser output power versus                |     |

|      | coupler loss for different link architectures, (b) To achieve $10^{-12}$ BER at 50          |     |

|      | Gbps, required laser output power versus sampler-limited swing for different                |     |

|      | link architectures                                                                          | 77  |

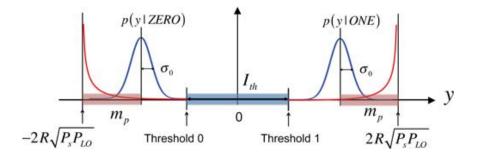

| 6.8  | Noise distribution with laser phase noise effects. The blue margin is reserved              |     |

|      | for sampler-limited swing $I_{th}$ . The red margins on the two sides are chi-              |     |

|      | squared noise caused by laser phase noise. The sum of thermal noise and                     |     |

|      | shot noise obeys Gaussian distribution with variation $\sigma_0^2$ . The peaks of the       |     |

|      | conditioned pdf are moved closer due to the added margin $m_p$ for phase noise              |     |

|      | effects                                                                                     | 79  |

| 6.9  | Estimated upper bound of BER for a 50 Gbps LF-BPSK link, considering laser                  |     |

|      | phase noise, shot noise, thermal noise and sampler-limited swing requirement.               | 80  |

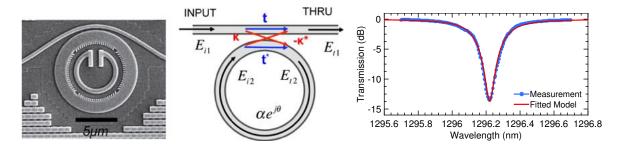

| 6.10 | From left to right are an SEM image of a microring modulator fabricated in                  |     |

|      | zero-change 45nm CMOS process [6], model diagram of the microring, and                      |     |

|      | the measured and modeled transmission spectra                                               | 80  |

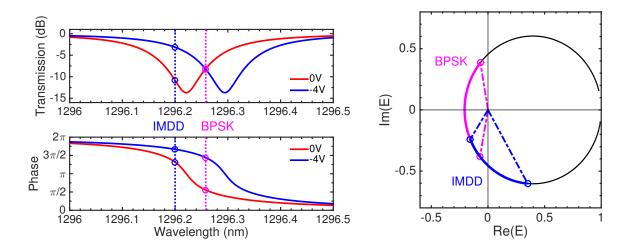

| 6.11 | Left is the transmission spectra and phase response of a microring modulator,               |     |

|      | where the two dashed lines represent nominal laser wavelength for the two                   |     |

|      | modulation schemes. Right is the phasor diagram of a microring modulator                    |     |

|      | marked with modulation trajectories                                                         | 82  |

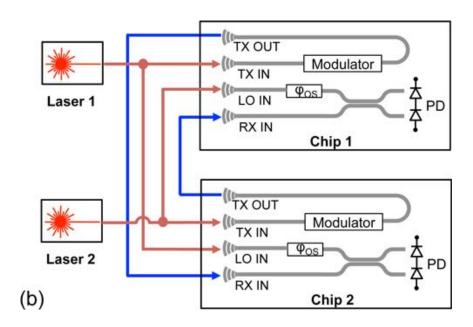

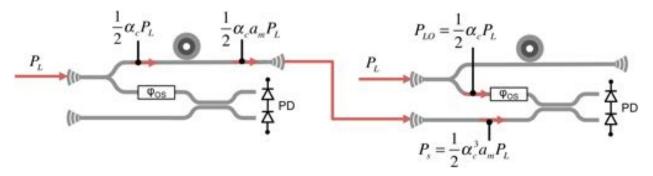

| 6.12 | System diagram of microring-based laser-forwarding coherent link. On-chip                   |     |

|      | 3dB splitting is used in this configuration. $P_L$ is the laser output power, $\alpha_c$ is |     |

|      | coupler loss, $\phi_{OS}$ is tunable phase offset for noise tracking and eye optimization.  | 82  |

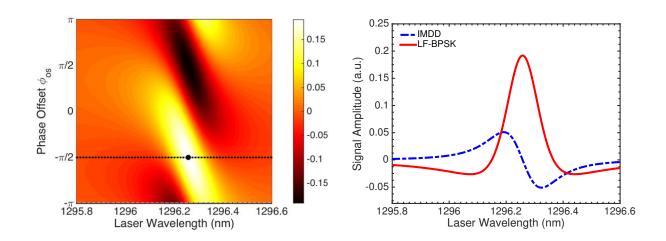

| 6.13 | Left is the contour of the received signal in LF-BPSK vs. phase offset $\phi_{OS}$          |     |

|      | and laser wavelength. The optimal point is marked with the black dot and                    |     |

|      | the optimal phase offset with the dashed line. Right is the received signal for             |     |

|      | IMDD and LF-BPSK vs. laser wavelength, assuming an optimal $\phi_{OS}$                      | 84  |

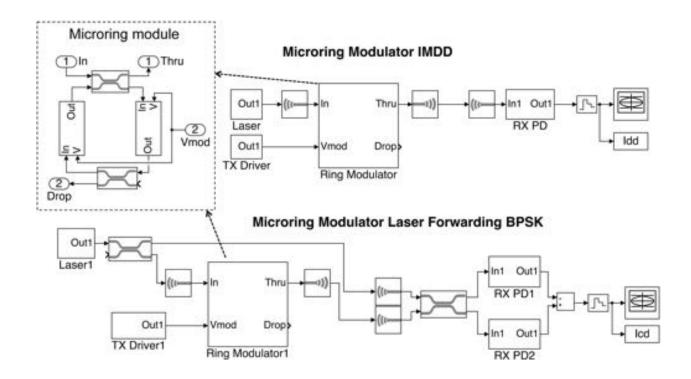

| 6.14 | Simulink schematics for optical link simulation. Top schematic is for microring             | _   |

|      | modulator based IMDD link. Bottom schematic is for microring modulator                      |     |

|      | based laser forwarding coherent link. The simulation framework supports all                 |     |

|      | basic optical devices such as laser, modulator, photodetector, coupler and                  |     |

|      | · · · · · · · · · · · · · · · · · · ·                                                       | Q A |

|      | splitter                                                                                    | 84  |

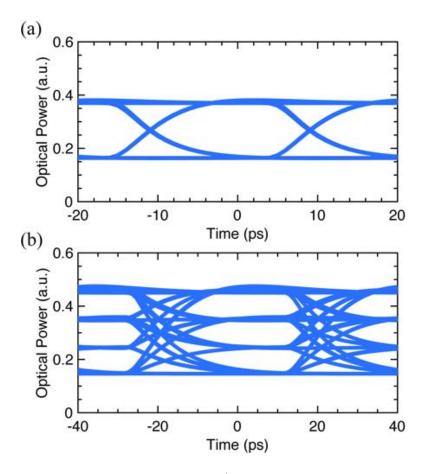

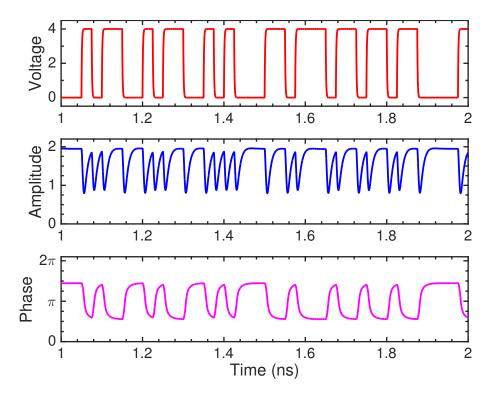

| 6.15 | Transient simulation results for microring modulator in BPSK mode. From                                                                                                                     |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | the top to bottom are the waveforms of drive voltage, amplitude of the mod-                                                                                                                 |     |

|      | ulated signal and phase of the modulated signal                                                                                                                                             | 85  |

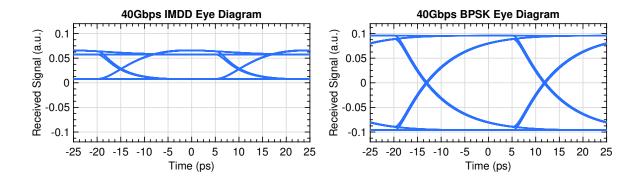

| 6.16 | Simulated eye diagram for IMDD link and laser forwarding BPSK link. Note                                                                                                                    |     |

|      | the laser power is set the same and the scale for signal amplitude is the same.                                                                                                             | 85  |

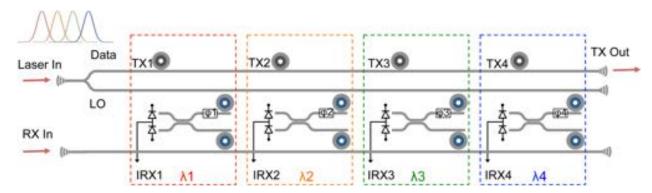

| 6.17 | Proposed microring-based WDM coherent link architecture with laser for-                                                                                                                     |     |

|      | warding configuration. Microring-based modulators and filters are used for                                                                                                                  |     |

|      | energy-efficient modulation and intrinsic wavelength selectivity. In this exam-                                                                                                             |     |

|      | ple, on-chip optical power splitting between LO and signal is adopted. Off-chip                                                                                                             |     |

|      | optical power splitting can also be used                                                                                                                                                    | 86  |

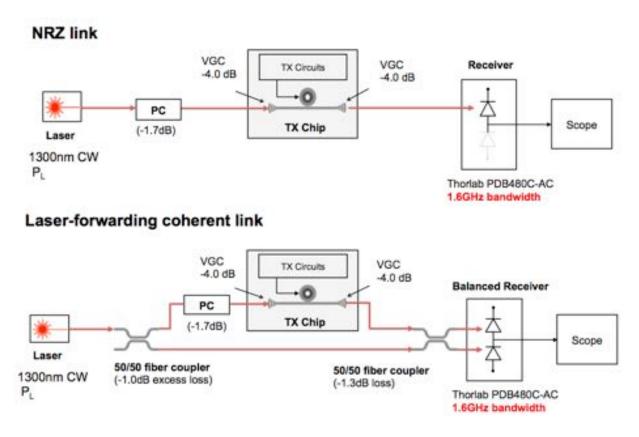

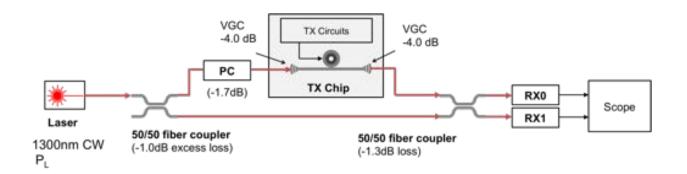

|      | Measurement setup of NRZ link and laser-forwarding coherent link                                                                                                                            | 87  |

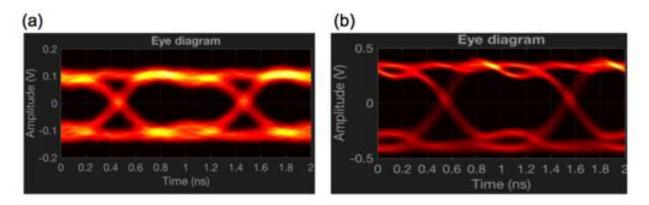

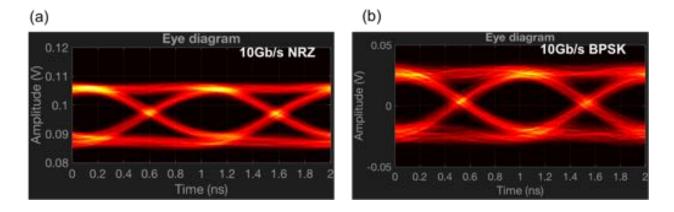

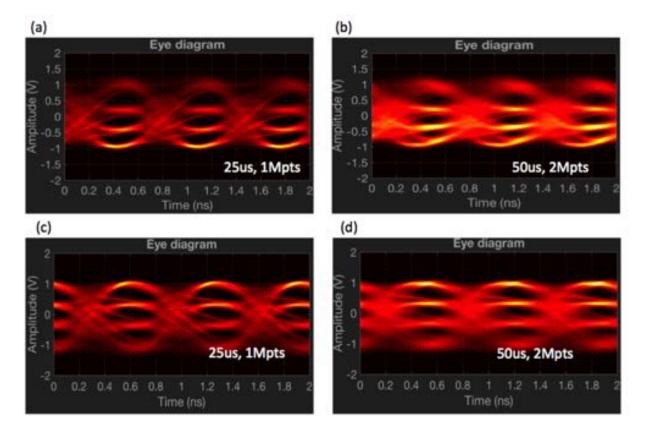

| 6.19 | Comparison between the eye diagrams of NRZ link and LF-BPSK link. Com-                                                                                                                      |     |

|      | mon conditions: bias condition $V_b = 0.5V$ , measurement duration = $25\mu s$ ,                                                                                                            |     |

|      | samples = 1Mpts. (a) NRZ modulation, laser output power $P_L = 4dBm$ , (b)                                                                                                                  |     |

|      | LF-BPSK, laser output power $P_L = 0$ dBm                                                                                                                                                   | 88  |

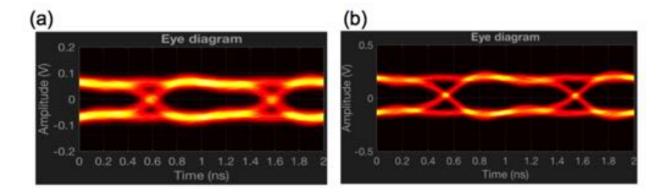

| 6.20 | Comparison between the eye diagrams of NRZ link and LF-BPSK link. Com-                                                                                                                      |     |

|      | mon conditions: bias condition $V_b = 1.0V$ , measurement window = $25\mu s$ ,                                                                                                              |     |

|      | samples = 1Mpts. (a) NRZ modulation, laser output power $P_L = 4dBm$ , (b)                                                                                                                  |     |

|      | LF-BPSK, laser output power $P_L = 0$ dBm                                                                                                                                                   | 89  |

|      | LF-BPSK measurement setup with two standalone receivers                                                                                                                                     | 90  |

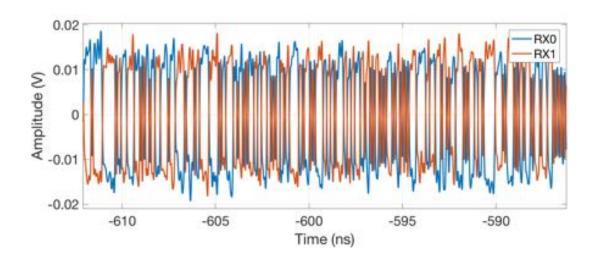

| 6.22 | The output waveforms of the two receivers in the modified LF-BPSK setup                                                                                                                     | 0.0 |

| ഭവാ  | at 10Gbps                                                                                                                                                                                   | 90  |

| 0.23 | Comparison between the 10Gb/s eye diagrams of NRZ link and LF-BPSK                                                                                                                          |     |

|      | link. Bias condition $V_b = 1.0V$ (a) 10Gb/s NRZ modulation, laser output                                                                                                                   | 00  |

| 6 24 | power $P_L = 10 \text{dBm}$ , (b) $10 \text{Gb/s}$ LF-BPSK, laser output power $P_L = 7 \text{dBm}$ .<br>(a) $1 \text{Gb/s}$ LF-BPSK eye diagram, measurement window $= 25 \mu s$ , samples | 90  |

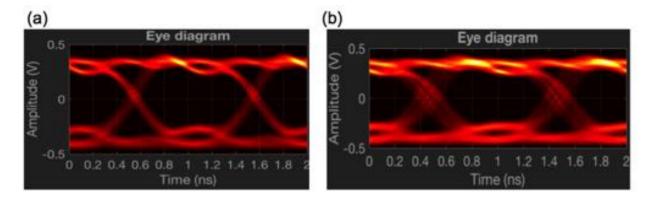

| 0.24 | (a) 1Gb/s LF-Bi SK eye diagram, measurement window = $25\mu s$ , samples = 1Mpts; (b) 1Gb/s LF-BPSK eye diagram, measurement window = $50\mu s$ ,                                           |     |

|      |                                                                                                                                                                                             | 91  |

| 6.25 | 1 1                                                                                                                                                                                         | 91  |

| 0.20 | $(a)$ 3Gb/s EF-QF SK cyc diagram, DAC code = $4/5/16$ , incastrement window = $25\mu s$ , samples = 1Mpts; (b) 3Gb/s LF-QPSK eye diagram, DAC code =                                        |     |

|      | $-25\mu$ s, samples = 1Mpts, (b) 3Gb/s LF-QF SK eye diagram, DAC code = $4/9/15$ , measurement window = $50\mu$ s, samples = 2Mpts; (c) 3Gb/s LF-QPSK                                       |     |

|      | eye diagram, DAC code = $5/10/15$ , measurement window = $25\mu s$ , samples =                                                                                                              |     |

|      |                                                                                                                                                                                             |     |

|      | 1Mpts; (d) 3Gb/s LF-QPSK eye diagram, DAC code = 5/10/15, measurement                                                                                                                       | 00  |

|      | window = $50\mu s$ , samples = $2\text{Mpts} \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                               | 92  |

# Chapter 1

## Introduction

Today's computers are largely limited by communication bandwidth at every level of the system hierarchy: processor chip, server blade, rack, and data center. Silicon photonics copackaged or integrated with large-scale systems-on-a-chip holds great promise in meeting the high bandwidth and low-energy demands of machine-learning-driven next-generation data-center and high-performance computing interconnects. In particular, silicon photonics has stepped up as a clear contender for the next-generation 400G inter-rack interconnects and 100G intra-rack interconnects in data centers. Recent years have seen great efforts and rapid progress in developing and commercializing silicon photonics technologies from platforms, devices, circuits to systems [1-33]. One recent milestone is the demonstration of the first single-chip computer that communicates directly with light based on monolithic photonics in 2015 [2]. This is an example of how the close integration between photonics and electronics could enhance CMOS capabilities and open the door to new innovations as transistor scaling slows down in the post-Moore's law era.

However, there are still many challenges in the field of silicon photonic interconnects despite the great progress. The author attempts to address three challenges in the scope of this dissertation. First, the close electronic-photonic integration requires a new co-design methodology that is system oriented. Second, silicon photonics transceivers, especially the monolithic transmitters, that have been reported so far have limited data rate and energy efficiency mainly due to lack of co-optimization. Third, due to the limited wallplug efficiency and integration density of the lasers, laser power has become the bottle-neck of the overall system energy efficiency. Detailed description of these challenges as well as research background is introduced in Chapter 2. They are addressed one by one from Chapter 3 to Chapter 6, with innovative approaches in modeling, chip-level implementations to system architecture.

In Chapter 3, the author presents a new co-optimization and verification framework to address the challenge of system-oriented electronic-photonic co-design. This framework enables engineers to optimize high-speed silicon photonics transmitters in the context of a practical optical link. It is applicable to most of today's silicon photonics platforms that rely on PN junction based phase shifters. The author also presents the co-design methodology and co-design techniques for high-speed transmitters and the in-depth comparison between the different modulator types and modulation schemes. The work is published as "Electronic-Photonic Co-Optimization of High-Speed Silicon Photonic Transmitters", Sen Lin, Sajjad Moazeni, Krishna T. Settaluri, Vladimir Stojanović, Journal of Lightwave Technology, 2017.

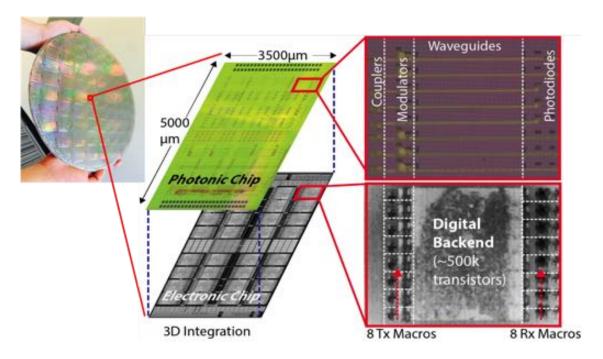

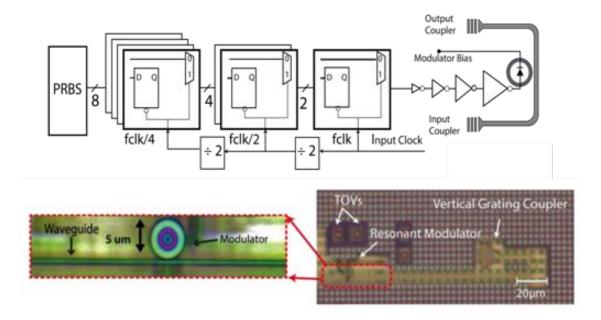

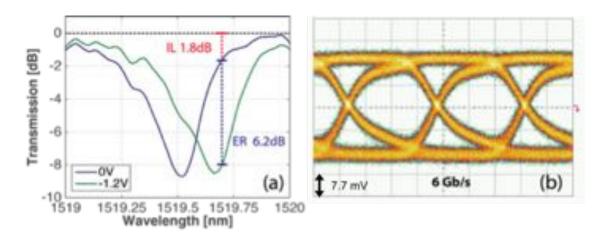

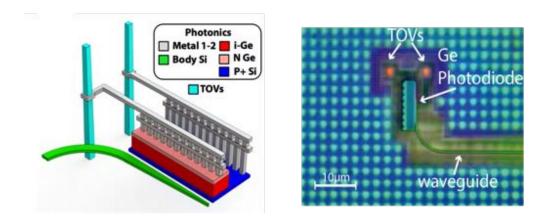

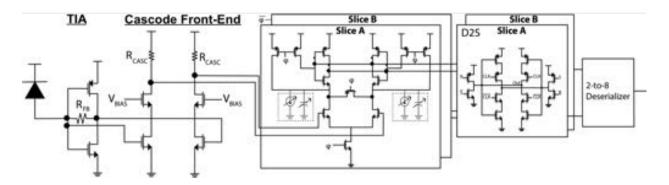

Next, the author addresses the second challenge and applies this co-design methodology to the chip-level high-speed optical interconnect designs based on state-of-the-art silicon photonics platforms. In Chapter 4, the author demonstrates a 40Gb/s optical non-returnto-zero (NRZ) transmitter and a 40Gb/s optical pulse-amplitude-modulation (PAM) transmitter. Both transmitter designs use monolithic silicon microring modulators in standard 45nm CMOS SOI process. The NRZ transmitter (including a serializer and modulator driver) achieves total energy efficiency of 330fJ/b and bandwidth density of 6.7Tb/s/mm<sup>2</sup> at 40Gb/s. To our knowledge, it is by far the fastest and most energy efficient monolithic optical transmitter ever demonstrated. In this work, the author designed the circuits and optimized the modulators for high-speed transmitters. In Chapter 5, the author presents the first demonstration of a complete silicon photonic interconnect on a 3D integrated electronicphotonic platform. The key circuit blocks for wavelength-mutiplexing-division (WDM) architectures are demonstrated along with state-of-art silicon photonic modulator and photodetector. This work is done in collaboration with Krishna Settaluri, Sajjad Moazeni, Chen Sun, Erman Timurdogan, Michele Moresco, Zhan Su, Yu-Hsin Chen, Gerald Leake, Douglas LaTulipe, Colin McDonough, Jeremiah Hebding and Douglas Coolbaugh. It is published as "Demonstration of an Optical Chip-to-Chip Link in a 3D Integrated Electronic-Photonic Platform", European Solid-State Circuits Conference (ESSCIRC), 2015. The author's main contribution is the design of transmitter circuits and the full-chip integration of the WDM test chip.

The last part of the study looks beyond the conventional silicon photonic interconnects and explores the feasibility of coherent optical communications with silicon photonics. In Chapter 6, the author takes a system-level approach and addresses the laser power challenge by proposing a short-reach laser-forwarding coherent architecture. The key concepts of the proposed architecture are verified both analytically and experimentally. This proposed architecture saves the laser power by 6-7.5 times and could enable complex coherent modulation for the future short-reach optical links.

# Chapter 2

# Background

#### 2.1 Silicon Photonic Interconnects

Silicon photonics can potentially achieve lower energy and higher bandwidth density over traditional electrical I/O. Additionally, optical links benefit from distance insensitivity due to the inherently low loss of fibers, allowing for new types of connectivity and network organization in modern digital systems and data-centers. Wavelength-division multiplexing (WDM) may also be realized to place many data channels on a single optical fiber, thereby increasing the bandwidth density while retaining energy efficiency and breaking the I/O pin limitations imposed by the electronics.

Compared with conventional optical interconnects, silicon photonic interconnects reduce manufacturing cost dramatically as the modulators and photodetectors are fabricated on standard silicon wafers instead of very expensive III-V wafers. In addition, silicon photonics are generally compatible with CMOS processes, enabling large-scale integration between CMOS circuits and photonic devices, such as monolithic integration and 3D integration. Silicon photonic interconnects achieve high bandwidth density and high energy efficiency through close electronic-photonic integration.

## 2.1.1 Silicon photonic modulator and photodetector

On the transmitter side, three types of silicon photonic modulators are of most interest: microring modulator (MRM), Mach-Zehnder modulator (MZM) and electro-absorption modulator (EAM). Microring modulators and EAMs are much more energy efficient than MZMs due to their compact sizes. Among these three types, microring modulator is the only one that has inherent wavelength selectivity and thus it has unmatched potential for future terabit per second dense wavelength division multiplexing (DWDM) links. Therefore, we choose

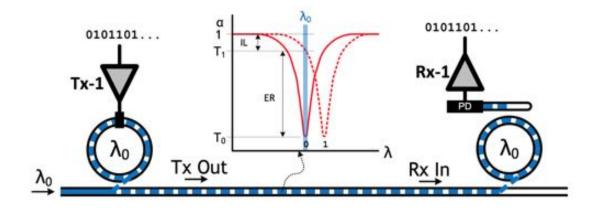

Figure 2.1: A single channel silicon photonic interconnect based on microrings. [1]

silicon microring modulators as the primary device for our high-speed link designs on both monolithic and 3D heterogenous platforms.

Fig. 2.1 shows the conceptual diagram of a single-channel silicon photonic link based on microrings. Microring modulator is a resonant photonic device and operates as a notch filter in optical spectrum near the laser wavelength. It modulates the incoming light from laser by shifting its own resonance in and out of the laser wavelenth. The resonance of microring modulators can be shifted by high-speed voltage drivers for high data rate modulation. The other two important specifications for optical transmitter are insertion loss (IL) and extinction ratio (ER) (defined as  $T_1/T_0$ ) as labeled in the same figure. Small IL and high ER could help increase the optical modulation amplitude (OMA) (defined as  $T_1 - T_0$ ) or reduce the required laser power in the link. Given the decrease in receiver sensitivity with increase in data-rate, the larger transmit OMA is required.

In Fig. 2.1, the optical receiver can use a microring filter to receive optical signal at a specific laser wavelength for WDM operation. The drop port of the optical filter is connected to a photodetector to convert optical signals into electrical signals. The photodetectors often require Ge or SiGe due to their good compatibility with standard CMOS process. Ge photodetectors can be used for both O-band and C-band receivers and they can typically achieve close to 1A/W responsivity in C-band [53]. SiGe photodetector can be only used for O-band and shorter wavelengths with much lower responsivity. SiGe already exists in standard CMOS processes as a strain-engineering material to improve the carrier mobility, enabling monolithic integration of silicon photonics into a standard CMOS process with zero change [2].

#### 2.1.2 WDM link architectures

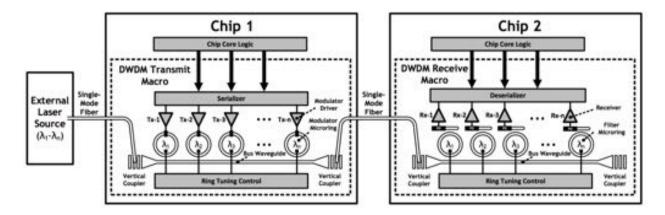

Fig. 2.2 shows the system diagram of a microring-based WDM optical link, where a bank of microrings are used for both transmitter channels and receiver channels. The microring

Figure 2.2: System diagram of a microring-based WDM optical link. [1]

modulator and filter operate in pairs as depicted in the single-channel diagram. Ring tuning control is implemented for all the transceiver channels to align the resonance wavelength of the microrings and lock them to the corresponding laser wavelength. The ring tuning control is critical to microring operations as they can calibrate process variation and compensate dynamic temperature fluctations. Detailed implementation and measurement results of a microring thermal tuner are dicussed in Chapter 5. The channel number of the WDM links is mainly limited by the cost of WDM laser source, which motivates our study on pushing the data rate boundary of silicon photonic interconnects.

#### 2.1.3 Coherent optical links

The link architectures mentioned in section 2.1.1 and 2.1.2 are based on amplitude modulation of the optical signal. Optical signals can carry information on both the amplitude and the phase, which allows more complex high-order modulation schemes and higher spectral efficiency. Studies also show that coherent detection schemes could require much fewer photons per bit than intensity modulation direct detection (IMDD) schemes [7–9].

To date, the focus of silicon photonic interconnects reserach has been on non-coherent optical interconnects. The short-reach optical interconnect standards for data centers are all non-coherent (e.g., 100G-SR4 and 100G-PSM4), which are based on the same intensity modulation direct detection (IMDD) architecture. In practice, coherent optical communication has been largely limited to long haul and metro applications due to its high cost, power, and complexity. For long-reach communication, the primary goal is to achieve high spectral efficiency for each optical channel. Silicon photonics transmitters with high-order modulation schemes such as quadrature amplitude modulation (QAM) have been demonstrated [10–12]. On the receiver side, the major challenge has been optical-carrier phase tracking [7], which requires high speed analog-to-digital converters (ADC) and digital signal processing (DSP). In contrast, cost and energy efficiency are the primary concerns for short-reach optical communication. As a result, coherent optical communication suitable

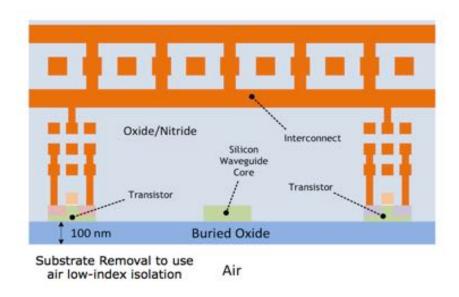

Figure 2.3: Cross-section view of the monolithic silicon photonics platform in 45nm SOI CMOS process. [1]

for short-reach applications has yet to be demonstrated. These challenges motivate us to look into new link architecture to enable low-cost short-reach coherent optical communication with silicon photonics. We propose and demonstrate a new, laser forwarded coherent link architecture tailored for low-cost energy efficient short-reach optical communication in Chapter 6.

#### 2.2 Silicon Photonics Platforms

#### 2.2.1 Monolithic silicon photonics platform

Silicon photonic interconnects benefit from the close integration between photonics and electronics in terms of performance, power and cost. Monolithic integration achieves the single-chip electronic-photonic integration and has been demonstrated in different SOI and bulk processes. One recent milestone in monolithic integration is the demonstration of first single chip computer with photonic I/O in GF 45nm SOI process [2].

Fig. 2.3 shows the cross-section view of monolithic silicon photonics platform in 45nm SOI CMOS process [2]. The core of the waveguide is based on the same crystalline silicon layer used for transistors, which has thickness of 80-100nm. Silicon has much higher refractive index ( $\sim 3.45$ ) compared to silicon oxide ( $\sim 1.45$ ), and with this high index contrast optical mode can be well confined in the waveguide with very low propagation loss (3-4dB/cm). Low-level metal routings are typically blocked above the silicon waveguide to avoid excess

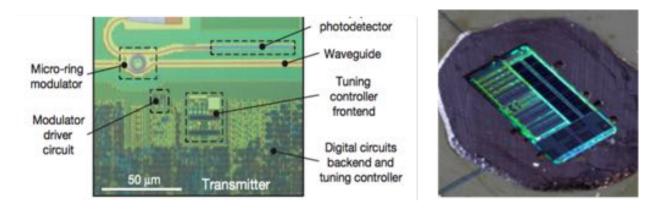

Figure 2.4: Photos of the first silicon photonic processor chip in 45nm SOI CMOS process.

loss. The thickness of the buried oxide is around 150nm. To prevent light from leaking into the substrate, the silicon substrate is removed with  $XeF_2$  dry etching. The author uses the technique to do both full and partial release of the processor chip [2]. This platform allows the integration of photonics and VLSI systems and opens the door to many opportunities on complex electro-optical systems. Based on this platform, we have successfully demonstrated the fastest and most efficient monolithic silicon photonics transmitters in Chapter 4 as well as the concept of laser-forwarding coherent link in Chapter 6.

#### 2.2.2 3D integrated silicon photonics platform

Although monolithic silicon photonics is a very promising technology, it has its own challenges in the short term. First, integration into nodes below 28nm is not possible using the crystalline Si (typically used for silicon-photonics) due to reduced thickness of the epi layers (sub 28nm only thin-body FDSOI and FinFETs are present). Second, it can impose additional constraints on photonics design and limit the performance of photonic devices, in particular, the modulation efficiency of modulator and the responsivity of photodetector.

Heterogeneous integration overcomes some of the limitations by decoupling photonic process from CMOS process. In this case, transistors and photonic devices can be optimized separately. This approach enables large-scale integration of silicon photonics and advanced bulk CMOS electronics with mature packaging solutions. It also relaxes design constraints on photonic devices and improves the performance of photonics.

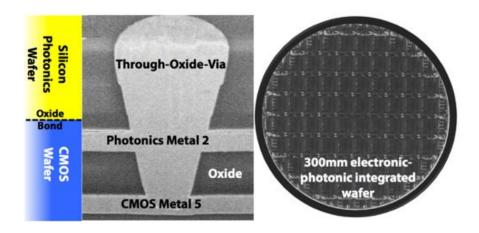

The first wafer-scale 3D integrated silicon photonics platform is developed through SUNY Poly Colleges of Nanoscale Science and Engineering (CNSE). The cross-section view and the top view of the 12-inch electronic-photonic wafer are shown in Fig. 2.5 [53]. The photonic devices on the top wafer and the electronic circuits on the bottom wafer (65nm bulk) are electrically connected through thru-oxide vias (TOVs), which have ultra-low parasitic capacitance of  $\sim$  3fF. Based on this platform, we have successfully demonstrated the first optical link using 3D integrated silicon photonics. The details are reported in Chapter 5.

Figure 2.5: Cross-section and top view of the electronic-photonic wafer [5]

## 2.3 Challenges and Opportunities

#### 2.3.1 Co-optimizing photonics and electronics

Optical links based on silicon photonics hold great promise for meeting the demands of next-generation 400G inter-rack interconnects and 100G intra-rack interconnects in data centers. To meet such demands, optical transceivers with datarates at or higher than 50Gb/s are of most interest in both wavelength-division mutiplexed (WDM) and parallel single-mode (PSM) systems. Recent years have seen great effort and rapid progress in the development and commercialization of silicon photonics technologies ranging from platforms, devices, and circuits, to large-scale systems [2, 18, 21–27]. Moreover, silicon photonic modulators and optical transceivers beyond 50Gb/s have recently been demonstrated in various photonic platforms [4, 13, 14, 28–30]. At these high data-rates, it is critical to consider holistically the design of the photonic and circuit components from the perspective of link energy-efficiency and bandwidth density.

In state-of-the-art 50Gb/s NRZ optical link based on Mach-Zehnder modulator (MZM), the driver and laser together consume more than 10pJ/b energy dominating the total link energy, compared to 1.4-3pJ/b consumed by the receiver [4, 14]. In contrast to MZMs, microring modulators (MRM) can consume less than 100fJ/b driver energy due to their compact sizes. The thermal tuning overhead for microrings can be as low as a few milliwatts per channel [31], which has negligible impact on the overall energy efficiency of the transmitter. Microring modulators have great potential for dense WDM systems due to their inherent wavelength selectivity. They have also shown promising high-speed operations for single-wavelength 50Gb/s links [13, 32, 33]. However, full optical links at such high datarate using microring modulators are yet to be demonstrated, which is in part due to unoptimized device designs and the inherent trade-offs between optical modulation amplitude (OMA) and optical bandwidth for microrings [34]. For both types of modulators, there are different architecture choices and also trade-offs between laser power and transmitter power. Addi-

tionally, they are both subject to the same technology constraints from the silicon photonics platforms and link specifications. As a result, it is critical yet challenging to co-optimize photonics alongside circuits. To date, there is still debate on which modulator architecture could be a better design choice for 50Gb/s optical channels in WDM and PSM systems.

#### 2.3.2 Pushing speed limits of photonics transmitters

Close integration of photonics with transceivers circuitry is critical for achieving ultra-low energy and high bandwidth densities (enabling low area overheads and new interconnect topologies). Monolithic silicon photonics is a potential solution that enables the closest proximity of electronics and photonics and large-scale integration. Recently, optical transceivers using monolithic silicon photonics in 45nm and 90nm SOI processes have been demonstrated [2, 23, 32, 33]. However, achieving high data-rates (25+ Gb/s) with sub-pJ/b energy-efficiency in order to meet the demands of the next wave of optical interconnects is still a challenge for these monolithic NRZ transmitters.

On one hand, Mach-Zehnder modulators (MZMs) have large optical bandwidth, but limited electrical bandwidth and large energy cost. On the other hand, microring modulators (MRMs) have narrower optical bandwidth but relatively large electrical bandwidth and low energy cost (due to their compact size). To achieve the high-modulation rate for target modulation depth while keeping the energy cost low, MRM-based NRZ transmitter requires careful co-design of electronic circuitry and photonic devices.

#### 2.3.3 Reducing the high power consumption of laser sources

Integrated silicon photonics has shown unmatched potential in providing high-data bandwidth with low-cost and high-energy efficiency [2, 13–18]. However, embedded laser power consumption for silicon photonic links has become a bottleneck for further improving overall energy efficiency. This problem is more prominent for high-speed optical interconnects, as receiver sensitivity degrades significantly at high data rates [19, 20]. The performance of photonic devices also imposes many constraints on the overall energy efficiency of a photonic interconnect. The key constraints include fiber-to-chip coupling loss, modulator insertion loss, and laser wall-plug efficiency. Most silicon-photonic chips today use off-chip lasers, and thus the total channel loss outside the laser module includes losses of at least three optical coupling interfaces: two on the transmitter and one on the receiver. Post-packaging loss of a fiber-to-chip coupler is typically in the range of 2-4 dB [2, 13, 14]. Typical insertion loss of a Mach-Zehnder modulator with a reasonable extinction ratio is around 5 dB [15]. Under these constraints and typical link loss margins of 3dB, the required optical power from the laser has to be 9-15 dBm to maintain a reasonable bit error rate (BER) at 50 Gbps [14] (i.e. at least 1e-4 or 1e-6 for forward error correction (FEC) links and 1e-12 for uncoded low-latency high-performance computing interconnects). In addition, considering a typical

uncooled laser wall-plug efficiency of 10%, the laser itself can consume 80 mW to 320 mW for a single optical channel. This could be prohibitive, especially for scenarios in which photonic transceivers aim to get closer to the processor and switch chips and further cut the interconnect energy. Typically, lasers are thermally stabilized, which adds another 3-4x reduction in wall-plug efficiency and makes the need for link co-optimization even more significant. Our research aims to explore new solutions to this problem from a link architecture perspective. We propose and demonstrate the concepts of laser-fowarding coherent silicon photonic links in Chapter 6.

# Chapter 3

# Electronic-photonic Co-Optimization of Silicon Transmitter

This chapter addresses the challenges discussed in Section 2.3.1 and provides new insights and intuition into high-speed silicon photonics transmitters. This chapter focuses on a comparison between microring and Mach-Zehnder modulators given the same technology constraints at 50Gb/s. We begin with an overview of the optimization framework in Section 3.1 and introduction of a compact model for phase shifters in Section 3.2. The phase shifter model is verified with experimental data and later sets the foundation for microring and Mach-Zehnder modulator modeling. In Section 3.3, the optimization of the microring-based transmitter is carried out for 50 Gb/s optical links to obtain the best energy efficiency. A new Simulink toolbox is introduced to capture dynamic behaviors of MRMs. This general-purpose toolbox can be used for simulating other optical systems as well. In addition, an MRM-based PAM4 transmitter is analyzed as a potential way to mitigate optical bandwidth constraints. In Section 3.4, a co-optimization of the Mach-Zehnder transmitter is carried out for both multi-stage (MS) and traveling-wave (TW) drivers. Finally, a comparison between optimized MRM-based TX and optimized MZM-based TX given the same technology constraints is discussed in Section 3.5. Section 3.6 summarizes this chapter.

## 3.1 Overview of Co-optimization Framework

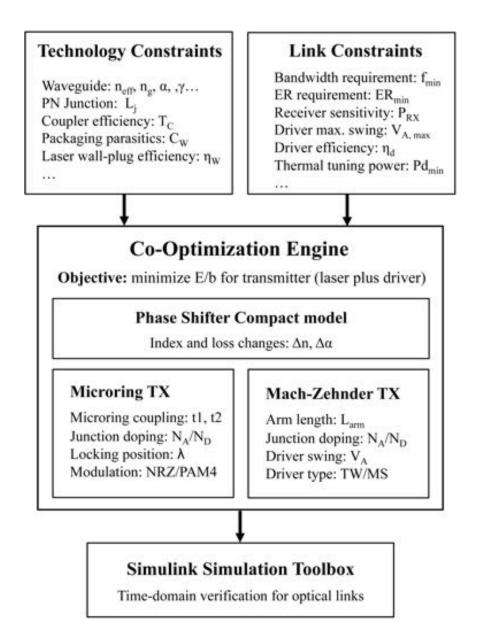

The objectives of the proposed framework are to lay the foundation for silicon photonics device and link co-design and to be readily applicable to a multitude of silicon photonics platforms. This framework is called "co-optimization" as it optimizes photonic device parameters such as doping levels and geometries alongside CMOS circuits and architectural choices. The optimization goal is to minimize the overall energy-per-bit (E/b) of the transmitter macro (laser plus driver) under both technology and link design constraints. The

detailed constraints, as well as the overview of optimization framework, are shown in Fig. 3.1.

Challenges for designing a comprehensive, yet general, co-optimization framework stem mainly from three important criteria. First, the framework needs to be specific enough to capture the intricacies of technology-dependent photonic device physics, without necessarily overburdening the optimizer. Second, the model needs to be generic enough to characterize the common waveguide and junction designs across many silicon photonics platforms. Third, it needs to consider key link constraints and provide a link-level picture that includes the transmitter, receiver and laser. Previous literature on link-level analysis and modeling of silicon photonics transmitters [19, 31, 35] often treats the optical devices as black boxes and does not consider doping and device design parameters altogether. For example, the critical trade-off between phase shift and optical loss under process constraints is often neglected. Other literature focusing on photonic device modeling [36–39] often relies on analytical expressions of optical mode distribution in the waveguide and can be too complex and cumbersome for link-level analysis. To overcome these issues, we model the silicon photonic modulators based on a simple yet accurate compact model for phase shifters. The study focuses on depletion-mode pn-junction-based phase shifters, as they are widely used for high-speed modulators on different silicon photonics platforms [2,21–25,27,40]. This compact model incorporates waveguide geometry, mode confinement factor, and PN junction doping, all with some reasonable approximations. The compact model fits well with experimental results in various silicon photonics platforms.

As shown in Fig. 1, the co-optimization engine uses both technology and link constraints. The technology constraints are related to the photonic processes and includes parameters for waveguides, junctions, couplers and lasers. The link constraints are determined by the overall link budget and specific transceiver circuits. The engine optimizes microring and Mach-Zehnder transmitters separately based on the same phase shifter model with the goal of minimizing total E/b for laser and electronic driver combined. An optical simulation toolbox is developed in Simulink to verify the large-signal transient time-domain performance of the co-optimized transmitters. The optimizer is implemented in Matlab and can be integrated seamlessly with Simulink. Although our study focuses on the transmitter side, the simulation toolbox can be applied to full optical links as well along with other communication toolboxes. This Simulink electronic-photonic co-design simulation toolbox has been released online [41].

## 3.2 PN-Junction-Based Optical Phase Shifter

## 3.2.1 Compact model of optical phase shifter

The common building block for both MRM's and MZM's is the high-speed optical phase shifter. More specifically, this phase shift allows the constructive or destructive interference

Figure 3.1: The flowchart of the co-optimization framework for silicon photonics transmitters. The denotations here are used in derivations in the study.

of light exiting the transmit waveguide, thereby creating a modulated output optical signal.

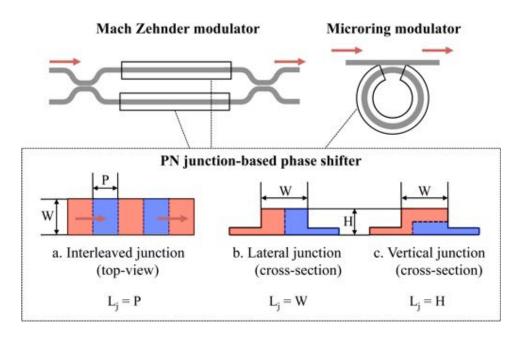

Due to the lack of Pockels effect, silicon photonics phase shifters rely on the carrier plasma dispersion effect [42]. High-speed phase modulation is achieved with depletion-mode PN junctions. Within PN junctions, the number of excess electrons and holes strongly dictate the refractive index and absorption coefficient. Combined with the applied voltage across the junction, these factors affect the maximum phase shift as well as the loss. Device parameters for phase shifters include intrinsic index and absorption, junction geometries and doping concentrations. The foundries often provide a wide range of doping concentrations by default and can potentially tune the doping levels for customers. Therefore, doping level

Figure 3.2: Mach-Zehnder and microring modulators based on different PN junction phase shifters. Three common types of phase shifters are listed with top view or cross-section view. The corresponding feature lengths  $(L_i)$  for these PN junctions are listed as well.

is considered a key parameter in our optimization framework. There are three main types of junction designs as shown in Fig. 3.2. In this section, we propose a simplified phase shifter model that is applicable to most junction shapes.

The carrier plasma dispersion effect in crystalline silicon was first shown in [42]. The wavelength-dependent expressions for the material properties were commonly used with fitting parameters. According to the models in [3], both index and absorption vary as wavelength  $\lambda$  (m). The changes in refractive index  $n(\lambda)$  and absorption  $\alpha(\lambda)$  are given by:

$$\Delta n(\lambda) = -A\lambda^2 \Delta N - B\lambda^2 \Delta P^{0.8} \tag{3.1}$$

$$\Delta\alpha(\lambda) = C\lambda^2 \Delta N + D\lambda^2 \Delta P \text{ (cm}^{-1}), \tag{3.2}$$

where  $\Delta N$  and  $\Delta P$  are changes in electron and hole concentrations (cm<sup>-3</sup>). The fitting parameters are  $A=3.64\times 10^{-10}$ ,  $B=3.51\times 10^{-6}$ ,  $C=3.52\times 10^{-6}$  and  $D=2.4\times 10^{-6}$ . Throughout the study, power absorption coefficient is denoted by  $\alpha$ , and field absorption coefficient is denoted by  $\alpha_f$ , where  $\alpha=2\alpha_f$ . The effective refractive index and absorption coefficient for an intrinsic silicon waveguide are denoted by  $n_{\rm eff,i}$  and  $\alpha_i$  respectively. The impacts of junction doping and external bias voltages can be derived in two steps. As the first step, a doped silicon waveguide without depletion region is assumed. For simplicity, the waveguide is assumed to be split evenly between uniform n-doping and uniform p-doping. The intermediate effective index  $n_{\rm eff,d}$  and absorption  $\alpha_d$  for a doped waveguide can be thereby approximated as

$$n_{\text{eff},d} \approx n_{\text{eff},i} - \gamma (A\lambda^2 N_D + B\lambda^2 N_A^{0.8})/2 \tag{3.3}$$

$$\alpha_d \approx \alpha_i + \gamma (C\lambda^2 N_D + D\lambda^2 N_A)/2.$$

(3.4)

where  $N_D$  and  $N_A$  are impurity densities for n-doping and p-doping respectively.  $\gamma$  represents the mode confinement factor for the waveguide (0< $\gamma$ <1). When optical mode is more confined in the waveguide,  $\gamma$  increases and thus doping has a larger impact on optical properties.

In reality, depletion region always exists in the PN junction of a depletion-mode phase shifter. As the second step, we assume that bias voltage V is applied on the junction (V=0 when there is no external bias). The voltage-dependent effective refractive index and absorption coefficient are derived as

$$n_{\text{eff}}(V) \approx n_{\text{eff},d} + \frac{\gamma}{L_i} \left( A \lambda^2 N_D x_n(V) + B \lambda^2 N_A^{0.8} x_p(V) \right)$$

(3.5)

$$\alpha(V) \approx \alpha_d - \frac{\gamma}{L_j} \left( C \lambda^2 N_D x_n(V) + D \lambda^2 N_A x_p(V) \right)$$

(3.6)

where  $x_n(V)$  and  $x_p(V)$  are depletion widths on the n-doping and p-doping side of the PN junction. They are calculated by the set of equations below:

$$x_n(V) = \sqrt{\frac{2\epsilon N_A(V_{bi} - V)}{qN_D(N_A + N_D)}}$$

(3.7)

$$x_p(V) = \sqrt{\frac{2\epsilon N_D(V_{bi} - V)}{qN_A(N_A + N_D)}}$$

(3.8)

$$V_{bi} = \frac{k_B T}{q} ln \frac{N_A N_D}{n_i^2}.$$

(3.9)

$L_j$  is defined as a feature length for PN junction. It is determined by the waveguide geometries and junction shapes. For different junction shapes, different feature lengths  $L_j$  are listed in Fig. 3.2. Intuitively, reducing  $L_j$  would improve phase modulation efficiency as the depletion region takes up a larger portion within the waveguide. For lateral and vertical junctions, feature length  $L_j$  are correlated with the confinement factor  $\gamma$ . For interleaved junctions, they are independent parameters. In general, reducing  $L_j/\gamma$  improves the overlap between the confined optical mode and depletion region and thereby improves phase modulation efficiency (Eq. 3.5).