# Electro-Mechanical Devices for Ultra-Low-Power Electronics

Chuang Qian

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2017-21 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-21.html

May 1, 2017

## Copyright © 2017, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Electro-Mechanical Devices for Ultra-Low-Power Electronics

By

#### Chuang Qian

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Junqiao Wu Professor Elad Alon

## Electro-Mechanical Devices for Ultra-Low-Power Electronics

Copyright © 2016

by

Chuang Qian

#### **Abstract**

Electro-Mechanical Devices for Ultra-Low-Power Electronics

by

Chuang Qian

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

The proliferation of mobile electronic devices and the emergence of the Internet of Things (IoT) have brought energy consumption to the fore of challenges for future information processing devices. Digital logic integrated circuits (ICs) implemented with complementary metal-oxide-semiconductor (CMOS) transistors have a fundamental lower limit in energy efficiency because transistors are imperfect electronic switches, having non-zero OFF-state current ( $I_{OFF}$ ) and finite sub-threshold slope. In contrast, electro-mechanical switches (relays) can achieve zero  $I_{OFF}$  and perfectly abrupt switching characteristics; therefore, they have attracted growing interest for ultra-low-power computing applications. A challenge for electro-mechanical relay technology is to reduce operation voltage and improve energy efficiency.

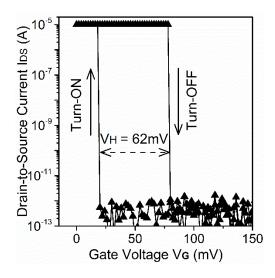

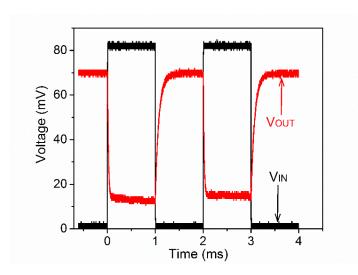

This dissertation addresses this challenge through relay design optimization for operation with an applied body bias voltage. The effects of body biasing on relay characteristics are systematically investigated by analytical modeling, simulation, and experiments. It is found that body biasing is an effective way to reduce the relay operation voltage, improve the energy-delay tradeoff, and ease fabrication challenges. By designing a logic relay to have relatively large structural stiffness and to operate in non-pull-in mode, less than 70 mV hysteresis voltage is experimentally demonstrated. A relay-based inverter circuit is demonstrated to operate reliably with a supply voltage below 100 mV, representing a significant milestone toward ultra-low-power mechanical computing.

This dissertation also includes an initial investigation of a more compact mechanical switch design for non-volatile memory application. The mechanical switch potentially can be used as a selector device in a cross-point memory cell array architecture, due to its zero off-state leakage current and non-linear current-vs.-voltage characteristics. Preliminary experimental results are shown and remaining challenges are discussed.

To my family,

for their unbounded love and unwavering support

## Table of Contents

| Chapter 1 Introduction                                                                | 1  |

|---------------------------------------------------------------------------------------|----|

| 1.1 Integrated Circuits: A Historical Perspective                                     | 1  |

| 1.2 Energy-Efficient Computing for IoT                                                |    |

| 1.2.1 CMOS Energy Efficiency Limit                                                    |    |

| 1.2.2 Zero-Leakage Switches for Digital Computing                                     |    |

| 1.3 Memory Requirements for IoT                                                       |    |

| 1.3.1 Traditional Memory Hierarchy                                                    |    |

| 1.3.2 Emerging Storage Class Memory                                                   |    |

| 1.3.3 Memory Cell Selection Device                                                    |    |

| 1.4 Dissertation Objectives and Overview                                              | 12 |

| 1.5 References                                                                        | 14 |

| Chapter 2 Operation Voltage and Energy Analysis of Micro-Electro-<br>Mechanical Relay | 17 |

| 2.1 Introduction                                                                      | 17 |

| 2.2 Relay Operation Modes: PI and NPI                                                 |    |

| 2.3 Energy and Voltage Scaling Analysis                                               |    |

| 2.3.1 NPI Mode Relay                                                                  |    |

| 2.3.2 PI Mode Relay                                                                   |    |

| 2.3.3 Challenges                                                                      |    |

| 2.4 Body-Biased Relay Operation and Analysis                                          | 23 |

| 2.4.1 Introduction to Body-Biased Relay Operation                                     | 23 |

| 2.4.2 Scaling Analysis of Operating Voltage and Energy of Body-Biased Relay .         | 24 |

| 2.5 Comparison of Minimum Voltage and Energy of Different Relay Designs.              | 26 |

| 2.6 Summary                                                                           | 28 |

| 2.7 References                                                                        | 29 |

| Chapter 3 Body-Biased Micro-Electro-Mechanical Relay                                  | 30 |

| 3.1 Introduction                                                                      | 30 |

| 3.2 Structure and Operation of 6-Terminal Relay                                       | 30 |

| 3.3 Characterization of 6-T Relay Performance                                         | 32 |

| 3.3.1 Quasi-Static <i>I-V</i> Characteristics                                         | 32 |

| 3.3.2 Dynamic Characteristics                                                         |    |

| 3.4 Effects of Body Biasing on Relay Characteristics                                  | 35 |

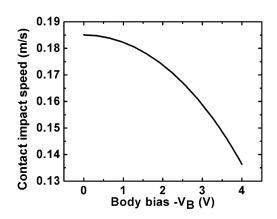

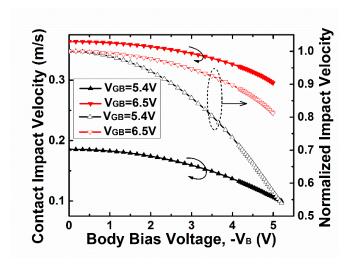

| 3.4.1 Contact Impact Velocity                                                         |    |

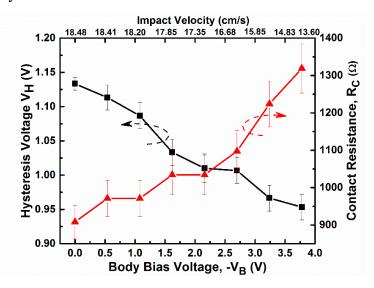

| 3.4.2 Effects of Body Biasing on $V_{\rm H}$ and $R_{\rm C}$                          | 37 |

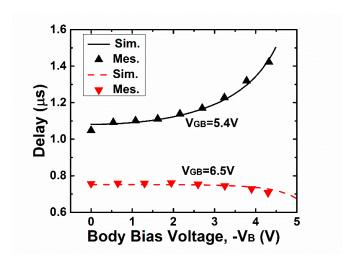

| 3.4.3 Effect of Body Biasing on $\tau_{\text{ON}}$                                    |    |

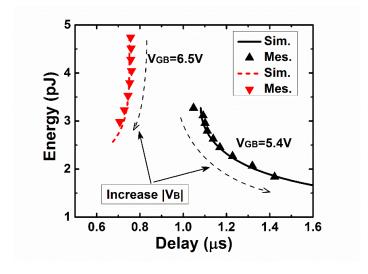

| 3.4.4 Energy-Delay Trade-Off for Body-Biased Relay                                    | 39 |

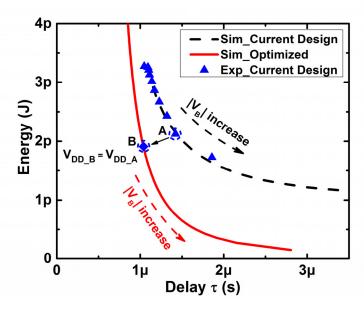

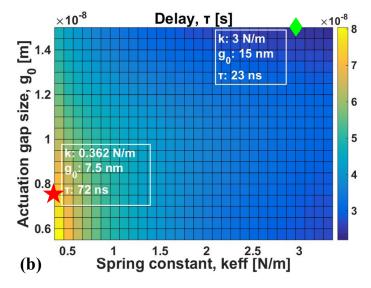

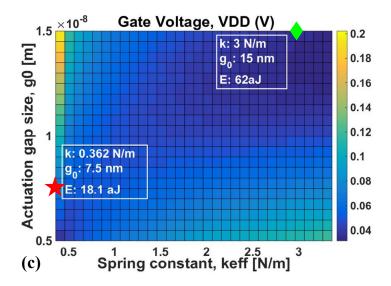

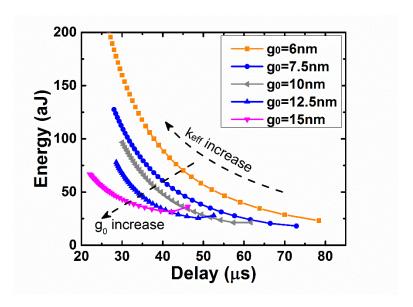

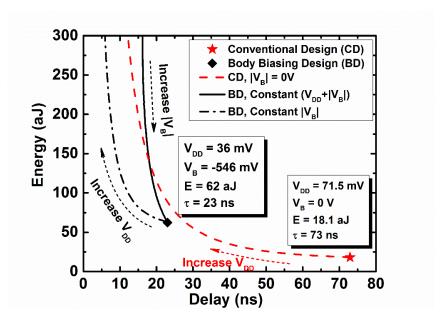

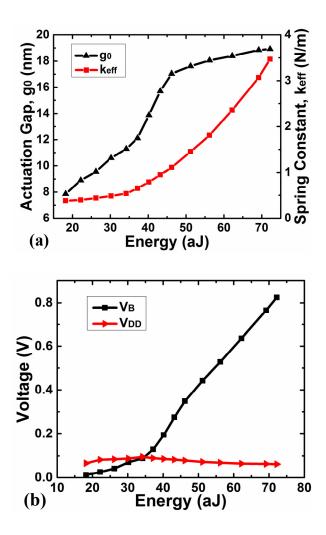

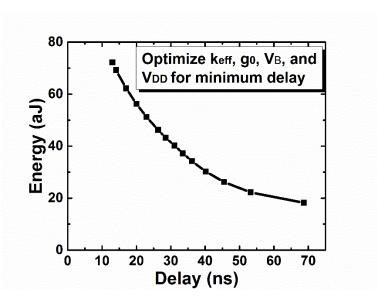

| 3.5 Energy-Delay Performance Optimization of NEM Relay | 41 |

|--------------------------------------------------------|----|

| 3.5.1 Parameters to Optimize                           | 41 |

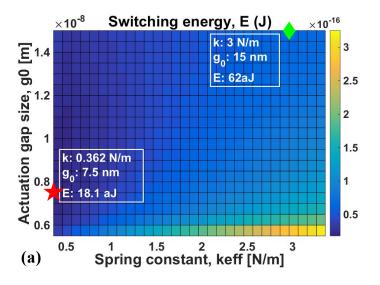

| 3.5.2 Minimization of $V_{\rm DD}$                     | 42 |

| 3.5.3 Minimization of Energy and Delay                 | 45 |

| 3.6 Summary                                            | 48 |

| 3.7 References                                         | 49 |

| Chapter 4 Millivolt Relay Technology                   | 50 |

| 4.1 Introduction                                       |    |

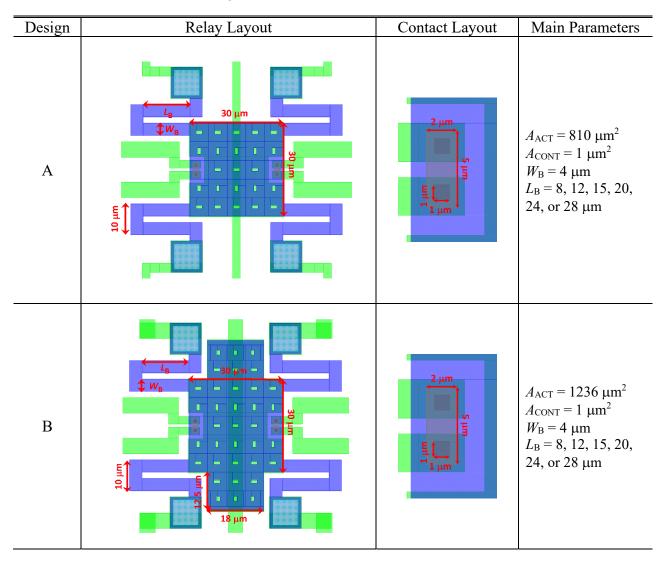

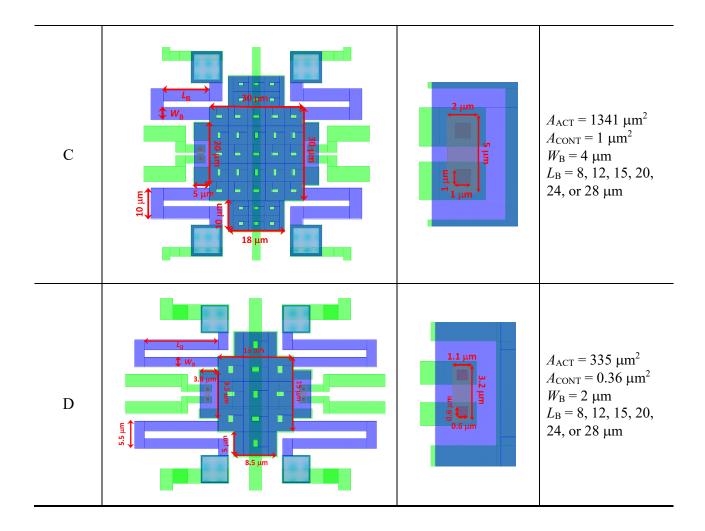

| 4.2 Millivolt Relay Design                             |    |

| 4.2.1 Relay Structure                                  |    |

| 4.2.2 Key Design Parameters                            |    |

| 4.3 Simulation                                         |    |

| 4.3.1 Process Emulation                                |    |

| 4.3.2 Device Simulation                                |    |

| 4.4 Relay Fabrication Process                          |    |

| 4.5 Relay Performance Characterization                 |    |

| 4.5.1 Switching Voltages                               |    |

| 4.5.2 <i>I-V</i> Characteristics                       |    |

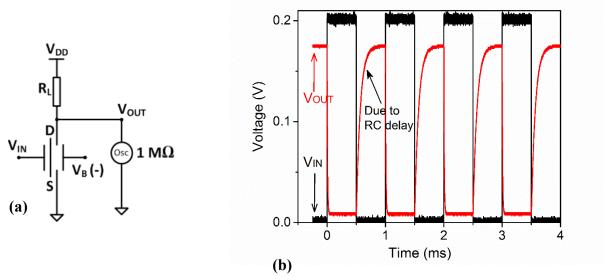

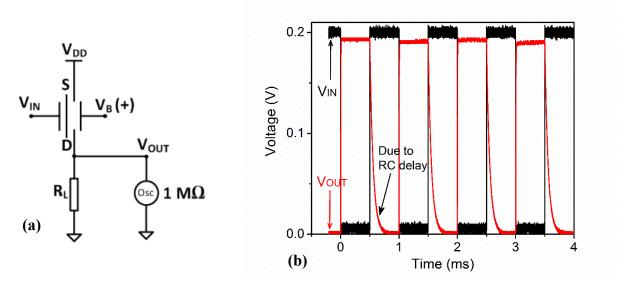

| 4.5.3 Millivolt Inverter Demonstration                 |    |

| 4.5.4 Mechanical Switching Delay                       |    |

| 4.5.4 Variability                                      |    |

| 4.6 Summary                                            | 76 |

| 4.7 References                                         |    |

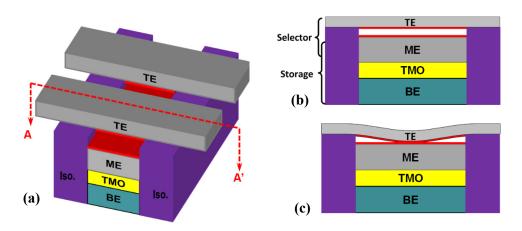

| Chapter 5 NEM Selector for Cross-point Memory          | 79 |

|                                                        |    |

| 5.1 Introduction                                       |    |

| 5.2 Proposal of NEM Selector                           |    |

| 5.3 Experimental Investigation of NEM Selector         |    |

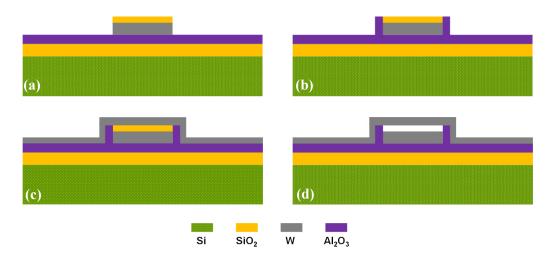

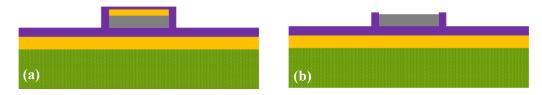

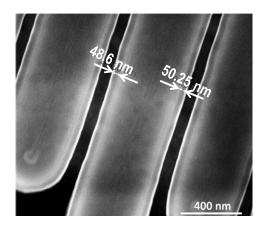

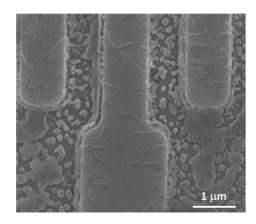

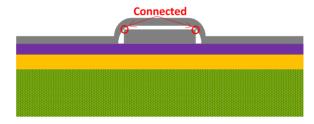

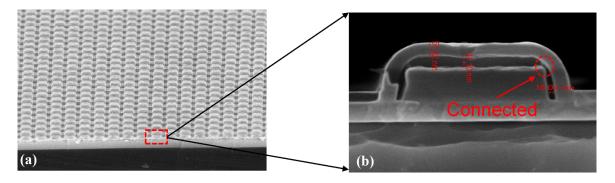

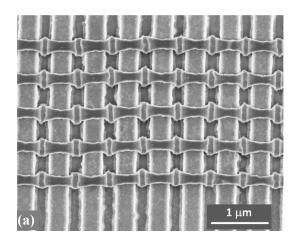

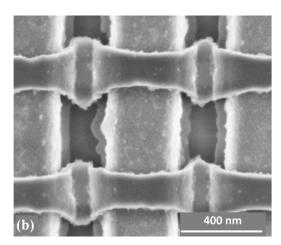

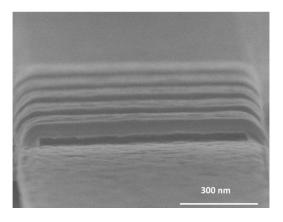

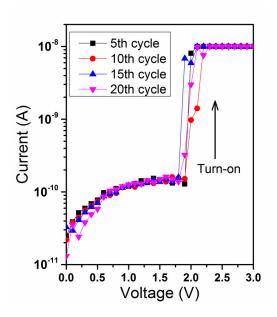

| 5.3.1 Device Fabrication                               |    |

| 5.3.2 Electrical Characterization                      |    |

| 5.4 Challenges for Selector Miniaturization            |    |

| 5.4.1 Stuck-ON Failure                                 |    |

|                                                        |    |

| 5.5 Actively-Reset NEM Selector Design                 |    |

| 5.6 Summary                                            |    |

| 5.7 References                                         | 93 |

| Chapter 6 Conclusion                                   | 96 |

| 6.1 Summary and Contributions of This Work             | 06 |

| 6.2 Suggestions for Future Work | 97 |

|---------------------------------|----|

| 6.3 Reference                   | 99 |

### **Acknowledgements**

First and foremost, my utmost gratitude goes to my research advisor, Professor Tsu-Jae King Liu, for her cordiality and generousness of offering me the research opportunity in her group at the darkest time of my Ph.D. journey. Life was never easy for me, especially at the beginning of the adventure. It was her kindness, patience, encouragement, and confidence on me that got me through the hard time. Her depth and breadth of knowledge, insightful vision, and wisdom have not only guided me through my Ph.D. research, but also shaped what I have achieved in this dissertation. Her dedication, professionalism, and leadership also set a great example from which I can learn and benefit in my future career.

I would like to thank Professor Junqiao Wu for graciously serving in both my qualifying exam and dissertation committee, as well as fruitful collaboration in the NEM relay project. I would like to thank Professor Elad Alon for serving in my dissertation committee. I'm grateful to him and his student Dr. Matthew Spencer for valuable discussion on NEMory project. Working with Professor Alon as a GSI (graduate student instructor) and teaching undergraduate students is also a delightful and rewarding experience. I also thank Professor Vivek Subramanian and Professor Ali Javey for serving in my qualifying exam committee. They are excellent lecturers. Both of their courses, the Solid State Devices and the Microfabrication Technology, laid a solid foundation for my Ph.D. research. I would like to thank Professor Vladimir Marko Stojanovic and Professor Eli Yablonovitch for their guidance and valuable discussions on the relay project.

I'm grateful to Professor Albert Pisano for being my academic advisor in the first year of my time at Berkeley. His thoughtfulness and willingness to offer help opened another door for a youngster.

My appreciation also goes to industrial friends. I would like to thank Dr. Jianhua (Joshua) Yang and Dr. Zhiyong Li from HP Lab for offering me an internship opportunity in HP Lab where I worked closely with them and gained valuable experience about cross-point memory as well as selector devices. I also thank Lief O'Donnell and Steve Nishimoto from Broadcom Corporation. Both of them mentored me through my internship at Broadcom Corp. and taught me practical experience about custom circuit design.

I'm indebted to many colleagues in King Group. Special thanks go to Dr. Yenhao Philip Chen, Dr. WookHyun Kwon, Dr. I-Ru Chen, Dr. Jack Yaung, and Dr. Louis Hutin. Being more senior to me, they trained me on how to use equipment in Marvell Nanofabrication Lab and Device Characterization Lab, and passed on their invaluable project experience to me. Without their help, I couldn't have been able to ramp up to full speed that quickly. I also owe my special gratitude to Dr. Nuo Xu for helping me prepare for Ph.D. prelim examination and sharing many insightful thoughts. His enthusiasm in research, diligent attitude, and depth and breadth of knowledge exemplify an outstanding Ph.D. researcher.

I would like to thank Dr. Alexis Peschot and Dr. Daniel Connelly for their close collaboration on relay project which leads to fruitful results. I would also like to thank other team members of the NEM project with whom I worked with: Jun Fujiki, Dr. Kimihiko Kato, Dr. Bivas Saha, Dr.

Sergio F. Almeida (UTEP), Farnaz Niroui (MIT), Benjamin Osoba, Urmita Sikder, Zhixin Alice Ye, and Miles Rusch.

I am sincerely grateful to those fine minds of King Group, Nguyen's Group, and "residents" of Cory 373 and NanoLab. Numerous times on weekends andr at midnight, having you as companions in the office or lab makes me feel life brighter. I would like to thank especially Dr. Sangwan Kim, Dr. Nattapol Damrongplasit, Dr. Eungseok Park, Ruolan Liu, Jalal Naghsh Nilchi, Xi (Robin) Zhang, Dr. Sangyoon Han, Yang Yang, Dr. Jie Zou, Dr. Shiqian Shao, Kevin Chen, Dr. Yuping Zeng, Hanyu Zhu, Dr. Thura Lin Naing, Dr. Turker Beyazoglu, Dr. Henry Barrow, Dr. Robert Schneider, Dr. Yang Lin, Dr. Wei-Chang Li, Dr. Lingqi Wu, Yiting Wu, Fei Ding, Alper Ozgurluk, Yongjun Li, and Yafei Li. Thank you all!

The fabrication of M/NEM devices used in this research would not have been possible without the effort and help of staff members of the UC Berkeley Marvell Nanofabrication Laboratory. I thanks especially Dr. William Flounders, Dr. Jeffrey Clarkson, Joseph Donnelly, Sia Parsa, Ryan Rivers, Kim Chan, Richelieu Hemphill, Marilyn Kushner, David Lo, Jay Morford, Jason Chukes, and Rosemary Spivey.

Last but not least, I owe the deepest debt of gratitude to my family for their unbounded love and unselfish support. Those miseries my parents suffered for me will be buried in my heart forever. I could never thank my wife enough for her sacrifice. Her smile is always delightful...

## **Chapter 1**

#### Introduction

#### 1.1 Integrated Circuits: A Historical Perspective

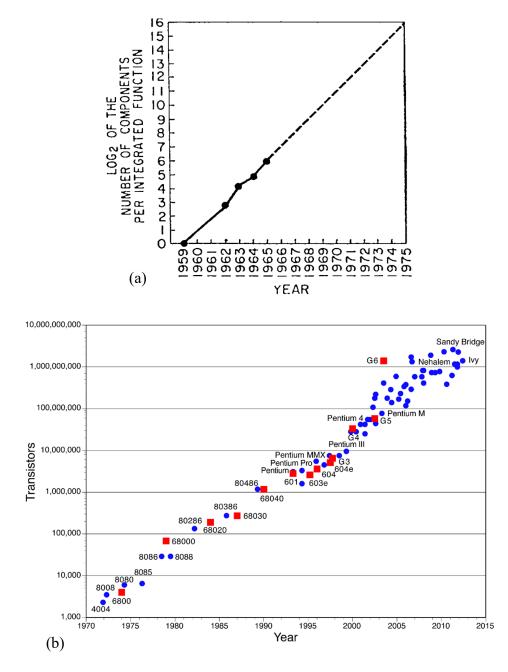

The invention of the transistor by John Bardeen, Walter Brattain, and William Shockley in 1947 revolutionized the field of electronics. Soon after that, bulky and power-hungry vacuum tubes, which were the basic building blocks for electronic circuits throughout the first half of the twentieth century, were replaced by solid-state semiconductor transistors in virtually all electronic circuits. About ten years later in 1958, Jack Kilby at Texas Instruments demonstrated the world-first working integrated circuit (IC), which revolutionized the semiconductor industry. Ever since then, the number of transistors on a single chip as well as its computing capability have increased exponentially. In 1965, Gordon Moore, the co-founder of Intel Corporation, made an observation that the number of transistors on a single chip doubled about every year (later on this was adjusted to every 18 months, and then to two years), and predicted that this exponential growth would continue (Fig. 1.1(a)) [1]. The prediction proved to be accurate and became known as Moore's Law [1]. For the past five decades, the semiconductor industry has marched to the pace of Moore's Law (Fig. 1.1(b)). The first commercially available general-purpose microprocessor Intel 4004 released in 1971 had only 2300 transistors and maximum clock frequency of 740 kHz. Today's high-end microprocessor for mission-critical computing, the Intel Haswell-EX Xeon E7-8890V3 processor released in 2015, has a total of 18 cores comprising up to 5.6 billion transistors within a die size of 662 mm<sup>2</sup> and operates at frequency up to 3.3 GHz [2]. Such a tremendous improvement in device density and computing ability could not have been realized without transistor miniaturization from a minimum feature size of 10 µm in the Intel 4004 microprocessor down to 22 nm in the Intel Xeon E7-8890V3 processor. Transistor scaling provides not only for faster switching speed but also for smaller footprint such that more

transistors can be crammed onto a single chip, leading to more functionality per chip and reduced cost per function [3].

**Fig. 1.1.** (a) Moore's original prediction of increasing number of transistors per chip in 1965 (reprinted from [1]); (b) The historical trend of number of transistors per chip (reprinted from [4]).

The ever-increasing functionality and decreasing cost per function of ICs led to the boom of electronic devices. Numerous new electronic devices and applications emerged in the last decade, such as the smartphone, tablet computer, smart watch, augmented-reality glasses, and all kinds of

wearable devices and sensors, just to name a few. Meanwhile, the great achievements of the semiconductor industry built a solid foundation for internet and telecommunication technology. High demand for mobile connectivity and information accessibility boosted the rapid progress and world-wide adoption of internet and wireless communication technologies which enabled an unprecedented level of global connectivity and ubiquitous access to information. These, together, are giving rise to the Internet of Things (IoT)!

The IoT promises a future where any aspect of society ranging from humans to objects – any thing that one can think of – are connected to and by the internet [5]. This is made possible by embedding "Things" with electronic devices, sensors, actuators, and network connectivity that enable them to collect, process, and exchange data. Fig. 1.2 is a vision of the future information infrastructure [6] which consists of a large number of huge data and computer centers, billions of personal computing devices, and potentially trillions of sensors and actuators. Realization of this vision calls for overcoming many technological challenges, among which one of the most critical is to achieve ultra-low-power electronics, for both digital computing and massive data storage.

Fig. 1.2. Information infrastructure of IoT era (reproduced from [6]).

#### 1.2 Energy-Efficient Computing for IoT

#### 1.2.1 CMOS Energy Efficiency Limit

Energy efficiency is one of the most critical figures of merit of integrated circuits (ICs). For power-outlet connected high performance computing devices, limitations of heat dissipation technology set the upper limit of power that an IC chip can consume without overheating itself, and thus the computation throughput of the chip for a given energy efficiency (*i.e.* energy per operation). For battery-powered electronics, since the total amount of available energy is limited, energy efficiency essentially determines the battery lifetime. In either case, low energy per operation is beneficial. Unfortunately, digital logic ICs implemented with complementary metal-

oxide-semiconductor (CMOS) transistors have a fundamental lower limit in energy per operation because transistors are imperfect electronic switches.

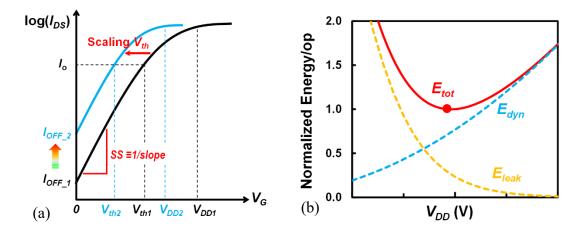

Fig. 1.3(a) illustrates typical current-vs-voltage (I-V) characteristics of a n-channel metal-oxide-semiconductor field-effect transistor (MOSFET), where the drain-to-source current  $I_{DS}$  is plotted on a logarithmic scale while the gate voltage  $V_{GS}$  is plotted on a linear scale. In the subthreshold region ( $V_{GS} < V_{th}$ ), the subthreshold swing SS is defined as

$$SS \equiv \frac{1}{slope} = ln(10) \frac{kT}{q} \left( 1 + \frac{C_{dep}}{C_{ox}} \right), \tag{1.1}$$

where k is the Boltzmann constant, T is the absolute temperature, q is the electronic charge,  $C_{\rm dep}$  is the depletion region capacitance, and  $C_{\rm ox}$  is the gate-to-channel capacitance.  $\frac{kT}{q}$  is called the thermal voltage and has a value of 26 mV at room temperature (300 K). The factor  $\left(1 + \frac{C_{\rm dep}}{C_{\rm ox}}\right)$  comes from a voltage-divider effect of the serial capacitances  $C_{\rm dep}$  and  $C_{\rm ox}$ . Ideally,  $C_{\rm ox}$  is much larger than  $C_{\rm dep}$ , so that this factor is close to the minimum value of 1. Therefore,  $SS > 60 \ mV/dec$  at room temperature. The transistor's off-state leakage current  $I_{\rm OFF}$ , i.e. the current  $I_{\rm DS}$  when  $V_{\rm GS} = 0$  V and  $V_{\rm DS}$  is equal to the power-supply voltage  $V_{\rm DD}$ , is given by

$$I_{OFF} = I_o 10^{-\frac{V_{th}}{SS}},\tag{1.2}$$

where  $I_0$  is the current at  $V_{GS} = V_{th}$ .

The total energy consumed per clock cycle  $E_{\text{tot}}$  of a CMOS logic circuit comprises two parts, the dynamic energy  $E_{\text{dyn}}$  which dissipates during charging and discharging of capacitors, and the static energy  $E_{\text{leak}}$  which is due to transistor off-state leakage current  $I_{\text{leak}}$ :

$$E_{tot} = E_{dyn} + E_{leak}, (1.3)$$

where

$$E_{dyn} = C_{eff} V_{DD}^2, (1.4)$$

$$E_{leak} = I_{OFF} V_{DD} L_d t_{delay}, (1.5)$$

and  $C_{\text{eff}}$  is the total effective capacitance along the signal-propagating path,  $L_{\text{d}}$  is the logic depth, and  $t_{\text{delay}}$  is the average propagation delay per logic stage. Further,  $t_{\text{delay}}$  can be written as

$$t_{delay} = \frac{C_g V_{DD}}{2I_{eff}},\tag{1.6}$$

where  $C_g$  is the output capacitance of the logic gate and  $I_{eff}$  is the effective transistor drive current which can be simply approximated as its on-state current  $I_{ON}$  (i.e. the  $I_{DS}$  at  $V_{GS} = V_{DS} = V_{DD}$ ).

**Fig. 1.3.** (a) Illustration of the switching *I-V* characteristics of an n-channel MOSFET; (b) dynamic, static, and total energy consumption of a CMOS-based digital logic circuit. The lower limit for CMOS energy efficiency exists due to MOSFET OFF-state leakage (reproduced from [7]).

From Eq. (1.4) one can see that decreasing  $V_{\rm DD}$  reduces  $E_{\rm dyn}$  quadratically; however, this decreases the drive current  $I_{\rm eff}$  (Fig. 1.3(a) black curve) and thus increases the delay  $t_{\rm delay}$  (Eq. (1.6)), which in turn increases the leakage energy consumption (Eq. (1.5)). In order to maintain the same  $I_{\rm eff}$ , the gate over-drive voltage ( $V_{\rm DD}$  -  $V_{\rm th}$ ) has to be kept the same, which requires  $V_{\rm th}$  to decrease (Fig. 1.3(a) blue curve). However, a linear decrease in  $V_{\rm th}$  results in an exponential increase of leakage current  $I_{\rm OFF}$  (Eq. (1.2)), so that  $E_{\rm leak}$  increases. Therefore, there is a trade-off between  $E_{\rm dyn}$  and  $E_{\rm leak}$ . This energy-voltage relation is depicted in Fig. 1.3(b). As one can see, there is a lower limit in energy per operation for CMOS technology.

It should be noted that the CMOS energy efficiency limit exists due to the inherent switching mechanism of the MOSFET (*i.e.* thermionic emission of carriers from the source region into the channel region) which inevitably leads to non-zero  $I_{OFF}$  and non-zero SS. This poses two challenges for CMOS technology, described below.

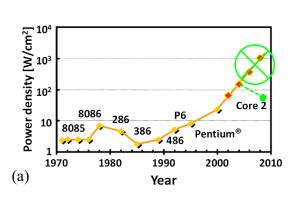

On one hand, when transistor switching speeds became ever-faster and transistor density kept improving at the pace of Moore's Law, chip power density quickly increased to an impractical level such that either the circuit operating frequency or transistor density had to level off to ensure that chips operated within practical thermal dissipation limits. Fig. 1.4(a) shows the historical trend of exponential increase in chip power density. Clearly the exponential growth was not sustainable, as it would have led to unreasonably high power density resulting in heat that could not be dissipated quickly enough using conventional chip-cooling technology. Parallelism was adopted beginning in the middle of the last decade as an alternative means for increasing the computational throughput of a chip. (The operation frequency stopped increasing and even dropped to lower power density.) Multiple processor "cores" were used to parallelize computing to keep improving overall throughput, shown in Fig. 1.4(b). However, parallelism is only a temporary fix: once the minimum energy/operation point (cf. Fig. 1.3(b)) is reached, lowering the operation frequency will not decrease the power density any further.

**Fig. 1.4.** (a) Historical trend of microprocessor chip power density (reproduced from [8]); (b) Parallelism is used to recoup chip performance with each core operating at lower frequency (reproduced from [9]).

On the other hand, since there exists a lower limit in energy per operation for any CMOS technology, there also exists an upper limit in the amount of total logic computation that can be performed with a given amount of energy for any CMOS circuit. This presents a fundamental challenge for battery-powered electronic devices. For example, many mobile devices, including smartphones, smart watches, and many other wearable devices, require frequent re-charging. The latest Apple Watch Series 2 can only operate up to 18 hours in a limited-usage case [10]. For other electronic devices such as distributed sensors whose energy is supplied from an embedded battery or is scavenged from environment, their functionality and/or lifetime depends largely on the energy efficiency of the underlying circuits.

Therefore, overcoming the fundamental limit of CMOS energy efficiency has become essential.

#### 1.2.2 Zero-Leakage Switches for Digital Computing

To break the CMOS energy efficiency limit, new electronic switching devices which ideally can achieve abrupt switching characteristics and no off-state leakage current are of interest. An electro-mechanical relay is such a switch. It works by making/breaking mechanical contact between two conductive electrodes such that it has zero  $I_{\rm OFF}$  and abrupt switching characteristics. Unlike the MOSFET, it doesn't rely on energy barrier modulation as the switching mechanism. So in principle an electro-mechanical relay can be made to operate at much lower voltage than CMOS transistors and hence more energy efficiently [11,12]. Therefore, there has been a resurgence of interest in mechanical computing in recent years [13-21].

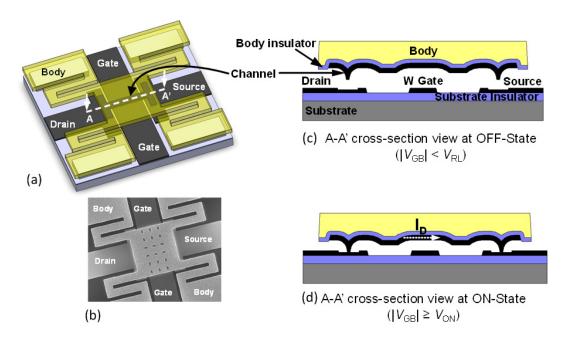

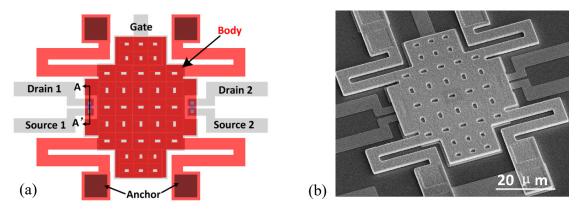

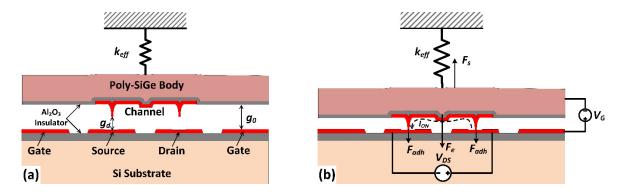

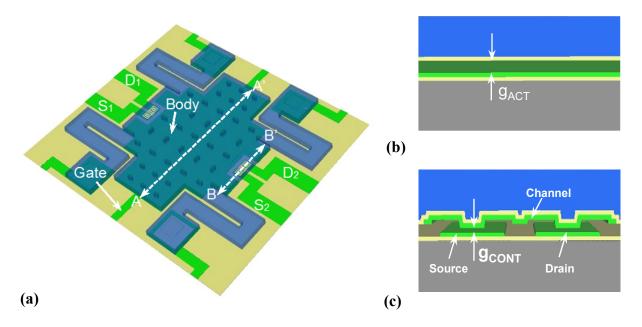

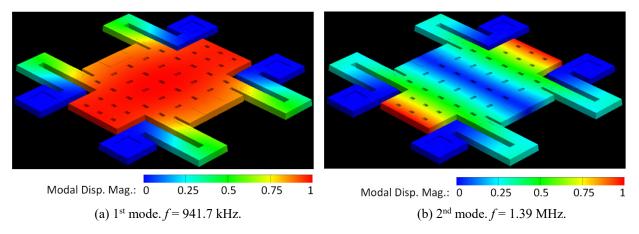

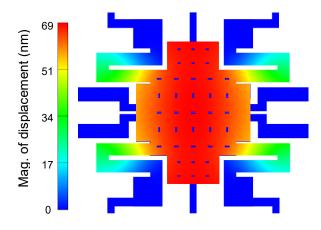

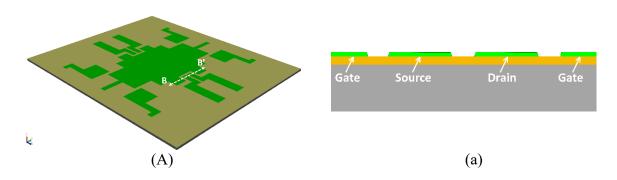

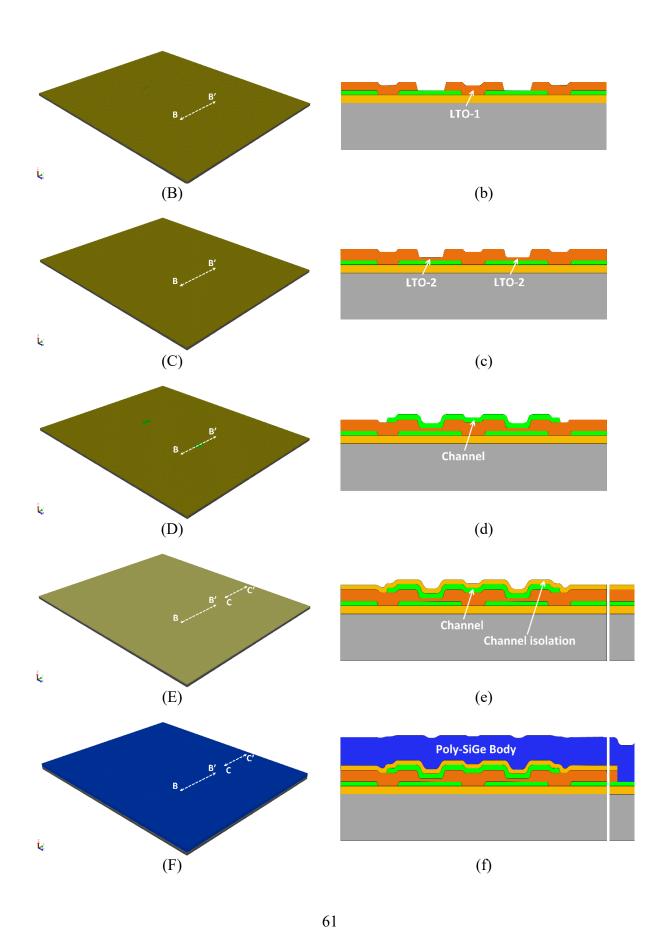

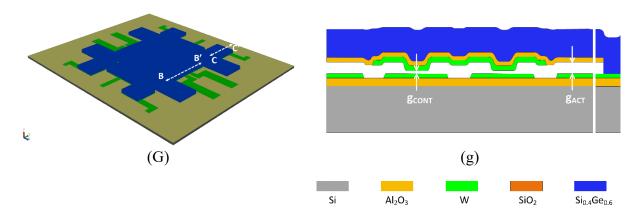

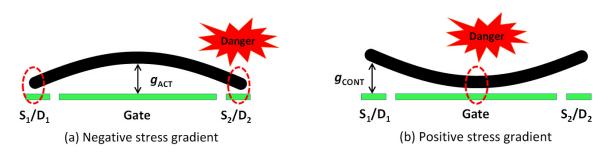

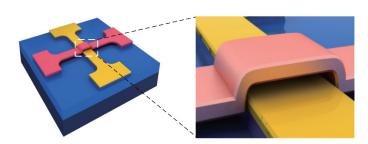

**Fig. 1.5.** Structure of a typical 4-terminal (4-T) logic relay: (a) 3-D structure of 4-T relay; (b) SEM image of a fabricated 4-T relay; (c) Cross-section view along cut-line AA' of the 4-T relay at OFF state; and (d) Cross-section view along cut-line AA' of the 4-T relay at ON state.

Fig. 1.5(a) illustrates a 3-dimensional (3-D) structure of a surface-micromachined 4-terminal (4-T) micro-electro-mechanical (MEM) logic relay comprising one Drain electrode, one Source electrode, one Gate electrode, and one Body electrode. A scanning-electron-microscopy (SEM) image of a fabricated relay is shown in Fig. 1.5(b). The cross-section views along cut-line AA' at the OFF and ON states are shown in Fig. 1.5 (c) and (d) respectively. The movable Body (yellow part in Fig. 1.5) electrode is suspended by 4 folded-flexure beams that are each anchored to the substrate. The Gate, Source, and Drain electrodes are co-planar and made of tungsten (Fig. 1.5(c)). Another narrow strip of tungsten is attached to the underside of the Body via an intermediary insulation layer, and functions as a bridge (referred to as the Channel hereafter) between the Source and Drain electrodes in the ON state. In the OFF state (Fig. 1.5(c)), the Channel is out of contact with the Source and Drain so that no current can flow. When a gate-tobody voltage  $V_{\rm GB}$  is applied, the electrostatic force  $F_{\rm elec}$  between the Gate and Body plates actuates the Body downward while the spring restoring force  $F_{\text{spring}}$  of the four deformed suspension beams counteracts this movement, such that a position of balanced forces is reached. If the magnitude of  $V_{\rm GB}$  is larger than a certain value (called turn-on voltage  $V_{\rm ON}$ ),  $F_{\rm elec}$  becomes sufficient to cause the Channel to make physical contact with the Source/Drain electrodes so that a current ( $I_{DS}$ ) suddenly can flow between the Source and Drain (Fig. 1.5(d)). When  $V_{GB}$  is reduced below a certain voltage (called the release voltage,  $V_{\rm RL}$ ) such that  $F_{\rm spring} > F_{\rm elec} + F_{\rm adh}$ , contact between the Channel and the Source/Drain electrodes is broken and I<sub>DS</sub> drops to zero suddenly.  $F_{adh}$  is the adhesive force between the Channel in the dimpled contact regions and the Source/Drain electrodes. Due to the existence of  $F_{\text{adh}}$  in the ON state,  $V_{\text{ON}}$  is always larger than  $V_{\rm RL}$ .

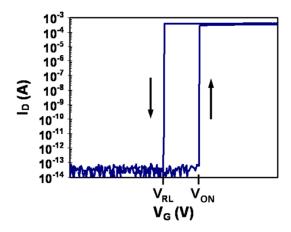

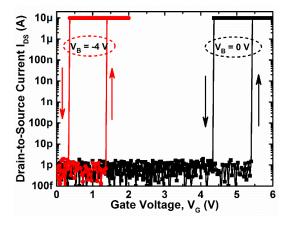

A typical current-vs.-voltage ( $I_D$ - $V_G$ ) characteristic of a 4-T relay is shown in Fig. 1.6. As one can see, the relay can switch on/off abruptly, with virtually 0 mV/dev local subthreshold swing

and zero leakage current (noise level in Fig. 1.6). This is beyond the capability of a MOSFET.

**Fig. 1.6.** A typical measured *I-V* characteristic of a 4-T relay. Reproduced from [9].

#### 1.3 Memory Requirements for IoT

Never has data been created at a faster pace than today [22]. Pervasive electronic devices and ubiquitous connectivity expedite the creation of ever-larger amounts of data. The explosive growth of generation and processing of "big data" in this IoT era calls for a massive data storage medium which ideally should have non-volatility, low power consumption, low latency, high endurance, and most importantly, high storage density at low cost per bit.

#### 1.3.1 Traditional Memory Hierarchy

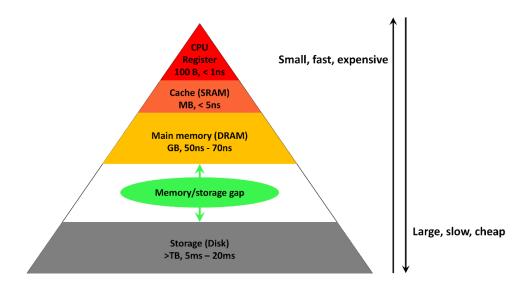

Fig.1.7 shows the hierarchy of different types of memory devices used in conventional computer systems. From the top to the bottom of the pyramid, there are registers, static random access memory (SRAM), dynamic random access memory (DRAM), and hard-disk drive (HDD). Going down the hierarchy, lower levels of memory have larger storage capacity and lower price per byte, but longer access time. The CPU (central processing unit) registers are very fast and can keep up with the speed of other parts of the CPU (e.g. the arithmetic logic unit); however, they are very expensive (consist of many transistors per bit) and thus have very limited storage capacity. For example, a multiplexer-based master-slave D-type flip-flop has more than 20 transistors. The main memory is usually DRAM which has much larger capacity (e.g. several gigabytes for a modern laptop computer), but unfortunately longer access time (e.g. tens of nanoseconds). To bridge the CPU/main memory speed gap, several levels of cache memory (typically made of SRAM) are used to temporarily store copies of data from frequently used main memory locations so as to reduce the average CPU waiting time for accessing data. SRAM is much faster than DRAM at the tradeoff of higher cost – typically a SRAM cell consists of six transistors while a DRAM cell comprises only one transistor and one capacitor. Both SRAM and DRAM cells are volatile, meaning that the stored data will be lost once power to the chip is shut off. For long-term storage the hard-disk drive (HDD) has been the predominant type of secondary storage device, for more than five decades. The advantages of a HDD are its nonvolatility, high storage capacity, and low cost per bit; its main disadvantage is its slow datatransfer rate, for both read and write operation.

Fig. 1.7. Memory hierarchy in computer systems.

#### 1.3.2 Emerging Storage Class Memory

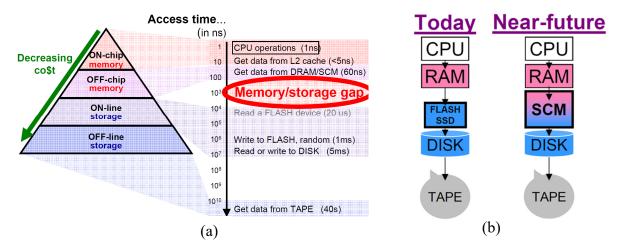

Sustaining growth in computing performance has become more and more challenging [23]. From a data-processing point of view, the performance gap (in terms of latency) between memory and CPU, which is already more than five orders of magnitude, continues to widen. For data-centric applications where huge amounts of data are frequently required by the CPU, data access time limits computational throughput [23]. In addition, from a data-storage point of view, the explosive growth of "big data" requires increasing capacity at lower price per bit. The energy consumption, space usage, and cost of memory systems with the DRAM-HDD-based memory hierarchy in Fig. 1.7 are major obstacles to the development of exascale computer systems capable of 10<sup>18</sup> operations per second [23].

Recently, NAND flash solid-state drive (SSD) has emerged as an alternative to HDD as the secondary storage device in computer systems, thanks to its faster data-accessing speed (~20 µs for read and ~1 ms for write), lower power consumption, smaller form factor, and continual reduction in price per bit. Although this partially mitigates the challenges that computer memory systems are facing today, the memory-storage performance gap remains significant (Fig. 1.8(a)). Since flash memory stores information by injecting (erasing) electrons to (from) a charge-storage layer through an electrically insulating dielectric material within a MOSFET, limited write endurance inherently is one of its main limitations. Other limitations include modest retention time (typically 10 years for a new device, but only 1 year at the end of rated endurance lifetime), long erase time (~ms), high operation voltage (~15 V), and sophisticated peripheral circuits [24]. With the miniaturization of memory cell size for improving bit density (thus decreasing cost per bit), the already-poor endurance of NAND flash devices worsens. This has driven the evolution to vertical integration (3-D stacking) of flash memory cells rather than further cell miniaturization to increase storage capacity.

**Fig. 1.8.** (a) Classic memory hierarchy. After introducing flash memory, memory-storage gap narrows but remains significant. (b) Comparison of memory hierarchies of today and the near-future. In the near future, flash SSD and HDD may coexist. The performance gap between main memory and storage memory will be bridged by SCM. (Reprinted from [25].)

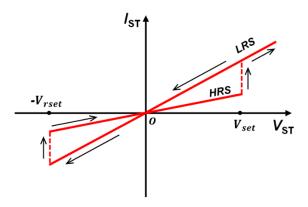

The challenges of today's memory hierarchy present opportunities for new memory technologies. A new class of memory devices, called storage class memory (SCM), is proposed to bridge the memory-storage gap as well as to address many of the other challenges mentioned above [24,25]. There are a variety of emerging SCM technologies, such as phase-change memory (PCM), magnetoresistive random-access memory (MRAM), spin-transfer-torque RAM (STT-RAM), resistive RAM (ReRAM), etc. All of these memory devices store information by means of different resistance states of a "storage element" (e.g., low resistance state represents "1", and high resistance state represents "0"). But the mechanisms for switching between the high/low resistance states are different, which then result in distinct characteristics for each of these SCM devices. In the near future, it is anticipated that some of these emerging SCM devices may bridge the memory-storage gap between main memory and disk (Fig. 1.8(b)). In the long term, it is also possible that one of these SCM devices may even replace both SSD and HDD, becoming so-called universal memory devices.

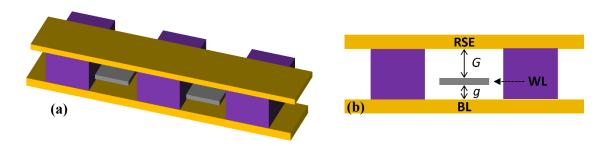

#### 1.3.3 Memory Cell Selection Device

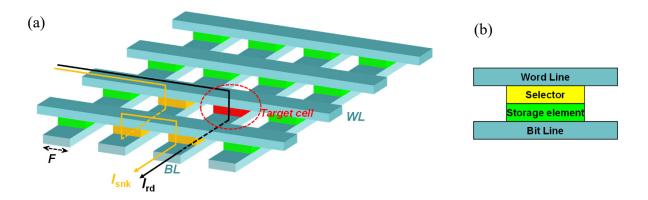

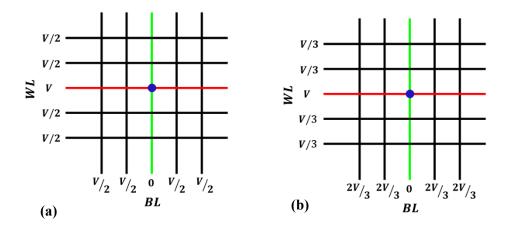

High storage density and low cost are two critical requirements of emerging SCM devices for massive data storage. In a typical memory system, memory cells are organized into arrays (rows and columns of cells) for high storage density and hence lower cost per bit. In a planar configuration, the cross-point array architecture (Fig. 1.9(a)) achieves the highest storage density, since each cell occupies only  $4F^2$  area where F is the minimum half-pitch. Each storage element is sandwiched between a word line (WL) and a bit line (BL) at their crossing. Due to its potential for high storage density, cross-point memory architecture has attracted tremendous research interest in recent years [26-29].

Fig. 1.9. (a) 2-dimensional cross-point memory array architecture; (b) Cross-sectional view of a 1S1R cross-point memory cell.

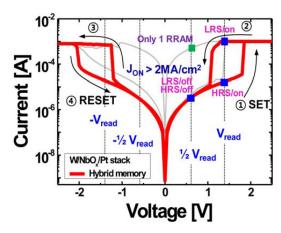

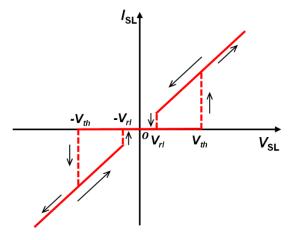

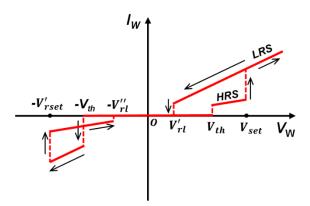

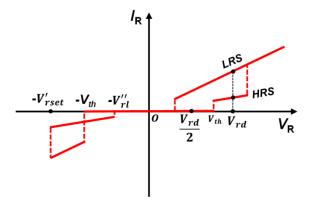

In addition to the information storage element, each cross-point memory cell should have a built-in selector device. Otherwise, there can be significant "sneak" current passing through unaddressed memory cells, degrading both read and write operation margins and increasing overall power consumption, which in turn limits the maximum possible array size [28,29]. Fig. 1.9(a) illustrates an example of a sneak current path through unaddressed (yellow) cells in the low-resistance state. The read current  $I_{rd}$  through the addressed (red) cell in the high-resistance state is sensed by peripheral circuitry. However, the sneak current  $I_{snk}$  affects the reading process by adding to the sensed current which can lead to a reading error ("1" state instead of "0" state). To mitigate this issue, nonlinearity in the I-V characteristics of the memory cells is required, such that  $I_{snk}$  is greatly reduced so that  $I_{rd}$  is much larger than  $I_{snk}$ . This nonlinearity can be achieved either by having a non-linear storage element, or by adding a selector device in series with the storage element in each memory cell forming a 1-selector-1-resistor (1S1R) structure as shown in Fig. 1.9(b). Fig. 1.10 shows a comparison of I-V characteristics of ReRAM cells with vs. without a selector device [30]. Clearly, with the selector device the leakage current at  $\frac{1}{2}V_{read}$  is greatly reduced.

**Fig. 1.10.** Comparison of *I-V* characteristics of ReRAM memory cell with (thin gray curves) *vs.* without (bold red curves) selector device. Reprinted from [30].

In the 1S1R case, characteristics of the selector device are essential to the overall performance

of the cross-point memory array. An ideal selector device should have the following characteristics [31]: (a) OFF-state leakage current should be as low as possible so as to increase read/write margin and to prevent aggregate sneak path current from dominating overall system power budget; (b) high ON-state current density so that the selector can deliver high enough current within very small area for programming the storage element; (c) bidirectional operation so that it is compatible with bidirectional-current storage elements such STT-RAM and bipolar ReRAM devices; (d) process compatibility with 3-D integration. Other characteristics, such as switching speed, cycling endurance, and variability, should be preferably as good as the storage element so that the selector device doesn't limit the overall 1S1R memory cell performance. These requirements are very challenging to meet with a single device. In fact, many devices have been proposed as candidates for cross-point memory selectors, such as MOSFET, BJT, PN junction diode, oxide diodes [32-36], ovonic threshold switching (OTS) devices [37-41], metalinsulator transition (MIT) devices [42,43], oxide tunnel barrier devices [44,45], and mixed-ionic-electronic-conduction (MIEC) devices [46-48]. Each has pros and cons [31]. Interested readers are referred to the cited references for more details.

Electro-mechanical switches have virtually zero OFF-state leakage current and high ON-state current. They are also bidirectional and fully compatible with back-end-of-line (BEOL) 3-D integration. Therefore, it is natural to propose to use nano-electro-mechanical (NEM) switches as cross-point memory selectors.

#### 1.4 Dissertation Objectives and Overview

This dissertation aims to advance micro/nano electro-mechanical (M/NEM) switch technology for both energy-efficient logic and memory applications. A large part of the research work focuses on reducing the operating voltage (to below 100 mV) and thereby improving the switching energy efficiency of a logic relay. The other part is devoted to prototyping a NEM selector device suitable for 3-D cross-point memory arrays. The remainder of this dissertation is organized as follows.

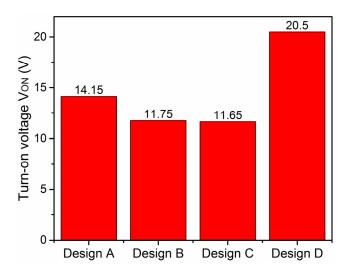

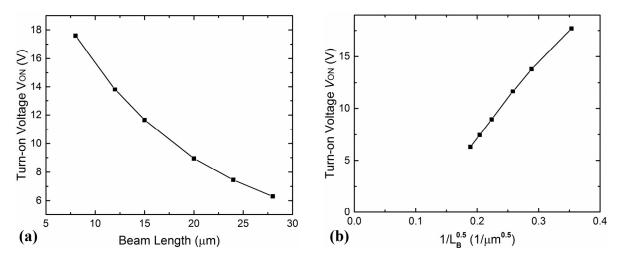

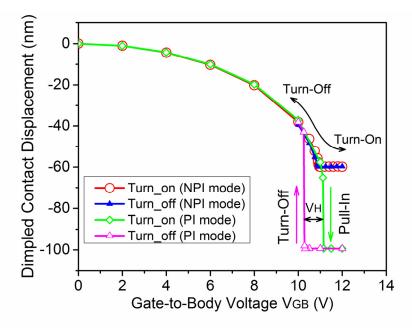

Chapter 2 first reviews pull-in (PI) and non-pull-in (NPI) operation modes of M/NEM switches. The scaling limit of voltage and energy for each of these modes are discussed, and challenges for conventional relay design are elucidated. Body biasing is then proposed to mitigate these challenges, followed by an analysis of the operating voltage and switching energy of a body-biased relay. The results indicate that a body-biased relay should be designed to operate at the boundary of PI and NPI modes to minimize operating voltage if the structural stiffness is relatively large.

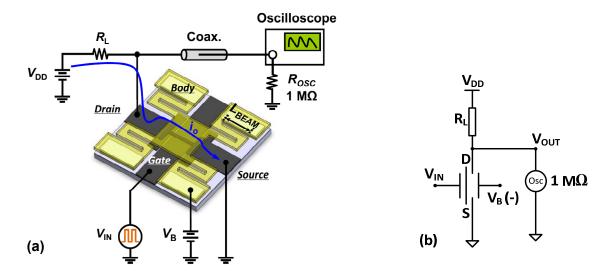

Chapter 3 presents the quasi-static and dynamic performance of a fabricated 6-T relay. Effects of body biasing on relay characteristics are experimentally investigated, leading to the discovery of the energy-delay tradeoff for body-biased relays. A methodology for optimizing this trade-off is developed.

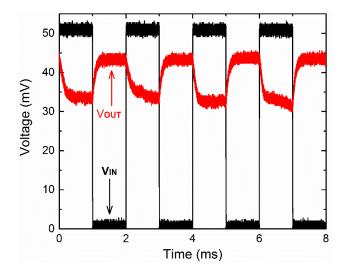

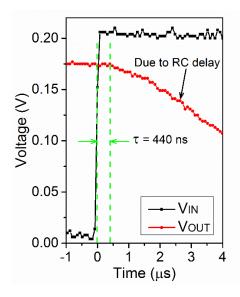

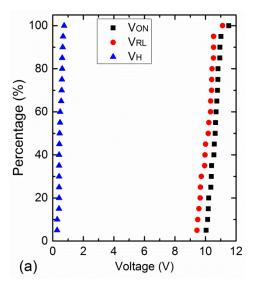

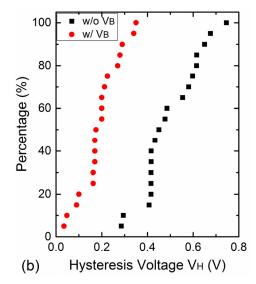

Chapter 4 covers the design, simulation, fabrication, and characterization of millivolt body-biased relays. Sub-100 mV operation of an electrostatically actuated relay is achieved. A relay-based inverter circuit is demonstrated to operate reliably with a supply voltage as low as 50 mV, representing a significant milestone toward ultra-low-power mechanical computing.

Chapter 5 proposes the application of NEM switch as a selector device for 3-D cross-point memory. A NEM selector is prototyped and preliminary results are shown. Remaining challenges are outlined, and their possible remedies are discussed.

Chapter 6 summarizes the key findings and contributions of this dissertation. Suggestions for future work are also offered.

#### 1.5 References

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 8, pp.114-117, Apr. 1965.

- [2] http://ark.intel.com/

- [3] R. H. Dennard, F. H. Gaensslen, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *Journal of Solid-State Circuits*, vol. 9, pp. 256-268, 1974.

- [4] http://www.assured-systems.com/news/article/moores-law--soon-to-be-no-more/

- [5] International technology roadmap for semiconductor 2.0: Executive report, 2015.

- [6] J. M. Rabaey, "A brand new wireless day," 13th Asia and South Pacific Design Automation Conference, Seoul, Korea, 2008.

- [7] I.R. Chen, "Novel material integration for reliable and energy-efficient NEM relay technology," Ph.D dissertation, UC Berkeley, 2014.

- [8] S. Borkar, Intel Corp.

- [9] R. Nathanael, "Nano-Electro-Mechanical (NEM) relay devices and technology for ultralow energy digital integrated circuits," Ph.D dissertation, UC Berkeley, 2012.

- [10] http://www.apple.com/watch/battery.html

- [11] O. Y. Loh, and D. Espinosa, "Nanoelectromechanical contact switches," *Nature Nanotech.*, vol. 7, pp. 283-296, 2012.

- [12] V. Pott, *et al.* "Mechanical computing redux: relays for integrated circuit applications," *Proc. IEEE 98*, pp. 2076-2094, 2010.

- [13] T.-H. Lee, S. Bhunia, and M. Mehregany, "Electromechanical computing at 500°C with silicon carbide," *Science*, vol. 329, no. 5997, pp. 1316-1318, Sep. 2010.

- [14] J. O. Lee, Y.-H. Song, M.-W. Kim, M.-H. Kang, J.-S. Oh, H.-H. Yangm and J.-B. Yoon, "A sub-1-volt nanoelectromechanical switching device," *Nature Nanotech.*, vol. 8, pp. 36-40, Jan. 2013.

- [15] J. E. Jang, et al. "Nanoscale memory cell based on a nanoelectromechanical switched capacitor," *Nature Nanotech.*, vol. 3, pp. 26-30, 2008.

- [16] S. W. Lee, S. J. Park, E. E. B. Campbell, and Y. W. Park, "A fast and low-power microelectromechanical system-based non-volatile memory device," *Nature Commun.*, vol. 2, pp. 1-6, 2011.

- [17] N. Sinha, T. S. Jones, Z. Guo, and G. Piazza, "Demonstration of low voltage and functionally complete logic operations using body-biased complementary and ultra-thin ALN piezoelectric mechanical switches," *Proc. 23rd IEEE Conf. MEMS*, 2010, pp. 751-754.

- [18] M. Spencer, *et al.* "Demonstration of integrated micro-electro-mechanical relay circuits for VLSI applications," *IEEE J. Solid-State Circuits*, vol. 46, pp. 146-148, 2011.

- [19] R. Venkatasubramanian, S. K. Manohar, and P. T. Balsara, "NEM relay-based sequential logic circuits for low-power design," *IEEE Trans. Nanotech.*, vol. 12, pp. 386-398, 2013.

- [20] N. Sinha, T. S. Jones, Z. Guo, and G. Piazza, "Body-biased complementary logic implemented using AlN piezoelectric MEMS switches," *IEEE J. MEMS*, vol. 21, pp. 484-496, 2012.

- [21] R. Nathanael, V. Pott, H. Kam, J. Jeon, and T.-J. K. Liu, "4-terminal relay technology for complementary logic," *IEEE IEDM Tech. Digest*, 2009, pp. 223-226.

- [22] R. L. Villars, C. W. Olofson, and M. Eastwood, "Big data: what it is and why you should care," A White Paper from www.idc.com, Jun. 2011.

- [23] R. F. Freitas, W. W. Wilcke, "Storage-class memory: the next storage system technology," *IBM J. RES. & DEV.*, vol. 52, pp. 439-447, 2008.

- [24] International technology roadmap for semiconductors 2.0: Beyond CMOS, 2015.

- [25] IBM Almaden Research Center, "Storage class memory: towards a disruptively low-cost solid-state non-volatile memory," 2013.

- [26] M.-J. Lee et al., "A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub> /TaO<sub>2-x</sub> bilayer structures," *Nature Mater.*, vol. 10, no. 8, pp. 625-630, Aug. 2011.

- [27] S.-G. Park, et al., "A non-linear ReRAM cell with sub-1µA ultralow operating current for high density vertical resistive memory," *IEEE Int. Electron Devices Meeting Tech. Dig.*, 2012, pp. 501-504.

- [28] S. Kim, J. Zhou, W. D. Lu, "Crossbar RRAM arrays: selector device requirements during write operation," *IEEE Trans. Electron Devices*, vol. 61, pp. 2820-2826, 2014.

- [29] J. Zhou, K.-H. Kim, W. Lu, "Crossbar RRAM arrays: selector device requirements during read operation," *IEEE Trans. Electron Devices*, vol. 61, pp. 1369-1376, 2014.

- [30] S. Kim, et al. "Ultrathin (<10nm) Nb<sub>2</sub>O<sub>5</sub>/NbO<sub>2</sub> hybrid memory with both memory and selector characteristics for high density 3D vertically stackable RRAM applications," *IEEE Symposium on VLSI Technology*, 2012, pp. 155-156.

- [31] G. W. Burr, R. S. Shenoy, K. Virwani, P. Narayanan, A. Padilla, and B. Kurdi, "Access devices for 3D crosspoint memory," *J. Vac. Sci. Technol. B*, vol. 32, pp. 040802, 2014.

- [32] M. J. Lee, Y. Park, D. S. Suh, E. H. Lee, S. Seo, D.-C. Kim, R. Jung, B.-S Kang, S.-E. Ahn, C. B. Lee, D. H. Seo, Y.-K. Cha, I.-K. Yoo, J.-S. Kim, B. H. Park, "Two series oxide resistors applicable to high speed and high density nonvolatile memory," *Adv. Mater.*, vol. 19, no. 22, pp. 3919-3923, 2007.

- [33] S.-E. Ahn, B. S. Kang, K. H. Kim, M.-J. Lee, C. B. Lee, G. Stefanovich, C. J. Kim, and Y. Park, "Stackable all-oxide-based nonvolatile memory with Al<sub>2</sub>O<sub>3</sub> antifuse and p-CuO<sub>x</sub>/n-InZnO<sub>x</sub> diode," *IEEE Electron Dev. Lett.*, vol. 30, pp. 550-552, 2009.

- [34] G. Tallarida, N. Huby, B. Kutrzeba-Kotowska, S. Spiga, M. Arcari, G. Csaba, P. Lugli, A. Redaelli, and R. Bez, "Low temperature rectifying junctions for crossbar non-volatile memory devices," *Proceeding of International Memory Workshop*, IMW'09, 2009.

- [35] J.-J. Huang, C.-W. Kuo, W.-C. Chang, and T.-H. Hou, "Transition of stable rectification to resistive-switching in Ti/TiO<sub>2</sub>/PtTi/TiO<sub>2</sub>/Pt oxide diode," *Appl. Phys. Lett.*, vol. 96, 262901 (2010).

- [36] W. Y. Park, G. H. Kim, J. Y. Seok, K. M. Kim, S. J. Song, M. H. Lee, and C. S. Hwang, "A Pt/TiO<sub>2</sub>/Ti Schottky-type selection diode for alleviating the sneak current in resistance switching memory arrays," *Nanotechnology*, vol. 21, no. 19, pp.195201.1-4, 2010.

- [37] S. R. Ovshinsky, "Reversible electrical switching phenomena in disordered structures," *Phys. Rev. Lett.*, vol. 21, no. 20, pp. 1450-1453, 1968.

- [38] D. Adler, M. S. Shur, M. Silver, and S. R. Ovshinsky, "Threshold switching in chalcogenide-lass thin films," *J. Appl. Phys.*, vol. 51, no. 6, pp.3289-3309, 1980.

- [39] M. Anbarasu, M. Wimmer, G. Bruns, M. Salinga, and M. Wuttig, "Nanosecond threshold switching of GeTe<sub>6</sub> cells and their potential as selector devices," *Appl. Phys. Lett.*, vol. 100, pp. 143505.1-4, 2012.

- [40] D. C. Kau, et al., "A stackable cross point phase change memory," *IEEE Int. Electron Devices Meeting Tech. Dig.*, 2009, pp. 617-620.

- [41] M.-J. Lee, *et al.*, "Highly-scalable threshold switching select device based on chaclogenide glasses for 3D nanoscaled memory arrays," *IEEE Int. Electron Devices Meeting Tech. Dig.*, 2012, pp. 33-35.

- [42] M. Imada, A. Fujimori, and Y. Tokura, "Metal-insulator transitions," *Rev. Mod. Phys.*, vol. 70, no. 4, pp. 1039-1263, 1998.

- [43] M. Son, *et al.*, "Excellent selector characteristics of nanoscale VO<sub>2</sub> for high-density bipolar ReRAM applications," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1579-1581, 2011.

- [44] A. Kawahara, et al., "An 8 Mb multi-layered cross-point ReRAM macro with 443 MB/s write throughput," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 178-185, 2013.

- [45] J. Shin, *et al.*, "TiO<sub>2</sub>-based metal-insulator-metal selection device for bipolar resistive random access memory cross-point application," *J. Appl. Phys.*, vol. 109, pp. 033712.1-4, 2011.

- [46] R. S. Shenoy, *et al.*, "Endurance and scaling trends of novel access-devices for multi-layer crosspoint-memory based on mixed-ionic-electronic-conduction (MIEC) materials," *Symp. VLSI Technol.*, 2011, pp. 94-95.

- [47] K. Virwani, et al., "Sub-30nm scaling and high-speed operation of fully-confined Access-Devices for 3D crosspoint memory based on Mixed-Ionic-Electronic-Conduction (MIEC) materials," *IEEE Int. Electron Devices Meeting Tech. Dig.*, 2012.

- [48] G. W. Burr, *et al.*, "Recovery dynamics and fast (sub-50ns) read operation with Access devices for 3D crosspoint memory based on Mixed-Ionic-Electronic-Conduction (MIEC)," *Symp. VLSI Technol.*, 2013, pp. 66-67.

## Chapter 2

## **Operation Voltage and Energy Analysis of Micro-Electro-Mechanical Relay**

#### 2.1 Introduction

CMOS technology is fundamentally limited in energy efficiency due to non-zero transistor OFF-state leakage current ( $I_{OFF}$ ) [1,2]. That is, the energy required to perform a digital logic operation cannot be decreased to be infinitesimally small, due to a trade-off between dynamic energy consumption and static energy consumption. For ultra-low-power applications, such as distributed sensor networks and Internet of Things, micro-electro-mechanical (MEM) relay technology is potentially superior to CMOS because mechanical switches have zero  $I_{OFF}$  and abrupt switching behavior which in principle enable ultra-low operating voltage [3]. Thus, relays as logic switches have been developed and intensively investigated [4-8]. However, hindering the IC application of MEM relays is their relatively high operating voltage [9,10].

In this chapter, two different operation modes of a MEM relay, namely the pull-in (PI) mode and non-pull-in (NPI) mode, are introduced in section 2.2. Section 2.3 presents an analysis of MEM relay switching energy and voltage for each mode, and the challenges of conventional relay design. In section 2.4, body biasing is introduced as a method to mitigate these challenges, followed by a scaling analysis of switching energy and voltage of a body-biased relay. Section 2.5 compares these different designs. Section 2.6 summarizes this chapter.

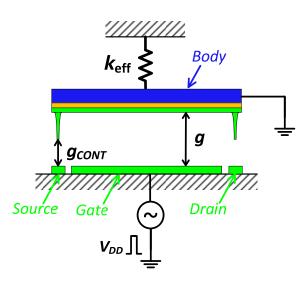

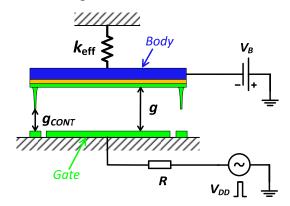

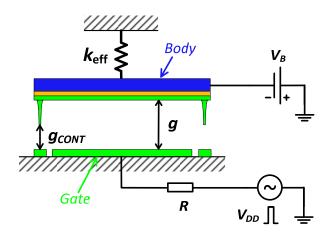

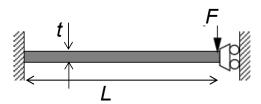

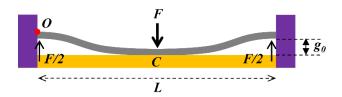

#### 2.2 Relay Operation Modes: PI and NPI

For simplification, an electrostatically-actuated MEM relay can be modeled as a parallel-plate capacitor, as shown in Fig. 2.1. The top plate (Body) is electrically grounded, and mechanically suspended by a spring with effective spring constant  $k_{eff}$ . The bottom plate (Gate) is electrically driven by a voltage source (square wave with magnitude of  $V_{DD}$ ).  $g_{CONT}$  and  $g_{CONT}$  are gap size and the actuation gap size, respectively. Without an applied gate voltage, the initial condition for  $g_{CONT}$  are  $g_{CONT} = g_{CONT} = g_{CON$

$$F_{spring} = k_{eff}(g_0 - g), \tag{2.1}$$

and

$$F_{elec} = \frac{\varepsilon_0 A_{ACT} V_{DD}^2}{2g^2}, \tag{2.2}$$

respectively, where  $A_{\text{ACT}}$  is the actuation area and  $\varepsilon_0$  is the vacuum permittivity. The net force on Body (whose positive displacement is defined to be downwards) is therefore

$$F_{net} = F_{elec} - F_{sping}. (2.3)$$

Fig. 2.1. Parallel-plate capacitor model of a MEM relay.

Taking a derivative over g on both sides of (2.3) results in

$$\frac{dF_{net}}{dg} = k_{eff} - \frac{\varepsilon_0 A_{ACT} V_{DD}^2}{g^3}.$$

(2.4)

Let's take a close look at (2.4): if  $k_{eff} < \frac{\varepsilon_0 A_{ACT} V_{DD}^2}{a^3}$ , i.e.

$$V_{DD} > \sqrt{\frac{k_{eff}g^3}{\varepsilon_0 A_{ACT}}},\tag{2.5}$$

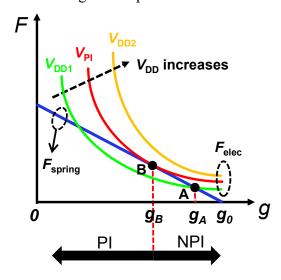

then  $dF_{net} > 0$  when Body is moving downwards (*i.e.* dg < 0). There is a positive feedback between g and  $F_{net}$ :  $F_{net}$  increases when g decreases, which then brings the Body downwards further (*i.e.* g becomes even smaller) until the Body collapses to the bottom Gate electrode (or, for the case in Fig. 2.1,  $g_{CONT}$  drops to zero, so the relay is turned on). This highly non-linear positive feedback phenomenon is called the pull-in (PI) effect, which can be better visualized in an F-vs.-g plot as shown in Fig. 2.2. The blue-solid line shows the linear dependence of  $F_{spring}$  on g. The other three curves show  $F_{elec}$ -vs.-g relation for different values of  $V_{DD}$ . A small gate voltage (e.g.,  $V_{DD1}$ ) can reduce g from  $g_0$  to  $g_A$  at which  $F_{spring} = F_{elec}(V_{DD1})$  so the system is in a balanced stable state. Since  $F_{spring}$  increases linearly while  $F_{elec}$  increases super-linearly when g decreases,  $F_{elec}$  will be always larger than  $F_{spring}$  if  $V_{DD}$  is large enough, as for the  $V_{DD2}$  curve shown in Fig. 2.4. In between these two cases, clearly there is a critical voltage  $V_{DD}$  at which the  $F_{elec}$  curve is tangent to that of  $F_{spring}$  and the system has only a metastable position B. Beyond this metastable position (i.e.  $g < g_B$ ), there exists the aforementioned positive feedback between  $F_{net}$  and g, so the system enters the PI region of operation.

**Fig. 2.2.** Illustration of the relationship between forces and actuation gap size.  $F_{\text{spring}}$  linearly depends on g, whereas  $F_{\text{elec}}$  has a super-linear dependence on g. When  $V_{\text{DD}}$  increases, the number of intersection-points between  $F_{\text{spring}}$  and  $F_{\text{elec}}$  drops from 2 to 0.

This critical value of  $V_{DD}$  is called the pull-in voltage  $V_{PI}$ . Both  $V_{PI}$  and  $g_B$  can be calculated by solving the following group of equations:

$$F_{elec} = F_{sping} \tag{2.6}$$

$$\frac{dF_{elec}}{dg} = \frac{dF_{sping}}{dg} \tag{2.7}$$

So,

$$V_{PI} = \sqrt{\frac{8k_{eff}g_0^3}{27\varepsilon_0 A_{ACT}}} \tag{2.8}$$

and

$$g_B = \frac{2g_0}{3}. (2.9)$$

To summarize, with the parallel-plate capacitor simplifying assumption, the minimum voltage  $V_{\rm DD}$  that can decrease the parallel-plate gap size g by 1/3 of its initial value ( $g_0$ ) such that the system enters into a non-linear positive-feedback region is called the pull-in voltage  $V_{\rm PI}$ . Relays working in this manner are referred to herein as PI-mode relays. However, if the as-fabricated contact gap size  $g_{\rm d}$  is smaller than 1/3 $g_0$ , the relay turns on before it enters into the PI region. Therefore, relays with  $g_{\rm d} < 1/3g_0$  are referred to herein as non-pull-in (NPI) mode relays.

Note that the above analysis is based on quasi-static analysis. If dynamic effects are taken into account,  $V_{\rm PI}$  would be smaller than the static  $V_{\rm PI}$  given by (2.8), because the inertia of the downward-moving Body would aid in exceeding the critical displacement (i.e.  $1/3g_0$ ) even if  $V_{\rm GB}$  is less than the static  $V_{\rm PI}$ . A detailed dynamic analysis [11] shows that the dynamic  $V_{\rm PI}$  is about 91.9% of the static  $V_{\rm PI}$ . Throughout this thesis,  $V_{\rm PI}$  always refers to the static pull-in voltage, unless otherwise noted.

#### 2.3 Energy and Voltage Scaling Analysis

#### 2.3.1 NPI Mode Relay

To turn on a NPI-mode relay,  $V_{\rm DD}$  should be large enough such that  $g_{\rm CONT}$  drops to 0 in a stable state (i.e.,  $F_{\rm net} = 0$ ). The turn-on voltage ( $V_{\rm on-NPI}$ ) is given by

$$V_{on-NPI} = \sqrt{\frac{2k_{eff}g_d(g_0 - g_d)^2}{\varepsilon_0 A_{ACT}}}.$$

(2.10)

To decrease  $V_{\text{on-NPI}}$ , clearly smaller  $k_{\text{eff}}$ , smaller  $g_0$ , and larger  $A_{\text{ACT}}$  are preferred. The energy supplied by the voltage source during this turn-on process is

$$E_{NPI} = QV_{DD} = C_{on}V_{on-NPI}^{2}$$

$$= \frac{\varepsilon_{0}A_{ACT}}{g_{0} - g_{d}} \frac{2k_{eff}g_{d}(g_{0} - g_{d})^{2}}{\varepsilon_{0}A_{ACT}}$$

$$= 2k_{eff}g_{d}(g_{0} - g_{d}), \qquad (2.11)$$

where Q is the total charge supplied by the voltage source, and  $C_{\rm on}$  is the capacitance of the parallel-plate capacitor in ON state. Again, decreasing  $k_{\rm eff}$  and  $g_0$  is the key to reduce energy consumption. On the other hand, to be able to turn off the relay,

$$F_{\text{spring}} > F_{\text{adh}} + F_{\text{elec}}$$

(2.12)

has to be satisfied. This puts a lower limit on  $k_{eff}g_d$ , i.e.

$$k_{eff}g_d > F_{\text{adh}}. (2.13)$$

To further reduce  $E_{\rm NPI}$ , the  $(g_0 - g_d)$  term has to be decreased. Unfortunately, both  $g_0$  and  $g_d$  have a lower limit set by fabrication process technology. Assuming  $g_d$  is fixed, one can minimize  $E_{\rm NPI}$  by minimizing  $g_0$  which has a lower limit of  $3g_d$  (because NPI mode relay requires  $g_d$

$1/3g_0$ ). Therefore,

$$E_{NPI} > 2F_{adh} * 2g_d = 4F_{adh}g_d.$$

(2.14)

(2.14) indicates the minimum energy consumption of NPI relay is fundamentally limited by contact adhesive force and contact gap size.

#### 2.3.2 PI Mode Relay

The minimum voltage required to turn on a PI relay is given by (2.8). Similarly, smaller  $k_{\text{eff}}$ , smaller  $g_0$ , and larger  $A_{\text{ACT}}$  are preferred. The energy to turn on a PI mode relay is:

$$E_{PI} = QV_{DD} = C_{on}V_{PI}^{2}$$

$$= \frac{\varepsilon_{0}A_{ACT}}{g_{0} - g_{d}} \frac{8k_{eff}g_{0}^{3}}{27\varepsilon_{0}A_{ACT}}.$$

(2.15)

Where Q is the total charge supplied by the voltage source, and  $C_{\rm on}$  is the capacitance of the parallel-plate capacitor in ON state. (2.15) has a minimum value at  $g_0 = 1.5 g_d$ , namely,

$$E_{PI} \ge E_{PI}(g_0 = 1.5g_d) = 2k_{eff}g_d^2.$$

(2.16)

Inserting (2.13) into (2.16) gives

$$E_{PI} > 2F_{adh}g_d. \tag{2.17}$$

So the minimum energy consumption of PI mode relay is  $2F_{adh}g_d$ , which can ideally be achieved when

and

$$k_{eff}g_d = F_{adh}, g_0 = 1.5g_d.$$

(2.18)

The  $V_{\rm PI}$  of the ideal minimum-energy relay is

$$V_{PI-Emin} = \sqrt{\frac{k_{eff}g_d^3}{\varepsilon_0 A_{ACT}}} = F_{adh} \sqrt{\frac{g_d}{k_{eff}\varepsilon_0 A_{ACT}}}.$$

(2.19)

#### 2.3.3 Challenges

Eqs. (2.14) and (2.17) show that the switching energies for both NPI- and PI-mode relays are limited by the contact adhesive force and contact gap size. In addition, a PI-mode relay has a smaller minimum switching energy. This explains why researchers have focused on PI-mode relay designs, making the structure as compliant as possible. However, the more compliant the structure is, the higher the possibility that the relay will fail to turn off (i.e.  $F_{\text{spring}} < F_{\text{adh}}$ ). Also, the aforementioned conditions ( $k_{eff}g_d = F_{\text{adh}} \& g_0 = 1.5g_d$ ) for achieving minimum switching energy are ideal and in practice cannot be achieved across all devices on a chip, due to process-induced variations.

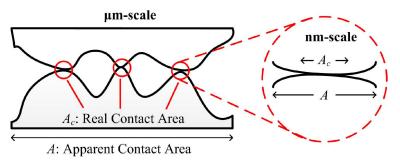

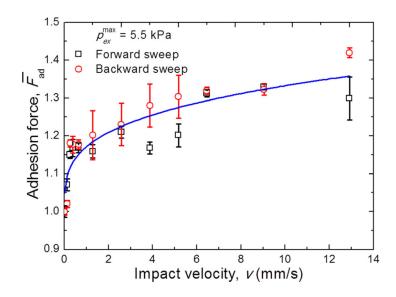

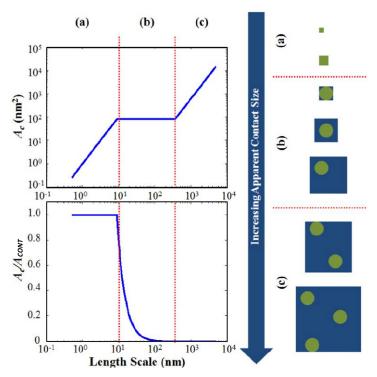

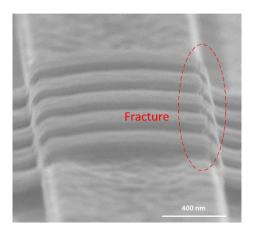

On one hand, F<sub>adh</sub> is difficult to precisely control in practice. Qualitatively, we have

$$F_{adh} = A_C * P, (2.20)$$

where  $A_{\rm C}$  is the real contact area and P is the average adhesive force per unit contact area. Fig. 2.3 shows an example of microscale contact, where the two surfaces make contact with each other only at a few asperities due to surface roughness [12].  $A_{\rm C}$  is much smaller than the apparent contact area A. Its exact value depends both on surface morphology and contact force, and thus is hard to know. Even worse,  $A_{\rm C}$  actually varies since the surface morphology changes over on/off switching cycles due to surface wear [13]. P is an average value accounting for all interface effects, possibly including metal-metal bonds, Van-der Waals forces, capillary forces, etc., and varies with contact materials and operating environment. Many factors can change P, such as surface oxidation, interface contamination, environment moisture, among many others. These render the precise control of  $F_{\rm adh}$  practically impossible.

Fig. 2.3. Schematic illustration of the contact interface. Reprinted from [12].

On the other hand, process variation is inevitable even in today's most advanced semiconductor fabrication facility. Unfortunately, the ideal condition (2.18) is so sensitive to process variation that any decrease in  $g_d$  or  $k_{eff}$  may lead to as-fabricated stuck-ON failure of relays designed with the ideal parameter values. Obviously, this is not acceptable for practical application of relays.

Clearly, to avoid stuck-ON failures despite process-induced variations,  $k_{eff}g_d$  must be increased. However, this would increase the turn-on voltage  $V_{on}$  and hence the switching energy. How can we solve this dilemma? This is where body-biasing comes into play.

#### 2.4 Body-Biased Relay Operation and Analysis

#### 2.4.1 Introduction to Body-Biased Relay Operation

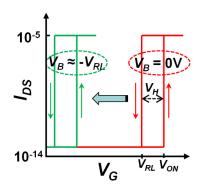

**Fig. 2.4.**  $I_D$ - $V_G$  of relay designed with stiff  $k_{\text{eff}}$ .

As discussed at the end of the last section, to tolerate inevitable process variation and avoid possible stuck-ON failure,  $k_{eff}g_d$  has to be larger than  $F_{adh}$  to some extent. According to (2.8), it is better to increase  $k_{eff}$  rather than  $g_d$  since  $V_{Pl}$  depends on  $g_d$  much more strongly (in other words, to get the same magnitude of increase of  $k_{eff}g_d$ , increasing  $g_d$  would lead to much larger increase of  $V_{Pl}$  than would increasing  $k_{eff}$ ). A typical  $I_D$ - $V_G$  characteristic of a relay with large  $k_{eff}$  is illustrated as the red curves in Fig. 2.4. The turn-on and turn-off voltages are marked as  $V_{ON}$  and  $V_{RL}$ , respectively. Since  $V_{RL}$  is much larger than zero (due to large  $k_{eff}$ ), the relay can easily be turned off at  $V_G < V_{RL}$ , not to mention at  $V_G = 0$  V.

In a digital IC, dynamic energy consumption is proportional to  $V_{DD}^2$ , where  $V_{DD}$  is the voltage swing of digital voltage signals. A stiffer structure results in larger  $V_{ON}$  (thus requiring larger  $V_{DD}$ ) which in turn results in larger energy consumption. To reduce energy consumption, the most efficient way is to decrease  $V_{DD}$ . In the case of a 4-terminal (4-T) relay, one can apply a bias voltage to the body electrode to pre-reduce the actuation and contact gap sizes to a certain extent, and then use a smaller gate voltage swing  $V_{DD}$  to turn the relay on and off, as shown in Fig. 2.5. This effectively shifts the  $I_D$ - $V_G$  curve along the horizontal axis to the left, as the green curves in Fig. 2.4. Ideally, the maximum possible body bias is  $|V_B| = V_{RL}$ , in which case  $V_{DD}$  can ideally be as low as the hysteresis voltage  $V_H$ .

Fig. 2.5. Schematic of body-biased relay operation

#### 2.4.2 Scaling Analysis of Operating Voltage and Energy of Body-Biased Relay

The analysis of the minimum switching voltage swing of a body-biased relay is different than that for a NPI-mode relay vs. a PI-mode relay, and thus is discussed separately below.

#### 2.4.2.1 NPI Relay Scaling Analysis

The Gate-to-Body voltage  $V_{\rm GB}$  to turn on a NPI-mode relay is shown in (2.10), namely,

$$V_{GB} = V_{on-NPI} = \sqrt{\frac{2k_{eff}g_d(g_0 - g_d)^2}{\varepsilon_0 A_{ACT}}}.$$

(2.21)

To turn off the relay, (2.12) has to be satisfied, which means

$$V_{GB} < V_{RL} = \sqrt{\frac{2(k_{eff}g_d - F_{adh})(g_0 - g_d)^2}{\varepsilon A_{ACT}}}$$

(2.22)

The hysteresis voltage is thus

$$V_{H} = V_{on-NPI} - V_{RL}$$

$$= \sqrt{\frac{2k_{eff}g_{d}(g_{0} - g_{d})^{2}}{\varepsilon A_{ACT}}} \left(1 - \sqrt{1 - \frac{F_{adh}}{k_{eff}g_{d}}}\right). \tag{2.23}$$

If  $k_{eff}g_d \gg F_{adh}$ , (2.23) can be simplified as

$$V_{H} \approx \frac{F_{adh}(g_{0} - g_{d})}{\sqrt{2\varepsilon A_{ACT}k_{eff}g_{d}}} \ge F_{adh} \sqrt{\frac{2g_{d}}{\varepsilon k_{eff}A_{ACT}}},$$

(2.24)

where  $g_0 \ge 3g_d$  is used in the derivation (NPI-mode design). (2.24) gives the lower limit of the hysteresis voltage of NPI-mode relay. Note that the equality holds when  $g_0 = 3g_d$ . In other words, for a variation-tolerant NPI-mode relay  $(k_{eff}g_d \gg F_{adh})$ , the hysteresis voltage can be minimized when it is designed to be at the boundary of NPI-mode and PI-mode operation, *i.e.*  $g_0 = 3g_d$ .  $V_H$  can be further reduced by decreasing  $F_{adh}$  and  $g_d$ , or increasing  $k_{eff}$  and  $A_{ACT}$ .

The switching energy of a body-biased NPI-mode relay also can be written in an analytical form. Assuming  $V_B = -V_{RL}$  and  $V_{DD} = V_H$ , the energy required to turn on a NPI-mode relay is

$$E_{NPI} = V_{GB} * \Delta Q = V_{GB} (C_{on} V_{GB} - C_{off} | V_B |)$$

$$= C_{on} (V_{RL} + V_H)^2 - C_{off} V_{RL} (V_{RL} + V_H)$$

$$^{i} \approx (C_{on} - C_{off}) V_{RL}^2 + (2C_{on} - C_{off}) V_{RL} V_H$$

<sup>&</sup>lt;sup>i</sup> The second order term  $C_{on}V_H^2$  is very small, so ignored.

$$_{i} \approx \frac{2(k_{eff}g_{d} - F_{adh})(g_{0} - g_{d})g_{d_{BS}}}{g_{0} - g_{d} + g_{d_{BS}}} + \frac{F_{adh}(g_{0} - g_{d})(g_{0} - g_{d} + 2g_{d_{BS}})}{g_{0} - g_{d} + g_{d_{BS}}}$$

$$= \frac{(g_0 - g_d)}{g_0 - g_d + g_{d_{BS}}} \left[ F_{adh}(g_0 - g_d) + 2k_{eff} g_d g_{d_{BS}} \right], \tag{2.25}$$

where  $g_{d_{BS}}$  is the contact gap size with the Body biased at  $V_B$  and Gate grounded. For a body-biased NPI-mode relay, since  $g_0 - g_d \ge 2g_d \gg g_{d_{BS}}$ , (2.25) can be further simplified as

$$E_{NPI} \approx 2k_{eff}g_dg_{d_{BS}} + F_{adh}(g_0 - g_d) \ge 2k_{eff}g_dg_{d_{BS}} + 2F_{adh}g_d.$$

(2.26)

Eq. (2.26) indicates that  $E_{\rm NPI}$  has a minimum value when  $g_0$  is minimized, i.e.  $g_0 = 3g_d$ .  $F_{\rm adh}$ ,  $g_d$ , and  $g_{d_{BS}}$  need to be reduced to further decrease  $E_{\rm NPI}$ . Interestingly,  $E_{\rm NPI}$  doesn't depend on  $A_{\rm ACT}$ , rather, it is fundamentally limited by  $F_{adh}$  and  $g_d$ .

#### 2.4.2.2 PI Mode Scaling Analysis

In quasi-static analysis, the turn-on voltage of a PI-mode relay is given by (2.8). The release voltage  $V_{\rm RL}$  is the same as that shown in (2.22). Therefore the hysteresis voltage is

$$V_{H} = \sqrt{\frac{8k_{eff}g_{0}^{3}}{27\varepsilon A_{ACT}}} - \sqrt{\frac{2(k_{eff}g_{d} - F_{adh})(g_{0} - g_{d})^{2}}{\varepsilon A_{ACT}}}.$$

(2.27)

$V_{\rm H}$  is minimized when

$$g_0 = 3\left(g_d - \frac{F_a}{k_{eff}}\right). \tag{2.28}$$

Namely,

$$V_{H} \ge V_{H\_min} = V_{H}|_{g_0 = 3\left(g_d - \frac{F_{adh}}{k_{eff}}\right)} = F_{adh} \sqrt{\frac{2}{k_{eff} \varepsilon A_{ACT}} \left(g_d - \frac{F_{adh}}{k_{eff}}\right)}. \tag{2.29}$$

If  $k_{eff}g_d \gg F_{adh}$  (to avoid stuck-ON failure), (2.28) and (2.29) can be simplified as

$$g_0 \approx 3g_d, \tag{2.30}$$

and

$$\mathrm{i} \sqrt{1 - \frac{F_a}{k_{eff} g_d}} \approx 1 - \frac{1}{2} \frac{F_a}{k_{eff} g_d}.$$

$$V_H \ge V_{H\_min} \approx V_H|_{g_0 = 3g_d} \approx F_{adh} \sqrt{\frac{2g_d}{k_{eff} \varepsilon A_{ACT}}}$$

(2.31)

respectively. Therefore, according to (2.30) and (2.31),  $V_{\rm H}$  of a variation-tolerant (i.e.  $k_{eff}g_d \gg F_{adh}$ ) PI-mode relay can minimize when the relay is designed to be close to the boundary of PI-mode and NPI-mode operation, i.e.  $g_0 \approx 3g_d$ . The minimum  $V_{\rm H}$  can be further decreased by decreasing  $F_{\rm adh}$  and  $g_{\rm d}$ , or increasing  $k_{\rm eff}$  and  $A_{\rm ACT}$ . In addition, it is very interesting to note that (2.31) has the same form as (2.24). This indicates that  $V_{\rm H}$  of both a PI-mode relay and a NPI-mode relay converges to the same minimum value if the relay is designed to operate at the boundary of PI-mode and NPI-mode operation (i.e.  $g_0 \approx 3g_d$ ) and has a large effective spring constant (i.e.  $k_{eff}g_d \gg F_{adh}$ ). This provides an important design guideline for achieving an ultra-low-voltage logic relay.

The analysis of switching energy of a PI-mode relay is similar to that for a NPI-mode relay. Again assuming  $V_B = -V_{RL}$  and  $V_{DD} = V_H$ , the energy to turn on a PI-mode relay is

$$\begin{split} E_{PI} &= V_{GB} * \Delta Q = V_{GB} \left( C_{on} V_{GB} - C_{off} | V_{B} | \right) \\ &= C_{on} (V_{RL} + V_{H})^{2} - C_{off} V_{RL} \left( V_{RL} + V_{H} \right) \\ &\approx \left( C_{on} - C_{off} \right) V_{RL}^{2} + \left( 2C_{on} - C_{off} \right) V_{RL} V_{H} \\ & \\ & \\ & \\ & \frac{2 \left( k_{eff} g_{d} - F_{adh} \right) (g_{0} - g_{d}) g_{dBS}}{g_{0} - g_{d} + g_{dBS}} + \\ & \\ & \frac{g_{0} - g_{d} + 2g_{dBS}}{(g_{0} - g_{d}) (g_{0} - g_{d} + g_{dBS})} \sqrt{\frac{2(k_{eff} g_{d} - F_{adh})(g_{0} - g_{d})^{2}}{\varepsilon A_{ACT}}} \left( \sqrt{\frac{8k_{eff} g_{0}^{3}}{27\varepsilon A_{ACT}}} - \sqrt{\frac{2(k_{eff} g_{d} - F_{adh})(g_{0} - g_{d})^{2}}{\varepsilon A_{ACT}}} \right). \end{split}$$

(2.32)

To gain insight into the dependence of  $E_{PI}$  on relay design parameters, numerical simulation is needed and will be presented in Chapter 4.

# 2.5 Comparison of Minimum Voltage and Energy of Different Relay Designs

The above analytical analyses are summarized in Table 2.1. The idealistic design is the conventional one which has zero  $V_{\rm RL}$  (and hence doesn't need Body biasing), but requires the spring constant  $k_{\rm eff}$  to be as small as possible. It can achieve smaller switching energy E, but is susceptible to stuck-ON failure. The body-biasing designs, in contrast, have stiffer spring constant, and thus can be turned off properly. Note that both NPI-mode and PI-mode body-biased relays have similar  $V_{\rm DD\_min}$  (see (2.24) and (2.31)) which can be achieved if  $k_{eff} \gg F_{adh}/g_d$  and  $g_0 \approx 3g_d$ . The performances of NPI-mode relay and PI-mode relays become similar if  $g_0$  approaches  $3g_d$ , which is not surprising because both  $V_{\rm DD\_min}$  and  $E_{\rm min}$  are continuous functions of  $g_0$ .

<sup>&</sup>lt;sup>i</sup> The second-order term  $C_{on}V_H^2$  is very small, hence ignored.

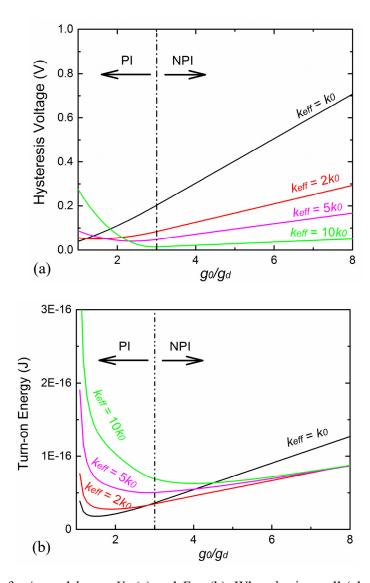

**Fig. 2.6.** Effects of  $g_0/g_d$  and  $k_{\rm eff}$  on  $V_{\rm H}$  (a) and  $E_{\rm min}$  (b). When  $k_{\rm eff}$  is small (close to  $k_0$ ), PI mode has smaller  $V_{\rm H}$  and  $E_{\rm min}$ . Increasing  $k_{\rm eff}$  shifts the minimum- $V_{\rm H}$  and minimum- $E_{\rm min}$  points towards the NPI region of relay design. When  $k_{eff} \gg F_{adh}/g_d$ ,  $V_{\rm H}$  is minimized when  $g_0$  is near  $3g_d$ .

The value of  $g_0$  to minimize energy of a body-biased relay is not very obvious. On one hand, the term  $F_{adh}(g_0-g_d)$  on the right-hand-side of Eq. (2.26) decreases monotonically with decreasing  $g_0$  and reaches a minimum value at  $g_0=3g_d$ . This indicates that an even smaller  $g_0$  (e.g.  $<3g_d$ , i.e. in PI mode) may be beneficial for achieving smaller energy. On the other hand, since  $k_{eff}$  is relatively large ( $k_{eff}\gg\frac{F_{adh}}{g_d}$ ), the other term  $2k_{eff}g_dg_{dgs}$  in (2.26) can be significant unless the relay is designed to be operated in NPI-mode such that  $g_{dgs}$  is very small with body biasing. These two competing facts indicate that  $g_0$  should be somewhere close to  $3g_d$ , but the exact value needs numerical simulation (discussed in Chapter 4). The above analysis can be more clearly illustrated with Fig. 2.6 which shows the effects of both  $k_{eff}$  and  $g_0/g_d$  on  $V_H$  and  $E_{min}$ . The following values are used for plotting Fig. 2.6:  $g_d = 5$ nm,  $F_{adh} = 1.81$  nN, and  $A_{ACT} = 1$

$μm^2$ . Clearly, when  $k_{eff}$  is close to  $F_{adh}/g_d$  (i.e. similar to the idealistic case), the PI-mode relay has smaller  $V_H$  and  $E_{min}$ . Increasing  $k_{eff}$  reduces  $V_H$  but increases  $E_{min}$ , and shifts the minimum- $V_H$  and minimum-E points towards the NPI-mode design region. Specifically, when  $k_{eff} \gg F_{adh}/g_d$ ,  $V_H$  is minimized when  $g_0 \approx 3g_d$ .

Please note that, since  $k_{eff}$  of a body-biased relay is larger than that of the idealistic design, the body-biased relay can operate with a smaller  $V_{\rm DD}$ . In practical ICs, parasitic capacitance-induced energy consumption (i.e.  $CV_{DD}^2$ ) can be more significant than switching energy of the logic devices themselves. Therefore, smaller  $V_{DD}$  is more beneficial for achieving ultra-low-power circuits.

TABLE 2.1

COMPARISON OF VOLTAGES AND ENERGY CONSUMPTION OF DIFFERENT DESIGNS

| Design                           |     | $V_{ m PI}$                                                     | $V_{ m RL}$                                                               | $V_{DD\_min}$                                                  |                                                      | Conditions                         |                         |  |

|----------------------------------|-----|-----------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|------------------------------------|-------------------------|--|

| Idealistic (w/o V <sub>B</sub> ) |     | $\sqrt{\frac{8k_{eff}g_0^3}{27\varepsilon_0A_{ACT}}}$           | 0                                                                         | $F_{adh}\sqrt{rac{g_d}{k_{eff}arepsilon A_{ACT}}}$            | $2F_{adh}g_d$                                        | $g_0 = 1.5g_d$                     | $k_{eff} = F_{adh}/g_d$ |  |

| With body bias                   | NPI | $\sqrt{\frac{2k_{eff}g_d(g_0 - g_d)^2}{\varepsilon_0 A_{ACT}}}$ | $\sqrt{\frac{2(k_{eff}g_d - F_{adh})(g_0 - g_d)^2}{\varepsilon A_{ACT}}}$ | $\sim F_{adh} \sqrt{\frac{2g_d}{k_{eff} \varepsilon A_{ACT}}}$ | $ \sim 2k_{eff}g_{d}g_{d_{BS}} $ $ + 2F_{adh}g_{d} $ | $g_0 \approx 3g_d$                 | $k_{eff} \gg$           |  |

|                                  | PI  | $\sqrt{rac{8k_{eff}g_0^3}{27arepsilon_0 A_{ACT}}}$             | $\sqrt{\frac{2(k_{eff}g_d - F_{adh})(g_0 - g_d)^2}{\varepsilon A_{ACT}}}$ | $\sim F_{adh} \sqrt{\frac{2g_d}{k_{eff} \varepsilon A_{ACT}}}$ | $\leq E_{NPI\_min}$ . Need simulation.               | $g_0 \approx 3(g_d - F_{adh}/g_d)$ | $F_{adh}/g_d$           |  |

# 2.6 Summary

A MEM relay can be designed for operation in one of two modes: PI and NPI. Using the parallel-plate approximation,  $g_0/g_d \ge 3$  for a NPI-mode relay whereas  $g_0/g_d < 3$  PI for a PI-mode relay. The conventionally idealistic design, which requires low  $k_{\rm eff}$ , has both small  $V_{\rm PI}$  and small switching energy, but unfortunately is susceptible to stuck-ON failure and thus is not practical. A stiffer structure is needed to solve this problem, which results in increased turn-on voltage. Body biasing can be used to achieve a low gate voltage swing  $V_{\rm DD}$  (as low as  $V_{\rm H}$ ), to avoid significantly increasing the switching energy. The minimum  $V_{\rm DD}$  is limited by  $V_{\rm H}$ , so smaller  $V_{\rm H}$  is preferred to minimize  $V_{\rm DD}$ .

A body-biased relay can be designed to operate in either PI mode or NPI mode. When  $k_{\rm eff}$  is small (e.g. close to  $F_{\rm adh}/g_{\rm d}$ ), the PI mode design has smaller  $V_{\rm H}$ . Increasing  $k_{\rm eff}$  reduces  $V_{\rm H}$  (at the trade-off of increasing  $|V_{\rm B}|$ ) and shifts the minimum- $V_{\rm H}$  design point (i.e.  $g_0/g_{\rm d}$ ) towards the NPI design. When  $k_{eff} \gg F_{adh}/g_d$ , the minimum- $V_{\rm H}$  design point approaches  $g_0/g_{\rm d} \approx 3$ , i.e. the boundary of PI-mode and NPI-mode designs.

## 2.7 References

- [1] S. Hanson, B. Zhai, K. Bernstein, D. Blaauw, A. Bryant, L. Chang, K. K. Das, W. Haensch, E. J. Nowak, and D. M. Sylvester, "Ultralowvoltage, minimum-energy CMOS," *IBM J. Res. & Dev.*, vol. 50, no. 4/5, pp. 469-490, Sep. 2006.

- [2] B. H. Calhoun, A. Wang, and A. Chandrakasan, "Modeling and sizing for minimum energy operation in sub-threshold circuits," *IEEE J. Solid-State Circuits*, vol. 40, no. 9, pp. 1778-1786, Sep. 2005

- [3] F. Chen, H. Kam, D. Marković, T.-J. King Liu, V. Stojanović, and E. Alon, "Integrated circuit design with NEM relays," *Proc. IEEE/ACM Int'l Conf. Comput.-Aided Des.*, 2008, pp. 750-757.

- [4] R. Nathanael, V. Pott, H. Kam, J. Jeon, and T.-J. King Liu, "4-Terminal relay technology for complementary logic", *IEEE Int. Electron Devices Meeting Tech. Dig.*, 2009, pp. 223-226

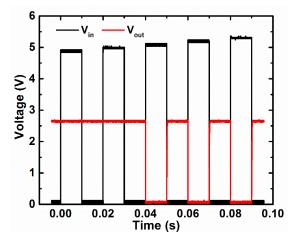

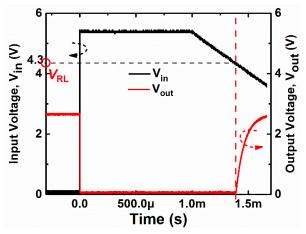

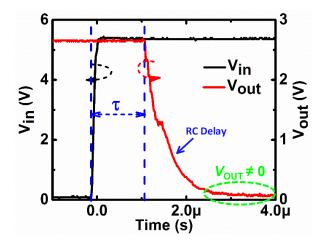

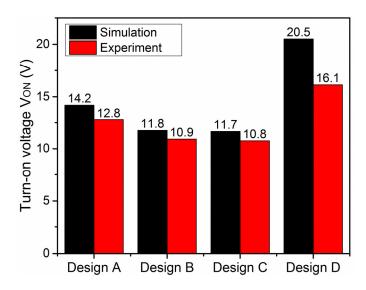

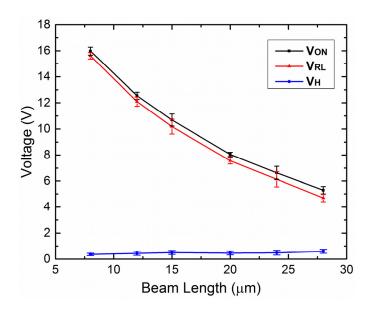

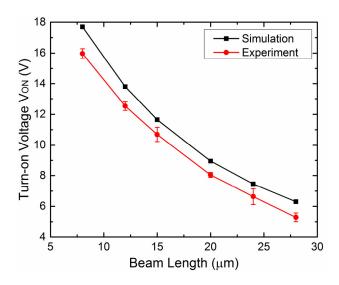

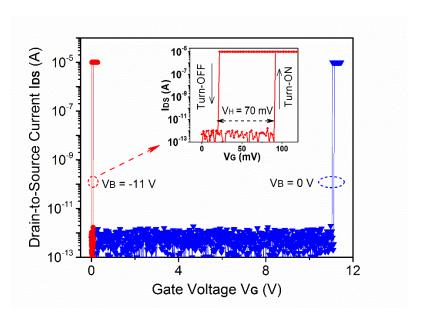

- [5] J. Fujiki, N. Xu, L. Hutin, I-R. Chen, C. Qian, and T.-J. K. Liu, "Microelectromechanical relay and logic circuit design for zero crowbar current," *IEEE Trans. Electron Devices*, vol. 61, no.9, pp. 3296-3302, Sep. 2014