### Closed Loop Digital LDO Linear Controller

Zinia Tuli

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2019-137 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-137.html

October 2, 2019

Copyright © 2019, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Closed Loop Digital LDO Linear Controller

Zinia Tuli 9/27/2019

## Agenda

- Problem statement

- Basic LDO

- Architecture

- Test bench

- Results

- Details of Closed Loop LDO

- Discussion

- Challenges

### Problem Statement

Want to build a closed loop digital LDO linear controller that provides constant Vout regardless of variable Vin with

- 1. At least 75% current efficiency when I\_Load=0.35mA

- 2.100mV regulation range

- 3. High clock frequency

- 4. Stable/Constant Vout

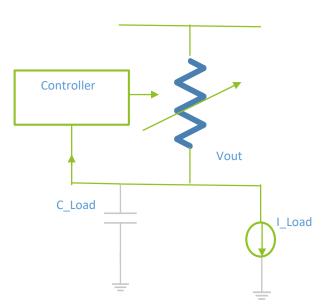

## Basic LDO

Vin

- Low dropout regulators (LDOs) are effective ways to regulate an output voltage that is powered from a higher input voltage

- A basic LDO involves a variable resistor (can be implemented by using PMOS transistors), I\_Load, C\_Load, and a controller.

- The job of the controller is to keep the output voltage constant even with variable input voltage. If the load current (I\_Load) increases, the variable resistor should decrease to increase the current flow from the input through the resistor to the output and vice versa in order to make Vout remain constant.

- The controller detects the deviation of the Vout from its desired value and responds accordingly to

either increase or decrease the variable resistor's value to keep the Vout constant.

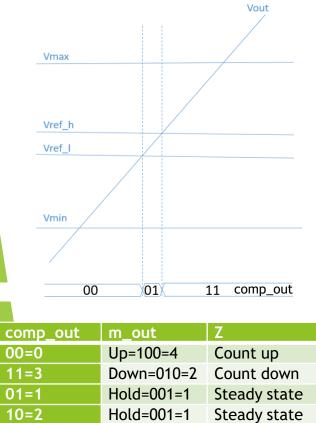

### Architecture

Closed loop design of digital LDO with digital controller (Decision maker and Decision executer), 2 Comparators and Pmos devices (binary coding power gates which has 8 different size), CL, IL:

#### Input of Comparators:

- The job of two comparators is to detect the position of Vout and feed the information into the decision maker block.

- The decision maker block takes that information and decides if Vout should go up, down, or stay hold within Vref\_h and Vref\_l.

- The decision maker feeds this information into the 8 bit binary counter or decision executer which physically changes the value of power gate code <7:0> (input of the Pmos devices) and thus Vout.

- An example: when Comp\_h=0 (Vref\_h> Vout, or Vout is lower) and Comp\_l=0 (Vref\_l> Vout, or Vout is lower)→Decision maker output=Up→Decision executer output = Power gate code<7:0> +1. Thus, Power gate code counts up from its previous value by turning on more Pmos devices.

#### Combined truth table of digital controller of LDO:

| comp_out (output of comparators) | m_out (output of decision maker) | Z (output of decision executer)     |

|----------------------------------|----------------------------------|-------------------------------------|

| 00=0                             | Up=100=4                         | Count up: Power gate code<7:0> +1   |

| 11=3                             | Down=010=2                       | Count down: Power gate code<7:0> -1 |

| 01=1                             | Hold=001=1                       | Steady state                        |

| 10=2                             | Hold=001=1                       | Steady state                        |

- Pmos device unit size: W=210nm, L=32nm

- Vin=1.05V

- C\_Load=200pF

- Proposed Metrics:

- 1. Current efficiency= 75-99% for 0.35mA current load (RL=3K $\Omega$ )

- 2. Regulation range= 100mV

- 3. Clk frequency=1MHz 1GHz

- 4. Vout being stable within regulation range

### Testbench and RTL code

```

1 timescale 1 ns / 1 ps

2 define expect(nodeName, nodeVal, expVal, cycle) if (nodeVal !== expVal) begin \

$display("\t ASSERTION ON %s FAILED @ CYCLE = %d, 0x%h != EXPECTED 0x%h", \

3

4

nodeName,cycle,nodeVal,expVal); $stop; end

5

6 module decoder tb();

7 reg [1:0] comp out = 0;

8 wire [2:0] m out;

9 wire [7:0] Z;

10 reg clk = 0;

11 wire resetb;

12 integer cycle = 0;

13 integer i;

14 wire up, down, hold;

15 assign up = m out ==3'b100;

16 assign down = m out ==3'b010;

17 assign hold = m out ==3'b001;

18

19

always #(`CLOCK PERIOD * 0.5) clk = ~clk;

20 always @(posedge clk) cycle = cycle + 1;

21 decoder decoder inst (.comp out(comp out), .m out(m out), .Z(Z), .clk(clk), .resetb(resetb));

22

23 reg [6:0] counter ;

24 initial begin

25 counter = 7'd0:

26 end

27

28 always @ (posedge clk)

29 begin

30 counter ← counter + 1 ;

31 end

32

33 assign resetb = (counter == 7'd0) ? 0 : 1;

34

35

initial begin

36

$vcdpluson;

37

// Extra cycles to flush out any initial X's

38

repeat(4) @(posedge counter[2]);

39

for (i=1; i<=50; i=i+1) begin</pre>

// Input + output events on clock rising edge

40

41

@(posedge counter[2]);

42

#0.001:

43

comp out = i;

44

end

45

$vcdplusoff;

46

$display("\t **Ran through all test vectors**"); $finish;

47

end

48

49

initial begin

50

$monitor($time,": comp out=%d, m out=%b, Z=%b, cycle=%d", comp out, m out, Z, cycle);

51

end

52 endmodule

```

1 module decoder( 2 input [1:0] comp out, //comp out 3 input clk, 4 input resetb, 5 output reg [2:0] m out, //decision maker output (up down hold) 6 output reg [7:0] Z); //decision executer output or power gate code 7 8 //decision maker 9 always @ (posedge clk) 10 begin if (comp out ==2'b00) m out=3'b100; 11 //output=up else if (comp out == 2'b11) m out=3'b010; 12 //output=down 13 else m out=3'b001; //when comp out==2'b01 or 2'b10 output=hold 14 end 15 16 //decision executer 17 always @ (posedge clk) 18 begin 19 if (!resetb)  $Z \ll 0$ ; 20 else if (m out[2]) Z ⇐ Z+1; //count up else if (m out[1]) Z<=Z-1; // count down</pre> 21 22 else Z<=Z; //steady state 23 end 24 25 endmodule

### Results

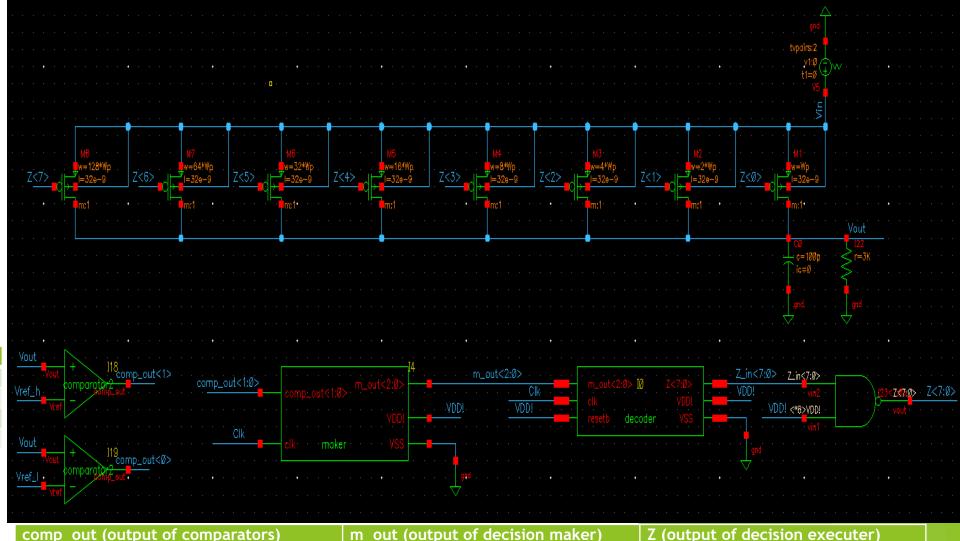

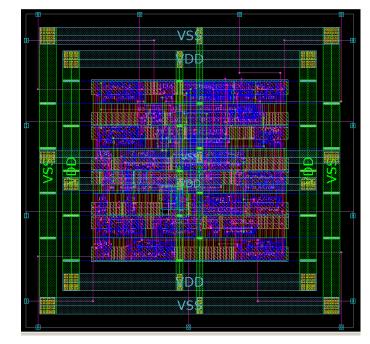

#### Gate Level Schematic of LDO controller (using IC compiler):

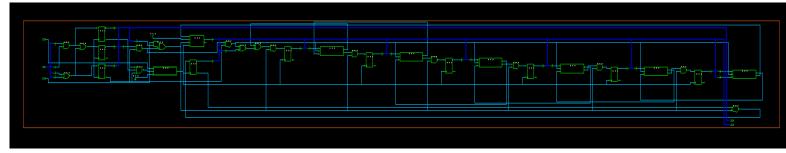

#### Layout of LDO controller(using IC compiler):

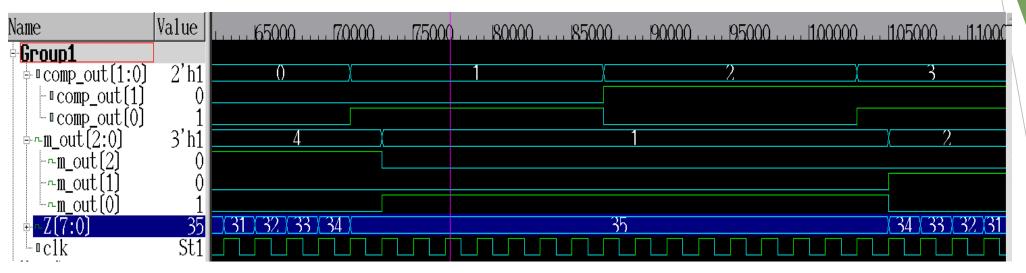

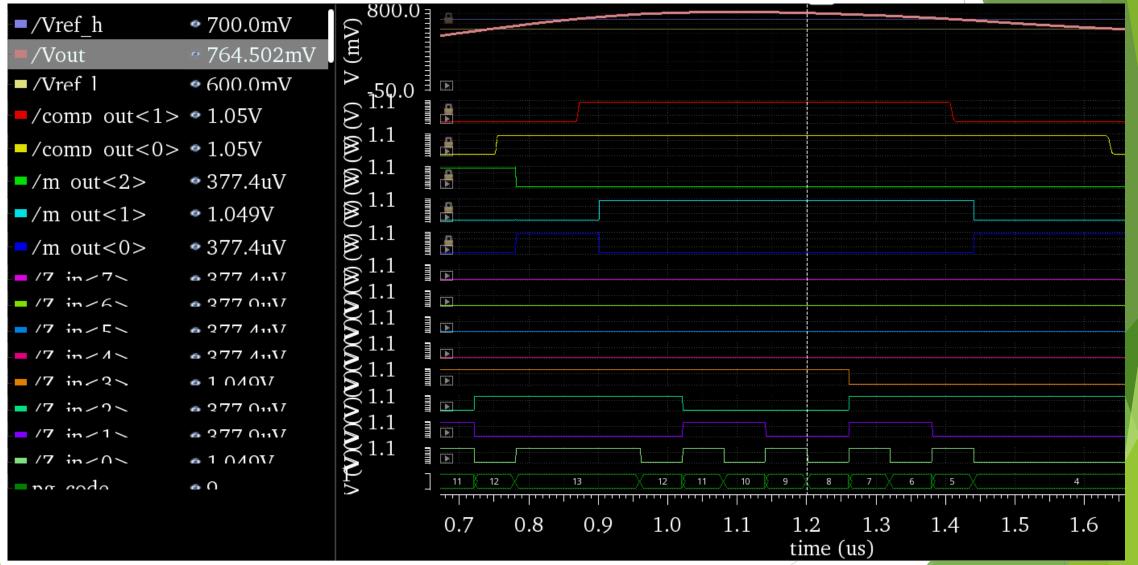

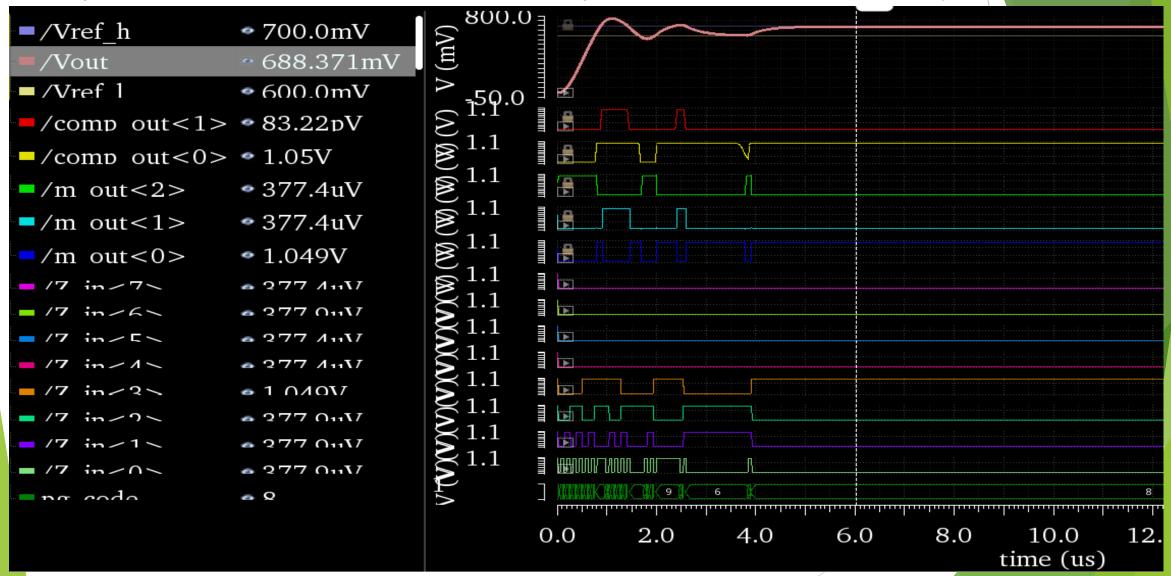

### Output Waveform (using DVE) of Digital LDO Controller:

In figure above, when Vout is between Vref\_l & Vref\_h, comp\_out=01=1, m\_out is Hold or 001=1, and Z is at steady state=35 which means the controller works and when used in the closed loop LDO, the Vout looks like the graph on the right where Vout is constant/stable between Vref\_h and Vref\_l.

| comp_out | m_out      | Ζ            |

|----------|------------|--------------|

| 00=0     | Up=100=4   | Count up     |

| 11=3     | Down=010=2 | Count down   |

| 01=1     | Hold=001=1 | Steady state |

| 10=2     | Hold=001=1 | Steady state |

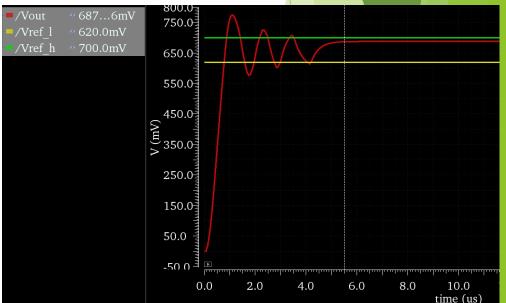

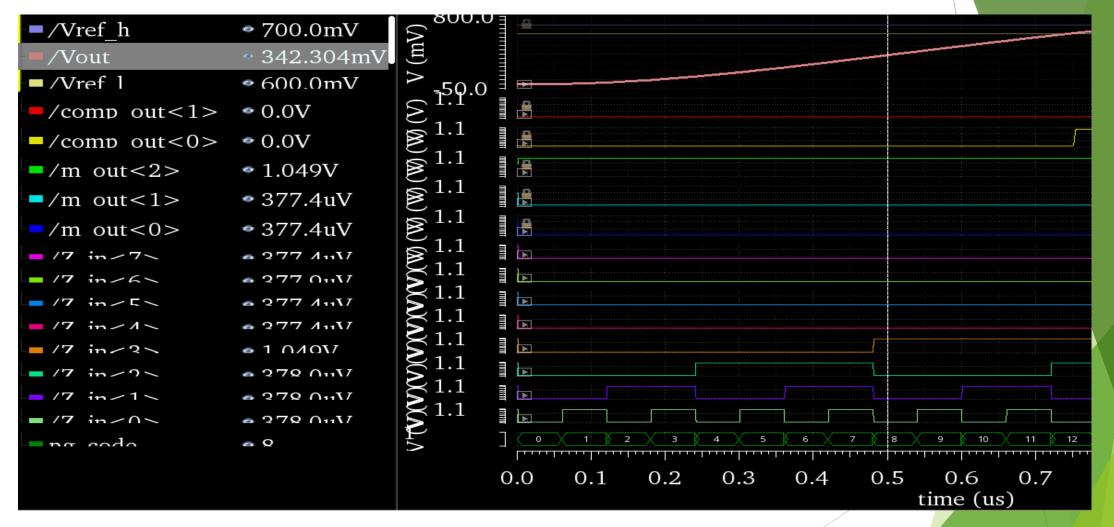

#### Vout waveform: The transient of the number of turned-on switches

| wn  |

|-----|

| ate |

| ate |

|     |

1. Comparator, decision maker, decision executer output waveform when Vout is increasing at 0.5us:

Comp\_out=00, m\_out=100 (Up), pg code is counting up from 7 to 8 to higher # and therefore Vout is increasing

| 00=0 | Up=100=4   | Count up     |

|------|------------|--------------|

| 11=3 | Down=010=2 | Count down   |

| 01=1 | Hold=001=1 | Steady state |

| 10=2 | Hold=001=1 | Steady state |

|      |            |              |

2. Comparator, decision maker, decision executer output waveform when Vout is decreasing at 1.2us:

Comp\_out=11, m\_out=010 (Down), pg code is counting down from 9 to 8 to lower # and therefore Vout is decreasing

| 00-0 | 0p=100=4   | Count up     |

|------|------------|--------------|

| 11=3 | Down=010=2 | Count down   |

| 01=1 | Hold=001=1 | Steady state |

| 10=2 | Hold=001=1 | Steady state |

3. Comparator, decision maker, decision executer output waveform when Vout is steady at 6us:

Comp\_out=01, m\_out=001 (Hold), pg code is at steady state at 8 and therefore Vout is constant

### Discussion

### 1. Current Efficiency:

- Using Invx1\_rvt standard cells, clock frequency=111MHz, C\_Load=0.01fF, supply voltage=1.05V power consumption of the digital controller was= 90uW after APR

- The current leakage =power consumed by controller/Vin= 90uW/1.05V= 85.7uA. Therefore current efficiency=I\_Load/(I\_Load+I\_Leak)=0.35mA/(0.35mA+.0857mA)=0.80 →80% which is within proposed metrics

#### 2. Regulation Range:

In this design I was able to achieve voltage range=80mV between Vmin=0V and Vmax=Vin. This turned out to be even better than expected value (100mV)

#### 3. Clock Frequency:

For the full closed loop LDO, clk period was=6ns $\rightarrow$ clk freq=0.17GHz which meets the proposed metrics

### **Discussion Continued...**

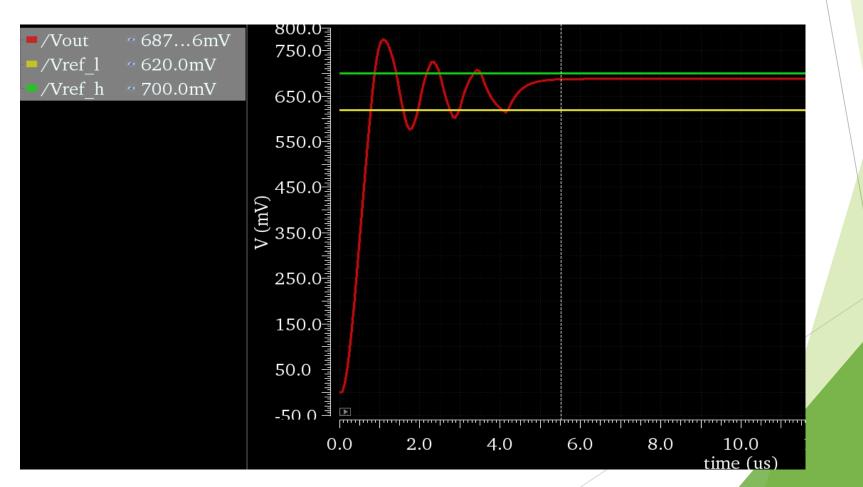

#### 4. Vout Stability:

With the closed loop, the voltage profile looks like the figure below, where Vout is stable/constant between Vref\_l=620mV and Vref\_h=700mV.

### Challenges

#### 1. Vout was increasing above Vref\_l and Vref\_h even though Z\_in<7:0> was steady:

- The reason was the current of Vout was too low compared to the pmos gates. So the current of a single pmos at Vds=700mV was measured and multiplied by 128 (because the biggest pmos size is 128x) which was equal to ~30uA\*128=3840uA=3.8mA. That means I\_Load<3.84mA→RL>0.3KΩ. First RL=1KΩ was chosen but RL=3KΩ gave better Vout curve. The lower the I\_Load the easier it is for the pmos gates to match the current with it.

- Still Vout was too high, so clk frequency was lowered by 3x and step size was decreased which made Vout to be in between Vref\_l and Vref\_h.

- 2. Vout was too rough and limit cycling (Vout is limited by the resolution of LSB) occurred:

- CL was increased by 2x (200pf) which made Vout smoother. Voltage range (between Vref\_l and Vref\_h) could have increased also to fix this issue.

# Thank you!

### Questions???