# RF Transmitter Design for Large Antenna Array Applications

Pengpeng Lu

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-191 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-191.html

December 1, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### RF Transmitter Design for Large Antenna Array Applications

by

Pengpeng Lu

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor David Aldous Professor Ali Niknejad

Fall 2018

### RF Transmitter Design for Large Antenna Array Applications

Copyright 2018

by

Pengpeng Lu

#### Abstract

RF Transmitter Design for Large Antenna Array Applications

by

#### Pengpeng Lu

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Elad Alon, Chair

Recent advances in wireless technologies have enabled fast increase of mobile data traffic. In fact, mobile data traffic has grown 18-fold over the past 5 years. The rapid growing demand imposes a big near-far problem on our wireless network. Beamforming technique provides an opportunity to efficiently solve the near-far problem, by combining elements in an antenna array in such a way that signals at particular angles experience constructive interference while others experience destructive interference.

This thesis focuses on the design of energy-efficient RF transmitters for large antenna array applications. In order to be energy-efficient, we should minimize the overhead power consumption. It makes the design challenging while minimizing out-of-band emissions and supporting multiple/reconfigurable bands as well as programmability in terms of performance (i.e., output power, noise figure, resolution, bandwidth, etc.), since any fixed frequency bandpass filters should be eliminated.

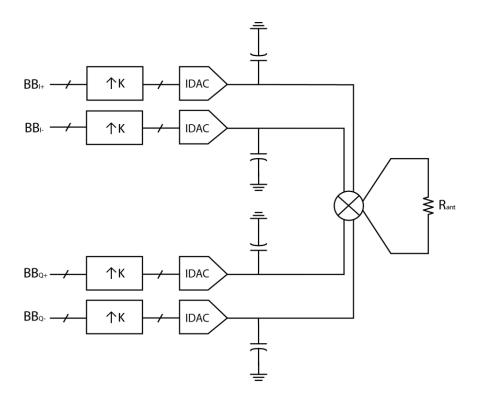

To address these challenges, a mixer-last TX architecture is proposed, which uses current DACs to deliver charge directly to the 50 Ohm output RF load. Out-of-band emissions are reduced by digital oversampling, and the charging operation of a baseband capacitor.

Using the proposed transmitter architectures, two chips were implemented. The first chip was fabricated in TSMC's 65nm CMOS technology. With a peak output power of 5.1dBm, the first chip consumes 49.2 mW and the measured noise floor at 40MHz offset is -155dBc/Hz.

Realizing it is impossible to build a single transmitter that is power efficient under all applications, we developed a generator for our proposed TX architecture using Berkeley Analog Generator (BAG) framework [1]. A generator captures the design methodology and is process portable. It could significantly lower the design cost so that different transmitters that are efficient for different design specifications can be generated. The second chip was generated by the generator and was fabricated in TSMC's 16nm CMOS technology. It consumes 5.14 mW at peak output power of -19.6 dBm. Compared with the first 65nm prototype, it is more power efficient in the output power range of less than -4 dBm.

To My Family

# Contents

| Co | Contents                              |                                                                                                                                                        |                            |  |  |  |  |  |  |

|----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|--|

| Li | List of Figures                       |                                                                                                                                                        |                            |  |  |  |  |  |  |

| Li | st of                                 | Tables                                                                                                                                                 | vi                         |  |  |  |  |  |  |

| 1  | 1.1<br>1.2<br>1.3<br>1.4              | Data Traffic Challenge                                                                                                                                 | 1<br>1<br>3<br>5<br>6      |  |  |  |  |  |  |

| 2  | eWa<br>2.1<br>2.2<br>2.3              | eWallpaper System                                                                                                                                      | 8<br>8<br>9<br>15          |  |  |  |  |  |  |

| 3  | RF<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Transmitter Design RF Transmitter for Large Array Applications Design Goal Challenge of Minimizing Out-of-band Emissions Proposed Architecture Summary | 16<br>18<br>18<br>19<br>24 |  |  |  |  |  |  |

| 4  | Mai<br>4.1<br>4.2<br>4.3              | Implementation       Implementation       Measurement Results       Reflection                                                                         | 26<br>26<br>29<br>34       |  |  |  |  |  |  |

| 5  | 5.1<br>5.2<br>5.3                     | G Generator Implementation Introduction to BAG                                                                                                         | 35<br>35<br>45<br>49       |  |  |  |  |  |  |

| 6 Co | nclusions         | <b>5</b> 0 |

|------|-------------------|------------|

| 6.1  | Thesis Summary    | 50         |

|      | Future Directions | 51         |

# List of Figures

| 1.1 | Cisco Forecasts 49 Exabytes per Month of Mobile Data Traffic by 2021. Adapted [reprinted] from "Cisco Visual Networking Index: Global Mobile Data Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Forecast Update, 2016 —2021 White Paper", Cisco, 2017                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1   |

| 1.2 | Global Growth of Smart Mobile Devices and Connections. Adapted [reprint-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|     | ed] from "Cisco Visual Networking Index: Global Mobile Data Traffic Forecast Update, 2016—2021 White Paper", Cisco, 2017                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2   |

| 1.3 | Near Far Problem. Adapted [reprinted] from "The xG Vision: Making the Inter-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2   |

| 1.0 | net truly wireless", Ali Niknejad, 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3   |

| 1.4 | Operating Principle of a phased array transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4   |

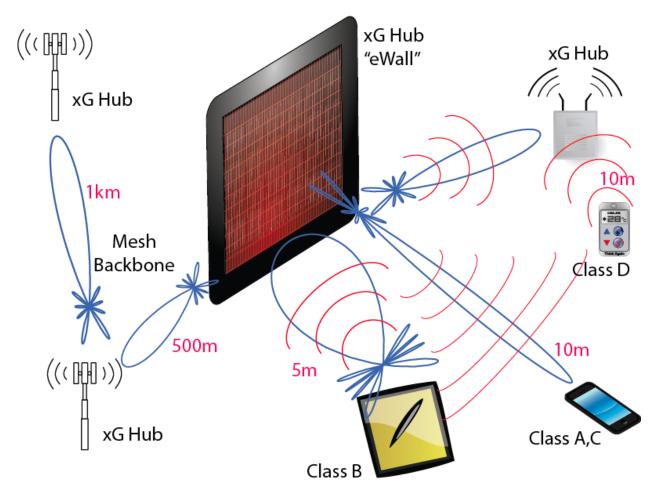

| 1.5 | xG Vision. Adapted [reprinted] from "The xG Vision: Making the Internet truly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|     | wireless", Ali Niknejad, 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6   |

| 2.1 | eWallpaper Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8   |

| 2.2 | eWallpaper Vision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9   |

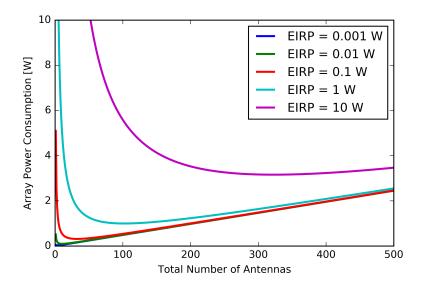

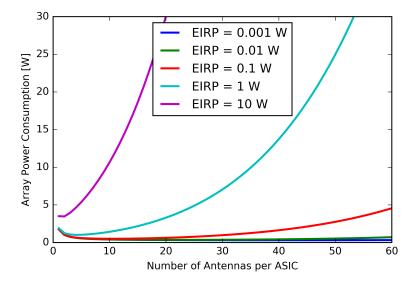

| 2.3 | Total array power consumption as a function of total number of antennas for various EIRP. Number of antennas per ASIC is held constant at 4. $(P_{ov,ASIC} = 10mW, P_{ov,ASIC} = 10mW, P_{ov,ASIC} = 10mW, P_{ov,ASIC} = 10mW, P_{ov,ASIC} = 10mW$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13  |

| 2.4 | $10mW, P_{ov,ant} = 1mW, P_{link} = 0.4mW)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10  |

|     | for various EIRP. Total number of antennas is held constant at 128. ( $P_{ov,ASIC} = 10^{-10} \text{ My P}_{out} = 10^{-10} $ | 1.0 |

| 0.5 | $10mW, P_{ov,ant} = 1mW, P_{link} = 0.4mW) \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13  |

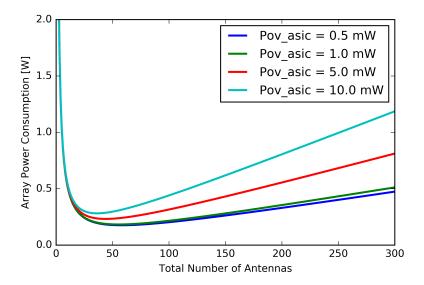

| 2.5 | Total array power consumption as a function of total number of antennas for various $P_{ov,ASIC}$ . Number of antennas per ASIC is held constant at 4. ( $EIRP =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     | $0.1W, P_{ov,ant} = 1mW, P_{link} = 0.4mW) \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14  |

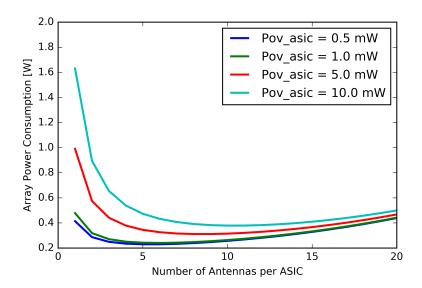

| 2.6 | Total array power consumption as a function of number of antennas per ASIC for various $P_{ov,ASIC}$ . Total number of antennas is held constant at 128. ( $EIRP =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|     | $0.1W, P_{ov,ant} = 1mW, P_{link} = 0.4mW)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15  |

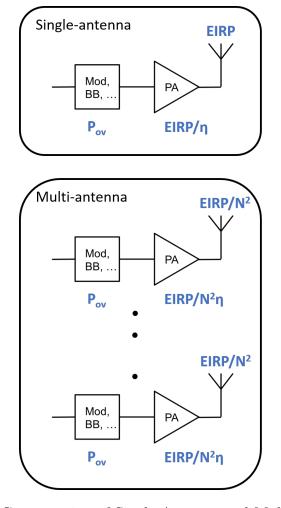

| 3.1 | Power Consumption of Single-Antenna and Multi-Antenna System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17  |

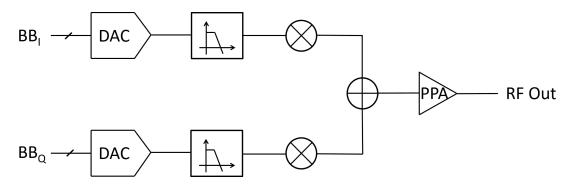

| 3.2 | Typical Analog Transmitter Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18  |

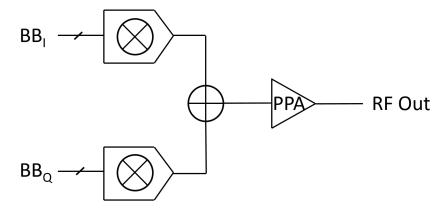

| 3.3 | Typical Digital Transmitter Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19  |

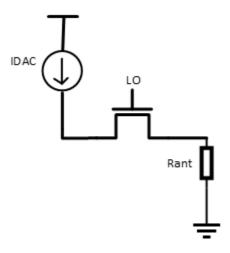

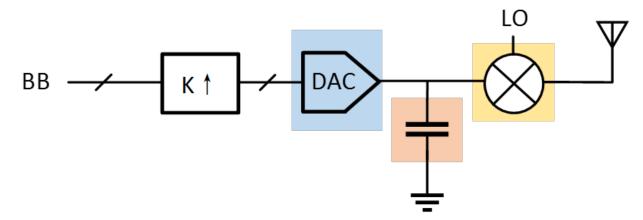

| 3.4 | TX block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20  |

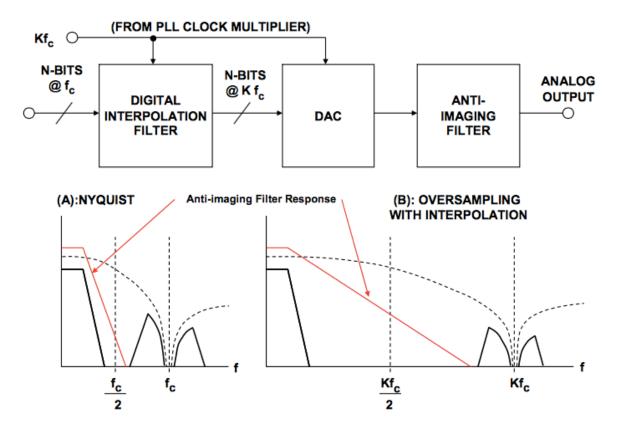

| 3.5 | Oversampling Interpolating DAC. Adapted [reprinted] from "Oversampling In-   |    |

|-----|------------------------------------------------------------------------------|----|

|     | terpolating DACs", Walt Kester, Analog Devices, 2009                         | 21 |

| 3.6 | TX Operating Principle                                                       | 23 |

| 3.7 | Intrinsic Filter                                                             | 24 |

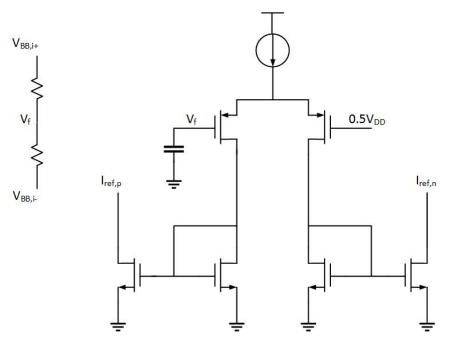

| 4.1 | TX Front-End showing NMOS/PMOS current DACs                                  | 26 |

| 4.2 | CMFB Circuit                                                                 | 27 |

| 4.3 | Simplified TX front-end to show headroom issue                               | 28 |

|     | <del>-</del>                                                                 | 29 |

| 4.4 | Scalable Blocks                                                              |    |

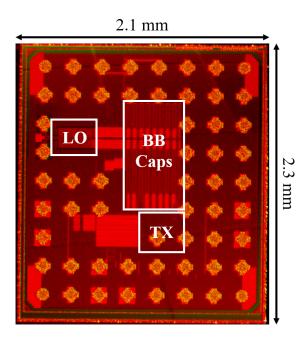

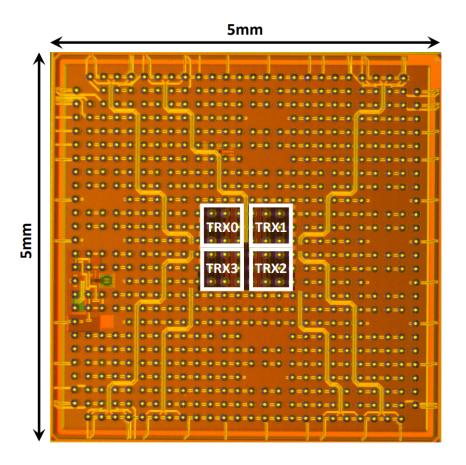

| 4.5 | Die Photo of 65nm TX Design                                                  | 30 |

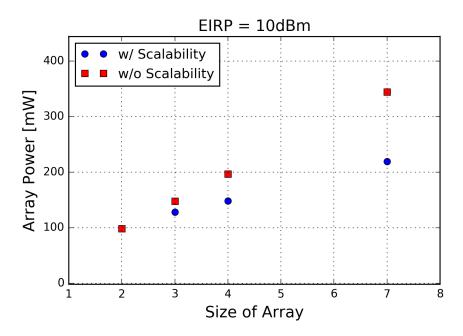

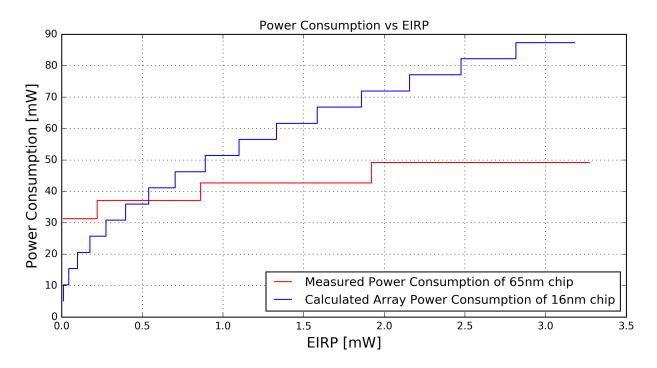

| 4.6 | Array Power Consumption w/ and w/o scalability features                      | 31 |

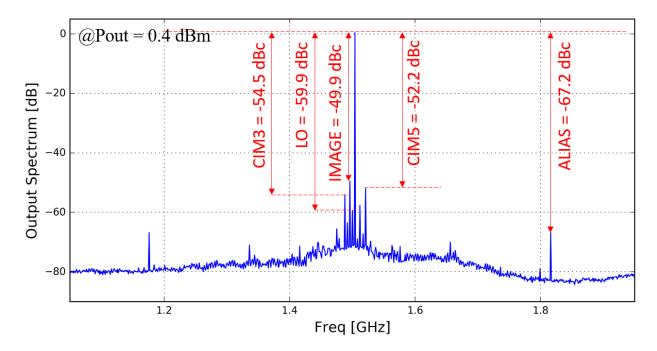

| 4.7 | Measured Spectrum of 4.2MHz single-tone                                      | 32 |

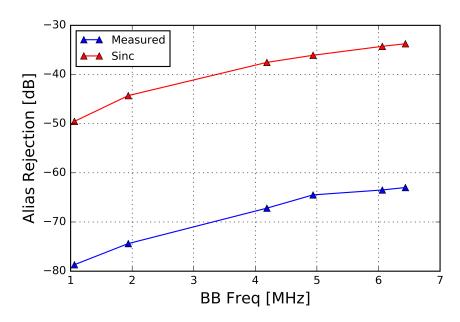

| 4.8 | Measured alias rejection and calculated alias rejection with sinc filter     | 32 |

| 4.9 | Measured 16QAM constellation                                                 | 33 |

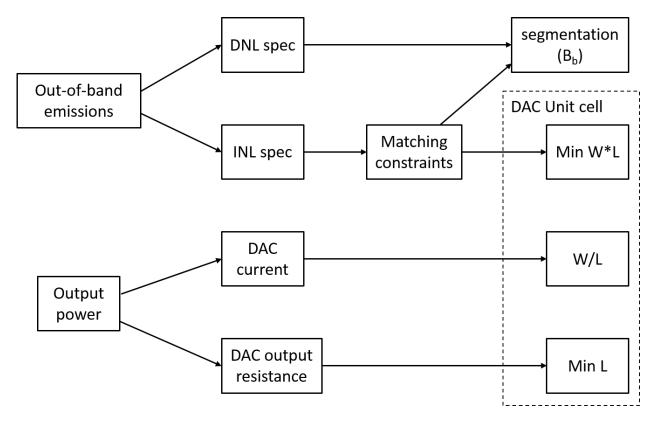

| 5.1 | DAC Design Flow                                                              | 37 |

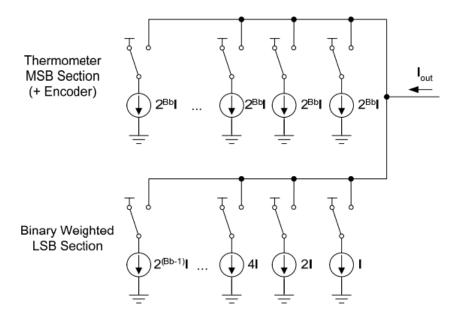

| 5.2 | Segmented DAC Design. Adapted [reprinted] from "Analog-Digital Interface In- |    |

|     | tegrated Circuits" (Lecture Notes), Bernhard Boser, 2014                     | 40 |

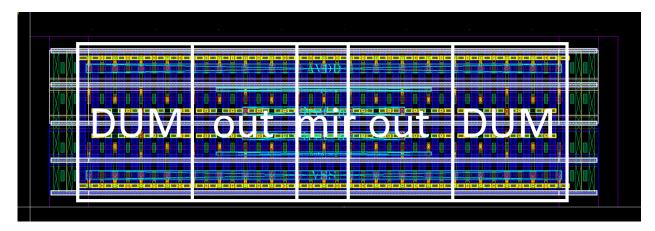

| 5.3 | DAC Unit Cell Layout                                                         | 43 |

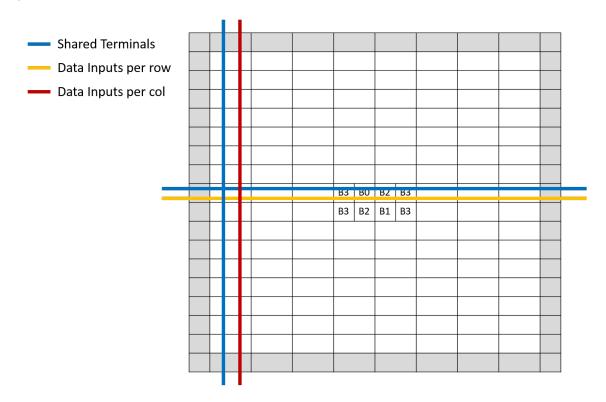

| 5.4 | Double Centroid Switching Scheme                                             | 44 |

| 5.5 | Layout Routing                                                               | 45 |

| 5.6 |                                                                              | 46 |

|     | Die Photo of 16nm TX Design                                                  |    |

| 5.7 | Power consumption comparison of the 16nm and 65nm TX designs                 | 47 |

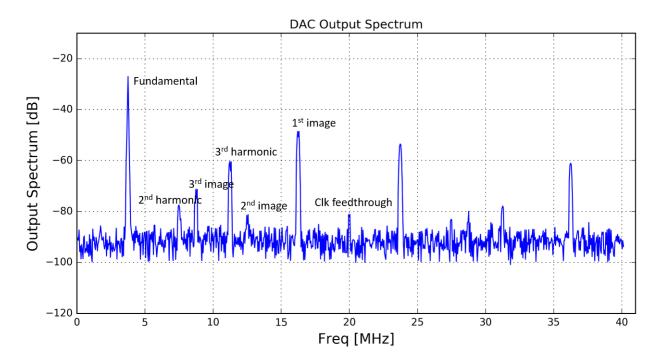

| 5.8 | Measured DAC Spectrum of 3.75MHz single-tone sampled at 20MS/s               | 48 |

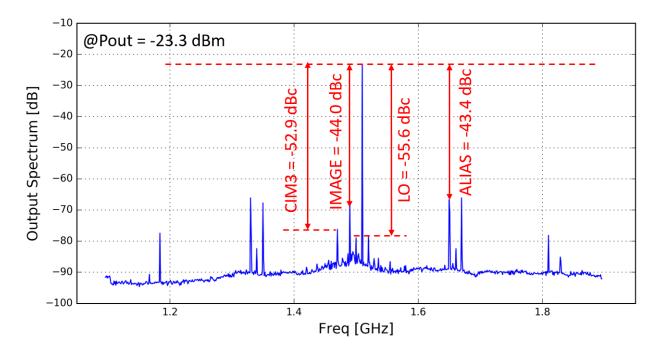

| 5.9 | Measured Spectrum of 10MHz single-tone                                       | 49 |

|     |                                                                              |    |

# List of Tables

| 4.1 | Power Breakdown at different Pout of 65nm TX Design | 30 |

|-----|-----------------------------------------------------|----|

| 4.2 | Comparison Table                                    | 33 |

| 5.1 | Power Breakdown of 16nm TX Design                   | 46 |

#### Acknowledgments

The past 6 years have been very challenging and stressful for me. Throughout this wild journey, I feel extremely fortunate to have received so much help and support from so many individuals, without whom I can never reach this finish line. I would like to take this opportunity to express my most sincere gratitude to every one of them.

First, I would like to express my sincere gratitude to my advisor, Professor Elad Alon, not only for his guidance in my research, but also for his understanding, patience, encouragement and continuous support over the years. After knowing him for more than 6 years, I am still impressed by how passionate he is about his work, and how diligently he works every day. There is no better advisor a student could hope to find than Elad.

Besides, I would like to thank Prof. Ali Niknejad, Prof. David Aldous, and Prof. Borivoje Nikolic for being on my thesis and qualification exam committee and for their valuable comments and encouragement.

My sincere thanks also goes to all BWRC staff, especially Candy Corpus, who made my experience at BWRC as smooth and stress-free as possible, and James Dunn and Brian Richards, who helped me wrestle with CAD tools and computers.

FADER is a huge project and I'm grateful to have worked with many talented friends on this project (in no particular order): Lingkai Kong, D. J. Seo, Antonio Puglielli, Amy Whitcombe, Eric Chang, Greg Lacaille, Nathan Narevsky, Zhongkai Wang, Kosta Trotskovsky, Marko Kosunen.

I would also like to thank my fellow BWRC colleagues (some of them have graduated) - Lucas Calderin, Jiashu Chen, Pi-Feng Chiu, Sijun Du, Seobin Jung, Nai-Chung Kuo, Benyuanyi Liu, Zhaokai Liu, Yue Lu, Alberto Puggelli, Sameet Ramakrishnan, Nicholas Sutardja, Angie Wang, Ruochen Wang, Meng Wei, Bonjern Yang, Luya Zhang, Qichen Zhang, Bo Zhao - for working with me on various projects, and having fun together.

Last but not the least, I would like to thank my parents, for their unconditional love and continuous support throughout my life. To my best friend Ye Tian, for being there through all the ups and downs. To my husband Guanyu, for taking care of me, and sharing all my laughs and tears. I can never get through my Ph.D journey without their love and support.

# Chapter 1

## Introduction

### 1.1 Data Traffic Challenge

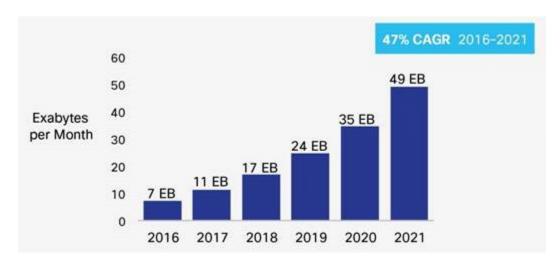

In the past few years, the world has witnessed huge and fast increase in data traffic. In fact, mobile data traffic has grown 18-fold over the past 5 years, from 400 petabytes (1 petabyte =  $10^{15}$  bytes) per month in 2011, to 7.2 exabytes (1 exabyte =  $10^{18}$  bytes) per month at the end of 2016. Cisco Visual Networking Index predicts that by 2021, monthly global mobile data traffic will be 49 exabytes [2] (Fig 1.1).

Figure 1.1: Cisco Forecasts 49 Exabytes per Month of Mobile Data Traffic by 2021. Adapted [reprinted] from "Cisco Visual Networking Index: Global Mobile Data Traffic Forecast Update, 2016—2021 White Paper", Cisco, 2017

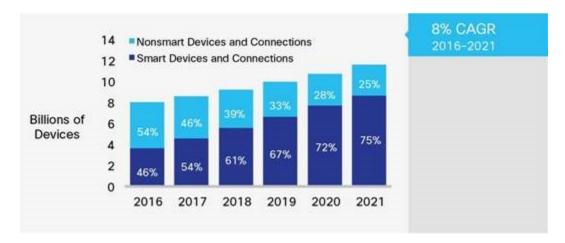

Figure 1.2: Global Growth of Smart Mobile Devices and Connections. Adapted [reprinted] from "Cisco Visual Networking Index: Global Mobile Data Traffic Forecast Update, 2016—2021 White Paper", Cisco, 2017

This trend is due to both the big increase in the data traffic per device and the number of devices worldwide. Both are expected to grow even faster in the next 5 years (Fig 1.2).

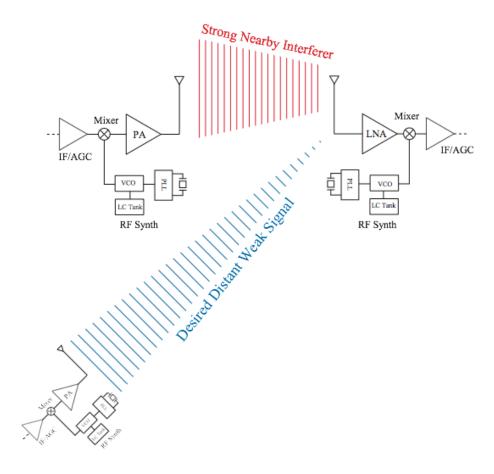

The rapid growing demand imposes a big near-far problem on our wireless network: Consider a receiver and two transmitters, one close to the receiver, the other far away. If both transmitters transmit simultaneously and at equal powers, then due to the inverse square law the receiver will receive more power from the nearer transmitter (Fig 1.3) [3]. Since one transmission's signal is the other's interferer, the signal-to-interference-plus-noise ratio (SINR) for the farther transmitter is much lower. This makes the farther transmitter more difficult, if not impossible, to understand.

Figure 1.3: Near Far Problem. Adapted [reprinted] from "The xG Vision: Making the Internet truly wireless", Ali Niknejad, 2014

### 1.2 Beamforming

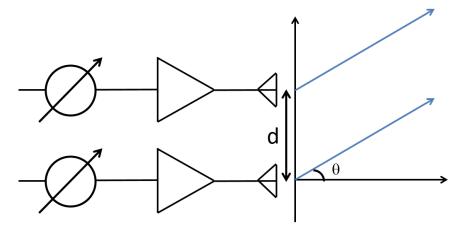

The near-far problem could be greatly relaxed if the transmitting and receiving are directional [4]. Beamforming is a technique for directional signal transmission or reception. This is achieved by combining elements in an antenna array in such a way that signals at particular angles experience constructive interference while others experience destructive interference [5–9].

To change the directionality of the array when transmitting, a beamformer controls the phase and relative amplitude of the signal at each transmitter. The simplest way is to put multiple antennas in a line and apply phase shifting only at each transmitter. Fig 1.4 illustrates the operating principle of a simple two-antenna phased array [10]. For simplicity, assume

each antenna transmits its own signal through an omnidirectional antenna. In an arbitrary direction  $\theta$  in space, due to the physical distance between these two antennas, a phase difference between signals from these two elements occurs. Far away from the antennas, the phase difference can be approximated as:

$$\phi = \frac{2\pi d}{\lambda} \cos\theta \tag{1.1}$$

Here d and  $\theta$  denote the distance between antennas and the wavelength, respectively.

Figure 1.4: Operating Principle of a phased array transmitter

By phase shifting the signal from the first TX by  $\phi$  relative to the second TX, the signals in the direction  $\theta$  in space can be realigned, and add in voltage. It is worth noting that at the same time, in the direction  $\theta'$  that satisfies

$$\frac{2\pi d}{\lambda}\cos\theta' = \pi - \frac{2\pi d}{\lambda}\cos\theta,\tag{1.2}$$

signals from these two TXs are out of phase. Therefore, the energy delivered in this direction is zero. Because energy is proportional to the square of voltage amplitude, the energy delivered in this direction is 4 times larger than a single TX. Generally, in a system with N elements, the transmitted energy is increased by  $N^2$  in the desired direction. This enables the system to boost the energy in the direction of target users, and reduce interference of other nearby systems.

The spacing between two adjacent antennas in the array is typically  $\lambda/2$  [11] to perform Nyquist sampling in space. For GHz applications, this is several centimeters (15cm@1GHz, 6.25cm@2.4GHz, 3cm@5GHz), which implies large array area. Luckily, we have enough "surface" areas around us - walls, tables, ceilings, etc. We could leverage the "surfaces" to build large antenna arrays. This concept leads us to our "xG" vision in BWRC.

#### 1.3 xG Vision

The industry is expecting 5G networks by 2020, which is positioned for a future with "everything in the cloud"—for example, immersive video conferencing, internet of things, low latency and high reliability machine-centric communication, and so on [12, 13].

Beyond 5G, researchers at BWRC (Berkeley Wireless Research Center) proposed the "xG" vision (Fig 1.5) [14–16]. In our "xG" vision, we will build a network that can grow organically with little to no user intervention or configuration. Access points (hubs) will be spreaded everywhere ,and allowed to talk to each other to form a mesh network. In order to reduce interference, antenna arrays (on "surfaces" around us) should be used to form beams and create point-to-point links. Small handsets do not need to spread energy out into a sphere of 1km radius, but simply a few meters, to the nearest "eWallpaper".

Figure 1.5: xG Vision. Adapted [reprinted] from "The xG Vision: Making the Internet truly wireless", Ali Niknejad, 2014

#### 1.4 Thesis Organization

With the introduction of beamforming, and the concept of "xG" vision and eWallpaper in this chapter, the remaining focus of the thesis will then be the presentation of circuit design techniques to build an RF transmitter for multi-antenna applications. We first introduce the whole system –eWallpaper, and discuss high-level system design concerns in Chapter 2. In Chapter 3, we begin with a comparison of system power consumption of single-antenna systems and multi-antenna systems. Overhead power is identified as the bottleneck of the system efficiency. Then a transmitter architecture that minimizes overhead power consumption is proposed. Using the proposed transmitter architectures, two chips were implemented. The first chip was implemented with traditional CAD tools in TSMC 65nm CMOS technology. Its implementation details and measurement results are shown in Chapter 4. Realizing

the fact that it is impossible to build a single TX that is power efficient for all design specifications, we wrote a generator with BAG, a process-portable circuit generator framework [1] developed in BWRC. In Chapter 5, the development of the generator is discussed. The second chip was generated by the generator and fabricated in TSMC 16nm CMOS technology. Chapter 6 concludes the entire thesis, and discusses about future directions.

# Chapter 2

# eWallpaper

### 2.1 eWallpaper System

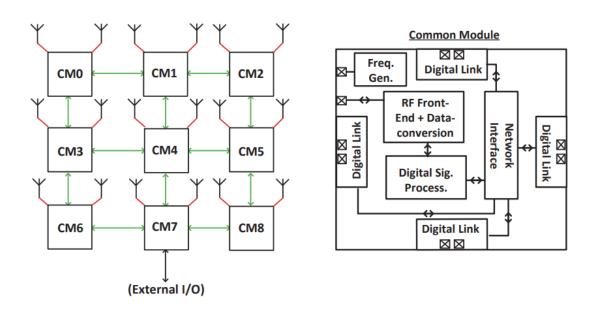

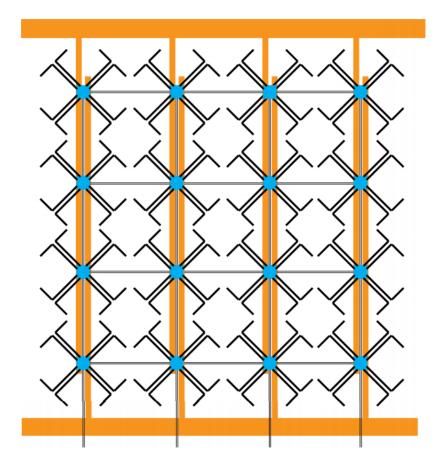

The core concept of our "xG" vision is to utilize the "surfaces" around us for large antenna arrays – eWallpaper. To fulfill what we envisioned, it should be an array of a large number of interconnected and controlled beam forming common module ASICs - with each of these ASICs including programmable RF front-ends, data-conversion, local digital signal processing, high-speed links and clock generation - assembled onto a flexible substrate containing printed antennas and other passive elements (Fig 2.1, 2.2).

Figure 2.1: eWallpaper Block Diagram

Figure 2.2: eWallpaper Vision

### 2.2 Choice of Number of Elements in eWallpaper

In Fig 2.1, for simplicity, it was shown that each ASIC supports two antenna. In reality, each ASIC could support different number of antennas. Therefore, it is necessary for us to understand the trade-offs and find the optimal number of antennas per ASIC first.

As shown in Fig 2.1, each ASIC consists of data-conversion, clock generation, local digital signal processing circuits, and digital high-speed links to enable it to talk to its neighbors. The advantage of having multiple antennas on one chip is that they could share part of the clock generation and local DSP circuits, and the number of serial links in the whole system is reduced, thus simplifying the system, and could possibly reduce the system power consumption. On the other hand, since the spacing between antennas is fixed  $(\lambda/2)$ , the more antennas one chip supports, the further the routing distance from the chip to the antenna. The transmitter on the chip needs to output more power to compensate the higher

routing loss, which might increase the system power consumption. The physical routing could become very messy, if not impossible, when one chip supports a lot of antennas.

Consider a 2D array of N ASICs, each ASIC supports A antennas. From the above discussion, it is clear that the power consumption of all ASICs in the system can be grouped into 3 categories: 1) Local power consumption that doesn't change with the number of antennas per chip; 2) Power used to communicate with other ASICs; 3) Power consumed by RF front-end. We will next establish mathematical equations for the 3 categories respectively.

#### Local power

Local power consumption includes local DSP, clock generation circuits, etc. It doesn't change with the number of antennas per chip. Assume each ASIC consumes  $P_{ov,ASIC}$  in its local DSP and clock generation circuits, then the whole antenna array system consumes  $\frac{N}{A}P_{ov,ASIC}$ . ( $\frac{N}{A}$  is the number of ASICs in the array.)

#### High-speed links

To simplify our analysis, we assume each ASIC uses 4 transceivers to talk to all its nearest neighbors, and each transceiver costs  $P_{link}$ , the whole antenna array system consumes  $4\frac{N}{A}P_{link}$ . It is worth noting that in reality, not all ASICs need to use all 4 transceivers to talk to all its nearest neighbors.

#### RF front-end

Apparently, the total power consumption of RF front-ends is  $NAP_{DC,TX}$ , where  $P_{DC,TX}$  is the DC power consumed by one RF transmitter.  $P_{DC,TX}$  can be divided into two parts: 1) Overhead part, which grows linearly with the number of antennas, but doesn't change with output power. Overhead power  $(P_{ov,ant})$  includes modulation, data conversion, phase shifting, etc.; 2) Power amplifier part, which changes with output power level. Power efficiency of a power amplifier is defined as:

$$\eta = \frac{P_{out,RF}}{P_{DC,PA}} \tag{2.1}$$

Then we could write  $P_{DC,TX}$  in terms of RF output power and PA efficiency:

$$P_{DC,TX} = P_{ov,ant} + \frac{P_{out,RF}}{\eta} \tag{2.2}$$

Similar to cable losses, we could characterize the routing loss from the ASIC to the antenna in terms of decibels per unit length. Here we define the antenna loss to be k dB per half-wavelength, which is equivalent as:

$$P_{radiated} = P_{out,RF} \cdot 10^{-\frac{2kl}{\lambda}} \tag{2.3}$$

where l is the routing distance. Then

$$P_{DC,TX} = P_{ov,ant} + P_{radiated} \cdot 10^{\frac{2kl}{\lambda}} \cdot \frac{1}{\eta}$$

(2.4)

*l* increases with number of antennas each ASIC supports (A). We could approximate the *l* as  $\frac{\sqrt{2}}{4}\lambda\sqrt{A}$ .

As discussed in section 1.2, in the direction the antenna array points, the equivalent isotropically radiated power (EIRP) is  $N^2$  times the radiated energy of one antenna. The radiated power of one antenna is:

$$P_{radiated} = \frac{EIRP}{(N)^2} \tag{2.5}$$

In summary, the total power consumption of RF front-end is:

$$P_{DC,TX} = P_{ov,ant} + \frac{EIRP}{(N)^2} \cdot 10^{\frac{2kl}{\lambda}} \cdot \frac{1}{\eta}$$

$$(2.6)$$

The antenna array's power consumption during RF transmission is:

$$P_{tot} = \frac{N}{A} P_{ov,ASIC} + 4 \frac{N}{A} P_{link} + N P_{ov,ant} + \frac{EIRP}{N} \cdot 10^{\frac{2kl}{\lambda}} \cdot \frac{1}{\eta}$$

(2.7)

It is worth noting that in reality,  $P_{ov,ASIC}$ ,  $P_{ov,ant}$ ,  $P_{link}$  and  $\eta$  all depend on EIRP, N, A, and the chosen circuit architectures. However, we assumed them to be constant to get an insight into how we choose N and A in the first step. By taking partial derivatives with respect to A, the optimal number of antennas per ASIC (A) when number of antennas in the entire array (N) is fixed is given by the following equation:

$$\frac{\sqrt{2}\ln(10)k}{4} \cdot A^{\frac{3}{2}} \cdot 10^{\frac{\sqrt{2}}{2}k\sqrt{A}} = \frac{\eta N^2}{EIRP} (P_{ov,ASIC} + 4P_{link})$$

(2.8)

Recall that  $\frac{EIRP}{N^2}$  is power radiated per antenna,  $\frac{EIRP}{\eta N^2}$  is the power amplifier power assuming zero routing loss. Equation 2.8 matches with our intuition - if the overhead power or high-speed link power consumed in each ASIC is large compared with the PA power, we would prefer to have more antennas per ASIC because it costs a lot of extra power to distribute antennas onto different ASICs. On the other hand, if routing is very lossy (k is big), we would prefer to have fewer antennas per ASIC in order to shorten the routing distance from the ASIC to the antennas.

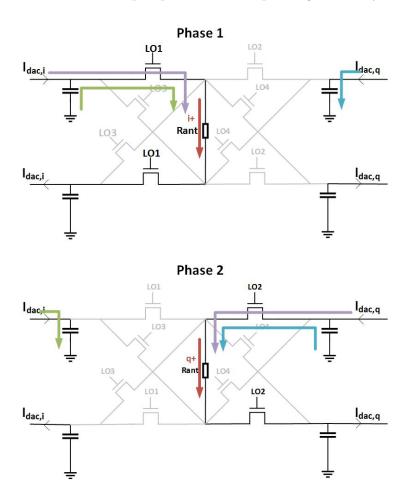

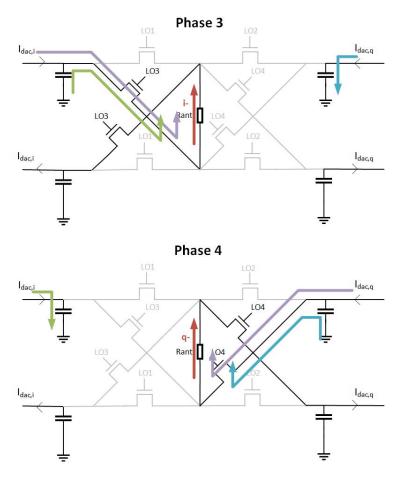

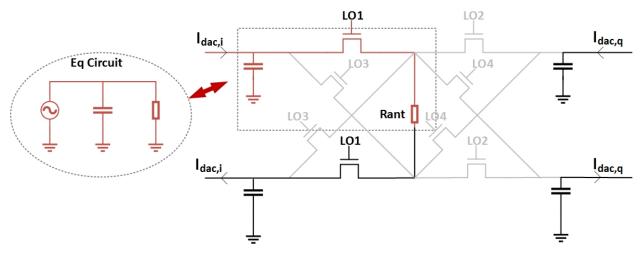

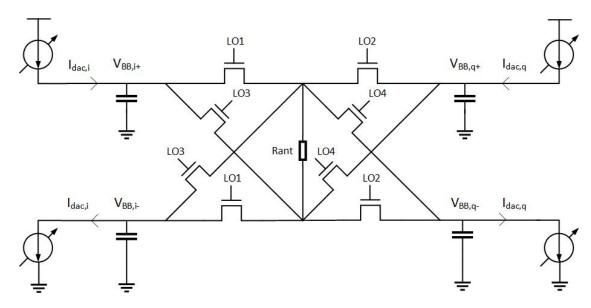

In a real design scenario, if our design goal is to minimize the array power consumption, we could find the best (N, A) pair that minimizes the array power consumption for our targeted output power range. More often, N is chosen based on spatial filtering specs and beamforming algorithms, then we could find the best A that minimizes the array power consumption when N and output power range are given. In most cases, when N is large, having multiple antennas on one ASIC (A > 1) is more power efficient.