## Redesigning Power Systems on a Single Chip Micro Mote with Berkeley Analog Generator Low Dropout Series Regulator Generation

Jackson Paddock

#### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-124 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-124.html

May 14, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Redesigning Power Systems on SCµM with BAG LDO Generation

by Jackson Paddock

#### **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of **Master of Science**, **Plan II**.

Approval for the Report and Comprehensive Examination:

**Committee:**

Professor Kristofer S.J. Pister Research Advisor

(Date)

\*

Professor Ali Niknejad Second Reader

(Date)

#### Abstract

Redesigning Power Systems on a Single Chip Micro Mote with Berkeley Analog Generator Low Dropout Series Regulator Generation

by

Jackson Paddock

Master of Science in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Kristofer S.J. Pister, Chair

The Single Chip Micro Mote (SC $\mu$ M) is a crystal-free radio chip with an on-board CPU developed at UC Berkeley in the Swarm Lab. This chip was designed to function as the brain of an untethered microrobot with no external components other than a power source required. SC $\mu$ M also features an optical programmer so that no cables are even needed to program it. With its size and functionality, SC $\mu$ M has the potential to allow a swarm of microrobots to communicate and perform complex tasks in tandem.

Like every other circuit, SCµM needs power to operate, and one of the most common power regulation circuits is an LDO (low dropout series regulator), which unlike many other DC-DC converter designs, does not require any switching or inductors, which take up a lot of area. This circuit is relatively simple, requiring only a voltage amplifier and one additional transistor, but the challenges in design come from balancing stability, accuracy, and area. The goal of this project was to write a process-independent script that will automatically design such a circuit quickly and accurately in any technology while requiring minimal manual adjustment on the part of the designer. Due to the prevalence of LDOs in integrated circuit chips, the script discussed in this report has many real-world applications. To my parents and my brother, and my friends from BareStage.

Thank you for supporting me in everything I do and making my life that much brighter.

# Contents

| Co            | ontents                                                                                                                                                    | ii                             |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Li            | st of Figures                                                                                                                                              | iii                            |

| $\mathbf{Li}$ | st of Tables                                                                                                                                               | iv                             |

| 1             | Background on SCµM Power Systems         1.1       Power Domains         1.2       Power Consumption                                                       | <b>1</b><br>1<br>1             |

| 2             | LDO Design with BAG2.1Berkeley Analog Generator (BAG)2.2LDO Design2.3Script Design Approach2.4Comparison to Hand-Designed LDOs2.5Approximations and Errors | <b>4</b><br>4<br>8<br>14<br>25 |

| 3             | Conclusion         3.1       Future Work                                                                                                                   | <b>31</b><br>31                |

| Bi            | ibliography                                                                                                                                                | 33                             |

| $\mathbf{A}$  | BAG Setup                                                                                                                                                  | 34                             |

| в             | Example Characterization Input YAML File                                                                                                                   | 39                             |

| С             | Example Design Script Input YAML File                                                                                                                      | 43                             |

| D             | LDO Design Script                                                                                                                                          | 45                             |

| $\mathbf{E}$  | VDDD Tap (SCµM)                                                                                                                                            | 60                             |

# List of Figures

| 1.1  | LDO with PMOS series device.                                                           | 2  |

|------|----------------------------------------------------------------------------------------|----|

| 2.1  | Block diagram of LDO feedback loop for a PMOS series device                            | 6  |

| 2.2  | Block diagram of LDO power supply gain loop for a PMOS series device                   | 6  |

| 2.3  | Small signal model for LDO load regulation calculation at low frequency with a         |    |

|      | PMOS series device.                                                                    | 7  |

| 2.4  | LDO with 5T differential amplifier topology and PMOS series device                     | 8  |

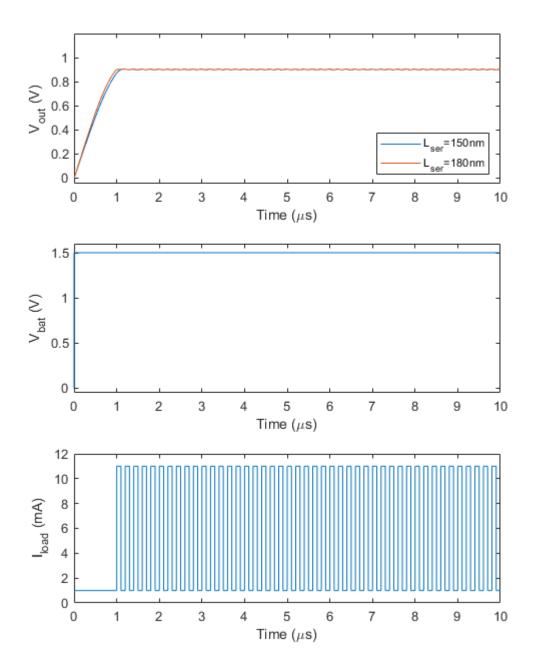

| 2.5  | SCµM 3C auxiliary and digital LDO transient response at 5MHz.                          | 15 |

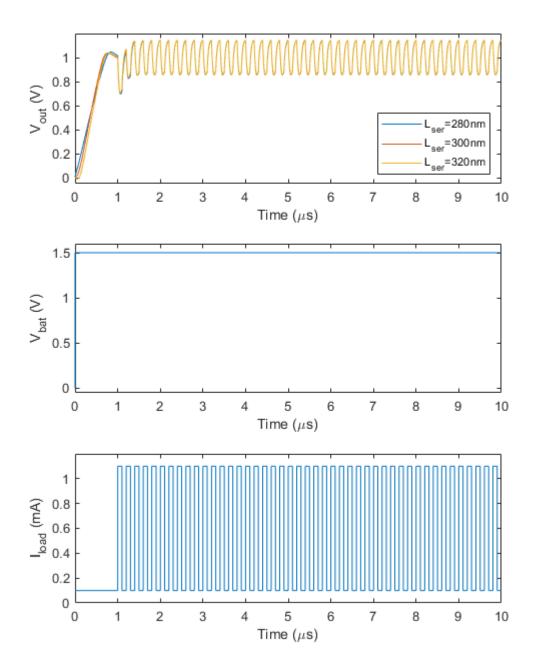

| 2.6  | SCµM generated LDO transient for amplifier channel length of 500nm at 5MHz.            | 19 |

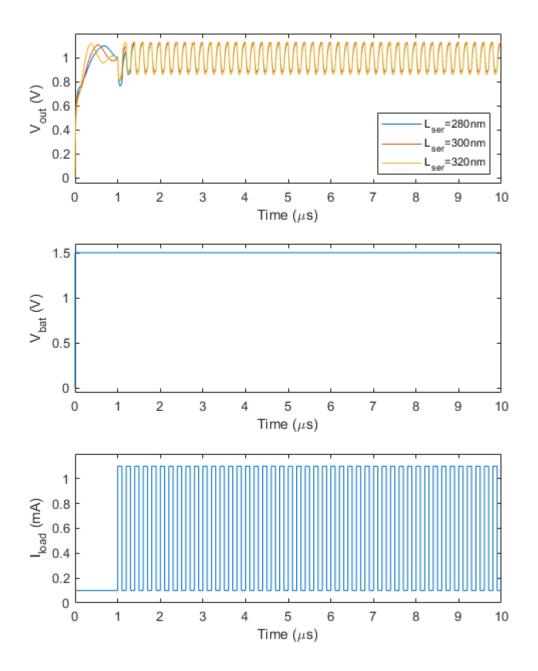

| 2.7  | SCµM generated LDO transient for amplifier channel length of 1µm at 5MHz.              | 21 |

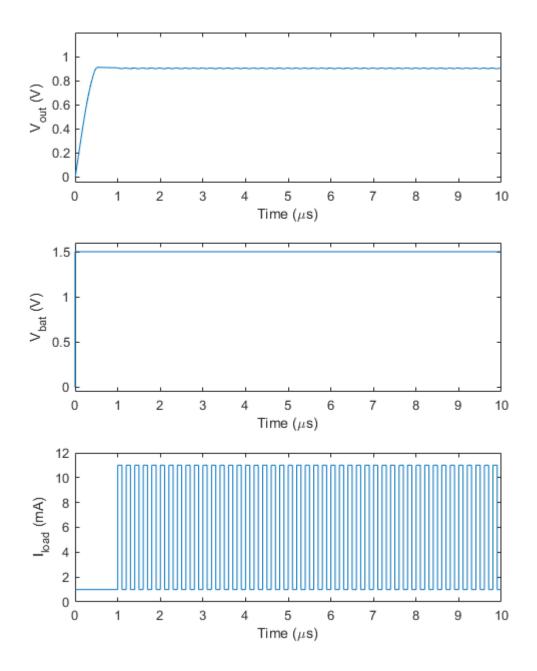

| 2.8  | $SC\mu M$ generated LDO transient for amplifier channel length of $5\mu m$ at $5MHz$ . | 23 |

| 2.9  | EE290C hand-designed LDO transient response at 5MHz.                                   | 24 |

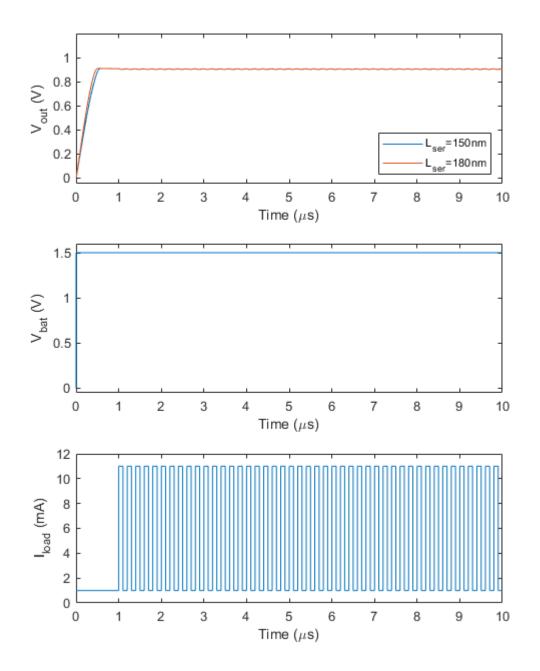

| 2.10 | EE290C generated LDO transient for amplifier channel length of 400nm at 5MHz.          | 27 |

| 2.11 | EE290C generated LDO transient for amplifier channel length of 1 $\mu$ m at 5MHz.      | 29 |

| E.1  | VDDD tap device proposed layout area.                                                  | 61 |

|      | SCµM Digital LDO schematic with NMOS tap device.                                       | 62 |

# List of Tables

| 1.1  | SCµM 3C current draw in different operating states [3]                              | 1  |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | $SC\mu M$ power domains [2]                                                         | 2  |

| 2.1  | LDO design script input parameters.                                                 | 9  |

| 2.2  | LDO design script output dictionary keys.                                           | 9  |

| 2.3  | SCµM 3C auxiliary and digital LDO performance.                                      | 14 |

| 2.4  | $SC\mu M$ generated LDO input parameters for amplifier channel length of 500nm.     | 18 |

| 2.5  | $SC\mu M$ generated LDO performance for amplifier channel length of 500nm           | 18 |

| 2.6  | $SC\mu M$ generated LDO input parameters for amplifier channel length of $1\mu m$ . | 20 |

| 2.7  | SCµM generated LDO performance for amplifier channel length of 1µm                  | 20 |

| 2.8  | $SC\mu M$ generated LDO input parameters for amplifier channel length of 5 $\mu m$  | 22 |

| 2.9  | SCµM generated LDO performance for amplifier channel length of 5µm                  | 22 |

| 2.10 | EE290C LDO performance with 10mA load current                                       | 25 |

| 2.11 | EE290C generated LDO input parameters for amplifier channel length of 400nm.        | 26 |

| 2.12 | EE290C generated LDO performance for amplifier channel length of 400nm              | 26 |

| 2.13 | EE290C generated LDO input parameters for amplifier channel length of $1\mu m$ .    | 28 |

| 2.14 | EE290C generated LDO performance for amplifier channel length of 1µm                | 28 |

#### Acknowledgments

I would like to offer many thanks to my advisor, Professor Kristofer Pister for guiding me through this program and always having more confidence in me than I at times have have in myself. Without him, I would not be where I am today and for that I would like to offer my utmost gratitude.

Thank you to Lydia Lee, who has been my mentor on this project and has always given me the guidance I needed when I was unsure of how to proceed with my work. Thank you for your endless support and patience.

Thank you to Alex Moreno, Austin Patel, David Burnett, Fil Maksimovic, and the rest of the SCµM team for all the advice and knowledge you have given me in the short time I've worked with you.

## Chapter 1

# Background on $SC\mu M$ Power Systems

## 1.1 Power Domains

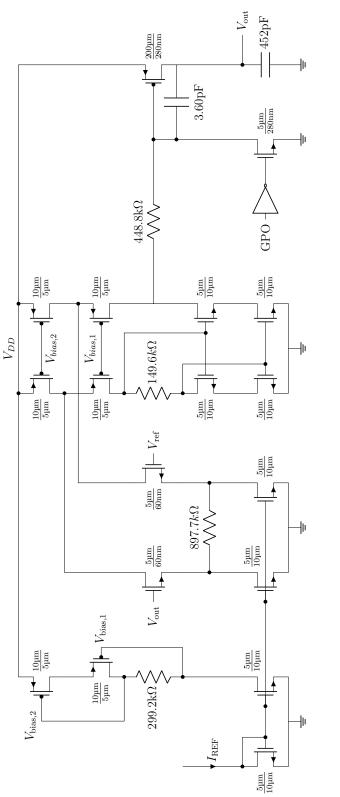

SCµM has eight power domains as listed in Table 1.2, each of which is supplied by an LDO connected to the off-chip battery voltage. There are also four different bandgap references, inside the blocks for the digital LDO, optical/alwayson, radio divider, and radio LO. Each of these LDOs is connected to the battery voltage for power, which is nominally at 1.5V, but can be brought down to 1.2V. The chip also uses an external VDDIO to supply the level shifters in the pad ring and GPIO to connect to chip-level inputs and outputs.

## 1.2 Power Consumption

The power consumption of the LDOs themselves are listed in Table 1.2. Each LDO reference voltage is set by a constant bandgap reference current running through a tunable resistor. The resistor for each LDO is the same and can be tuned to achieve discrete voltages between 0.8V and 1.2V. With a reference current of 500nA or 1µA, the resistor ranges between 950k $\Omega$  and 1.7M $\Omega$ . The LDOs that consume the most power in the amplifier, the Always On and Sensor ADC LDOs, also have the largest biasing networks, which are partially for the enable/disable bits that control whether or not the LDOs supply power to their loads.

| State         | Clock Rate | Average Current Consumption |  |  |  |  |

|---------------|------------|-----------------------------|--|--|--|--|

| Normal        | 5MHz       | 350µA                       |  |  |  |  |

| Radio on 5MHz |            | 1.6mA                       |  |  |  |  |

| Low power     | 78kHz      | 200µA                       |  |  |  |  |

Table 1.1: SCµM 3C current draw in different operating states [3].

<sup>&</sup>lt;sup>1</sup>Better performance was seen in practice with a slightly higher reference voltage.

| Domain         | Operating Voltage |            | Amplifier |        |                 | Sub-Blocks |                             |

|----------------|-------------------|------------|-----------|--------|-----------------|------------|-----------------------------|

|                |                   |            |           | Qui    | iescent Current |            |                             |

|                | Min               | Nom        | Max       | Min    | Nom             | Max        |                             |

| Digital (VDDD) |                   | 1V         |           |        | 4.763µA         |            | Cortex, RAM                 |

| Auxiliary      |                   | 1V         |           |        | 4.763µA         |            | Auxiliary Digital Circuits, |

|                |                   |            |           |        |                 |            | GPIO Levelshifters          |

| Always On      | 0.8V              |            | 1.2V      | 7.12µA |                 | 7.24µA     | Osc. DAC,                   |

|                |                   |            |           |        |                 |            | Optical Receiver            |

| Sensor ADC     | 0.8V              |            | 1.2V      | 7.16µA |                 | 7.16µA     | ADC                         |

| Radio IF       | 0.8V              | $0.8V^{1}$ | 1.2V      | 4.85µA | 4.85µA          | 5.32µA     | Radio IF                    |

| Radio LO       |                   | 0.8V       |           |        | 5.98µA          |            | Radio LO                    |

| Radio PA       |                   | 0.8V       |           |        | 4.84µA          |            | Radio TX PA                 |

| Radio Divider  |                   | 0.8V       |           |        | 760nA           |            | Radio Divider               |

Table 1.2: SCµM power domains [2].

Figure 1.1: LDO with PMOS series device.

Combined, the regulators consume  $40.5\mu$ A, which is more than 10% and 20% of the total operating current in the normal and low power states respectively (Table 1.1). Even in the radio on state, this current is not negligible. Disabling some LDOs may reduce this current consumption, but the LDO quiescent current is still high compared to the results seen in Section 2.4.

The dominant pole for the radio's IF, LO, and PA LDOs was placed at the LDO output to reduce the high frequency noise at the output and accommodate the sensitivity of the attached circuits. The rest of the LDOs have the dominant pole at the output of the amplifier. A dominant amplifier pole can lead to lower current consumption as discussed in Sections 2.2 and 2.3. The radio divider LDO does clearly have lower current than the radio LDOs with dominant output poles, but there is a lot of room for improvement with the other LDOs in terms of power efficiency. The current consumption of the digital, auxiliary, always on, and ADC LDOs should be much closer to that of the radio divider with the right design, if not even lower. With the varying requirements for nominal output voltages and currents on each LDO, and the sensitivity of the radio LDOs excepting the divider LDO, the Berkeley Analog Generator (BAG), discussed in the next chapter, becomes a useful tool for efficiently reducing power consumption and catering to the specifications of each LDO.

For SC $\mu$ M, reducing leakage current is a very important goal. For any application where the power supply is coming from a battery and not a lab bench, any reduction in power will allow SC $\mu$ M to run for a longer time, increasing the scope of potential applications.

## Chapter 2

## LDO Design with BAG

### 2.1 Berkeley Analog Generator (BAG)

The Berkeley Analog Generator (BAG) [1] is in infrastructure that supports a collection of process-independent design scripts which, when given a set of input parameters, will automatically design a circuit to meet those parameters down to the transistor level. These scripts can make the design process of a circuit block significantly faster and have the potential to design more efficient circuit blocks than would practically be created by hand. This chapter discusses a BAG script in BAG2 created to design an LDO optimized for low power consumption in any process, and potential applications for these designs.

This chapter describes the process the design script in Appendix D uses to generate LDOs and provides examples of its results. The LDO design script has been validated in both the TSMC 65nm LP and TSMC 28nm processes. The BAG framework and scripts used are process-independent, but the process information for the technologies used is protected under nondisclosure agreements. All process-specific information is located on private servers hosted by the Berkeley Wireless Research Center (BWRC). The process information for TSMC 65nm LP and TSMC 28nm is included in the library paths of the respective BAG workspace repositories described in Appendix A. For non-BWRC readers, a template for establishing the correct hooks can be found at:

https://github.com/ucb-art/BAG2\_cds\_ff\_mpt.

### 2.2 LDO Design

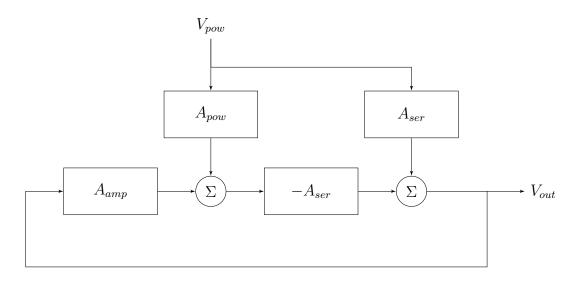

The performance parameters this report uses to design an LDO are the static output error, load regulation, noise rejection, and stability. Physical parameters used to determine transistor sizings and bias points are the load voltage, load current draw, load capacitance, power supply, and amplifier reference current. For this report and the associated design script, a 5T amplifier topology with an NMOS input pair was used. All diagrams in this section and LDOs designed with BAG use a PMOS series device. Although an NMOS series device is possible, it may be difficult to keep in saturation unless the output common mode of the amplifier is near the supply voltage. This issue is discussed in more detail in Section 2.3.

In this circuit, the two main poles are at the output of the amplifier and at the output of the LDO. Although there are other capacitors that contribute to the frequency response of the LDO, for the purposes of this section the amplifier and series device are assumed to only have a single pole each. There is also a zero created by the capacitor (a combination of explicit and parasitic) between the amplifier output of the amplifier and the LDO output with the effective resistance it sees at  $1/g_{m,ser}$  considered in this section. The zero may affect the phase margin at higher values of  $C_{amp}$  or higher gain from the series device, but the phase margin, derived from the loop gain in Figure 2.1 and given by Equation 2.2, is primarily determined by how far away the amplier and LDO output poles are. The unity gain frequency  $\omega_0$  of the loop gain in Equation 2.1 is affected by the DC gain as well as the poles and zeros.

$$LoopGain = \frac{A_{amp}A_{ser}(1+\frac{j\omega}{\omega_z})}{(1+\frac{j\omega}{\omega_{amp}})(1+\frac{j\omega}{\omega_{out}})}$$

(2.1)

$$PM = 180^{\circ} + \arctan\left(\frac{\omega_0}{\omega_z}\right) - \arctan\left(\frac{\omega_0}{\omega_{amp}}\right) - \arctan\left(\frac{\omega_0}{\omega_{out}}\right)$$

(2.2)

An unknown load capacitance can pose challenges for ensuring stability, for example if the load capacitance is higher than expected and the amplifier pole is dominant, the poles in Equation 2.1 move closer together, leading to instability if they become too close. This problem and possible solutions are discussed in more detail in Section 2.3.

After choosing a bias point for the gate of the series device (any voltage that keeps the transistor in saturation), the bias points for a 5T differential amplifier topology as shown in Figure 2.4 are entirely determined assuming a constant V<sup>\*</sup> for the devices in the amplifier. The BAG LDO design script makes this assumption to simplify the choices it makes, but setting the amplifier input pair's V<sup>\*</sup> higher than the amplifier load pair's V<sup>\*</sup> improves noise and matching.

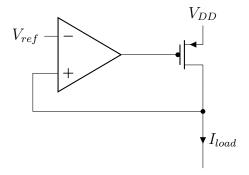

Modeling the circuit as a block diagram like in Figure 2.1, the relationship between the reference and the output of the LDO with a PMOS series is given by Equation 2.3, and the corresponding static error, expressed as a unitless fraction between the difference between the reference and output voltages and the reference voltage throughout this report, is given by Equation 2.4 where  $A_{ser} = g_{m,ser}r_{o,ser} > 0$ .

$$A_{amp}(-A_{ser})(V_{out} - V_{ref}) = V_{out}$$

$$\frac{V_{out}}{V_{ref}} = \frac{A_{amp}A_{ser}}{A_{amp}A_{ser} + 1}$$

(2.3)

$$\mathcal{E}_s = 1 - \frac{V_{out}}{V_{ref}} = \frac{1}{A_{amp}A_{ser} + 1} \tag{2.4}$$

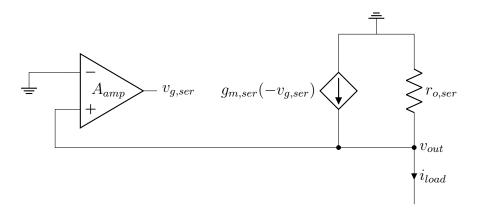

Figure 2.1: Block diagram of LDO feedback loop for a PMOS series device.

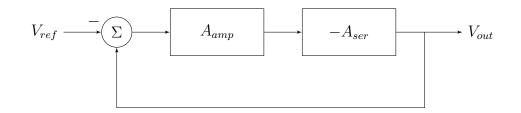

Figure 2.2: Block diagram of LDO power supply gain loop for a PMOS series device.

For high amplifier and series device gains, the static error in Equation 2.4 will be very small and the actual static error will be dominated by the device offsets of the amplifier devices. The LDO design script in Appendix D does not account for this in the approximations it makes.

Modifying Figure 2.1 slightly to find the gain from the power supply to the output through both the amplifier and the series device produces Figure 2.2, which in combination with Equation 2.3 can be used to find the PSRR as in Equation 2.5. For a 5T differential amplifier,  $A_{pow}$  approaches 1 as the tail resistance increases.

$$-A_{ser}(A_{amp}V_{out} + A_{pow}V_{pow}) + A_{ser}V_{pow} = V_{out}$$

$$PSRR = \frac{V_{pow}}{V_{out}} \cdot \frac{V_{out}}{V_{ref}} = \frac{A_{amp}A_{ser} + 1}{A_{ser}(1 - A_{pow})} \cdot \frac{A_{amp}A_{ser}}{A_{amp}A_{ser} + 1} = \frac{A_{amp}}{1 - A_{pow}}$$

(2.5)

Considering the amplifier output pole as a part of  $A_{amp}$  and the LDO output pole as a part of  $A_{ser}$  and that  $A_{pow}$  is relatively independent of frequency near the amplifier and

Figure 2.3: Small signal model for LDO load regulation calculation at low frequency with a PMOS series device.

output poles, the dominant pole and bandwidth of the PSRR equation is the amplifier output pole.

To calculate load regulation for a peak load current variation of 10% from the nominal value, which is expressed as a unitless fraction between the resulting peak to peak regulator output voltage and the average regulator output voltage, the small signal model with an abstracted amplifier in Figure 2.3 provides Equation 2.6.

$$v_{g,ser} = A_{amp}v_{out}$$

$$\frac{v_{out}}{r_{o,ser}} = i_{load} - g_m v_{g,ser} = i_{load} - g_m A_{amp}v_{out}$$

$$v_{out} = \frac{r_{o,ser}}{1 + A_{amp}A_{ser}}i_{load}$$

$$LoadReg = \frac{\Delta v_{out}}{V_{out}} = \frac{\Delta i_{load}r_{o,ser}}{V_{out}(1 + A_{amp}A_{ser})} = \frac{0.2 I_{load}r_{o,ser}}{V_{out}(1 + A_{amp}A_{ser})}$$

(2.6)

From these equations, a higher amplifier and series device gain improves static error, PSRR, and load regulation. A lower series device output resistance also improves the load regulation, but shorter channel devices also have a lower gain. For  $A_{amp}A_{ser} >> 1$ , the load regulation equation becomes dependent on  $1/g_{m,ser}$ . A shorter channel length also decreases the capacitance at the load of the amplifier, bringing the PSRR bandwidth higher. Because the amplifier pole sees the output resistance of the amplifier, larger devices and smaller effective widths will decrease the amplifier pole frequency and PSRR bandwidth, and decrease the power consumed in the amplifier. The PSRR will also be increased by the higher gain from longer channel devices in the amplifier pole frequency and PSRR bandwidth, and larger effective widths will increase the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier pole frequency and PSRR bandwidth, and increase the power consumed in the amplifier. The PSRR will also decrease with shorter channel amplifier devices.

Figure 2.4: LDO with 5T differential amplifier topology and PMOS series device.

### 2.3 Script Design Approach

The file regulator\_ldo\_series.py defines bag2\_analog\_\_regulator\_ldo\_series\_dsn as a subclass of the DesignModule class, which given a set of input parameters described in Table 2.1 will design an LDO with either an n-type or p-type series device and a 5T differential amplifier with an n-type input pair for the amplifier as shown in Figure 2.4. See Appendix C for an example input YAML file, and Appendix D for the script itself. Although this script has the option of using an NMOS series device, using a PMOS is recommended. Unless the supply voltage is high or the device thresholds are very low, using an NMOS series device may be difficult. The minimum series device gate voltage to keep the device out of the subthreshold region is the device's threshold voltage plus the regulator output voltage, which may need to exceed the supply voltage to provide the nominal load current. A different amplifier topology with a greater output swing would be more suited to using an NMOS series device.

The inputs to this script are listed with descriptions in Table 2.1. The output is a single dictionary, containing more dictionaries listed in Table 2.2 of the component sizes of the particular design.

The first part of the LDO that the code designs is the series device. Because the current is known, the drain and source voltages are known (the supply voltage and the output voltage, depending on what type of device it is), and the channel length is known, the only unknowns are the device's effective width and gate voltage. By setting the gate voltage at some value between the bounds that keep all devices in saturation, the effective width is easily determined by a ratio of the total load current to the device current at the base width. Since the transistor data is simulated with a fixed finger width, this code assumes that the

| Parameter     | Description                                                              |

|---------------|--------------------------------------------------------------------------|

| specfile_dict | Transistor database spec file names for each device                      |

| ser_type      | n or p for type of series device                                         |

| vdd           | Supply voltage in volts                                                  |

| vout          | Reference voltage to regulate the output to                              |

| iload         | Bias current of series device, in amperes                                |

| iref          | Reference current for amplifier biasing, in amperes                      |

| iampmax       | Maximum amplifier current, in amperes                                    |

| cload         | Load capacitance from the output of the LDO to ground                    |

| cdecap        | Maximum additional capacitance added to circuit                          |

| rsource       | Resistance from the power supply, in ohms                                |

| err           | Maximum percent static error at output (as decimal)                      |

| psrr          | Minimum power supply rejection ratio (dB, 20*log10(dVdd/dVout))          |

| psrr_fbw      | Minimum bandwidth for power supply rejection roll-off                    |

| pm            | Minimum phase margin for the large feedback loop, in degrees             |

| loadreg       | Maximum absolute change in output voltage given change in output current |

| load_pole     | True to ensure dominant pole is at the<br>regulator output               |

| v_res         | Resolution of voltage bias point sweeps, in volts                        |

| sim_env       | Simulation environment                                                   |

| l_dict        | Transistor channel length dictionary                                     |

| th_dict       | Transistor flavor dictionary                                             |

Table 2.1: LDO design script input parameters.

| Parameter | Description                                                       |

|-----------|-------------------------------------------------------------------|

| w_dict    | Dictionary of transistor channel width per finger for each device |

| l_dict    | Dictionary of transistor channel length for each device           |

| nf_dict   | Dictionary of transistor number of fingers for each device        |

| th_dict   | Dictionary of transistor flavor for each device                   |

| type_dict | Dictionary of transistor type, n or p, for each device            |

| cap_dict  | Dictionary of values of $C_{amp}$ and $C_{load}$                  |

Table 2.2: LDO design script output dictionary keys.

device currents, capacitances, and transconductances scale linearly with increased effective width. Additionally, without any information on minimum or maximum finger widths of the devices used, this code assumes that the base finger width is the minimum value, and twice that width is the maximum finger width. This assumption also ensures that any effective width greater than the minimum finger width is possible, with accuracy of device matching only limited to the how well the model matches the devices and what scale of resolution is possible for fabrication. The class function resize\_op(op,wm) takes in a dictionary of transistor parameters and scales them up by the factor wm that the effective width increases by. In pseudocode, this first layer of the design is:

best LDO design  $\leftarrow$  None,  $I_{amp,best} = \infty$ for  $V_{g,ser}$  where  $M_{ser}$  in saturation do size  $M_{ser}$  for  $I_{load}$ design amplifier(specs) if  $I_{amp,new} < I_{amp,best}$  then best LDO design  $\leftarrow$  new LDO design,  $I_{amp,new}$ end if end for

return best LDO design

To simplify the calculations, all amplifier stage devices ( $M_{load,p}$ ,  $M_{load,n}$ ,  $M_{in,p}$ ,  $M_{in,n}$ , and  $M_{tail}$ ) are assumed to have the same V<sup>\*</sup>. With the series device gate voltage set, the output common mode voltage of the amplifier is also set. Because the gate and drain of the amplifier load pair are tied together on  $M_{load,p}$ , all bias voltages for the amplifier devices are set by V<sup>\*</sup>. The only parameter that is not fixed for these devices at this point is the effective width, which will be determined later.

The drains of  $M_{in,p}$  and  $M_{in,n}$  are tied to the series device gate voltage as previously set in the sweep of the series device gate, and the gates are tied to  $V_{ref}$ . V\* is already determined for the devices in this amplifier stage, so a sweep of the input pair source voltage will determine what value will best match their V\* with the load devices.

The only remaining unknown bias point is the tail device gate, which can be determined through a sweep to match V<sup>\*</sup> as with the input devices. Anticipating that an LDO produced by this script will be fabricated and therefore require layout, this script also sizes  $M_{mir}$  to ensure that they have the same finger width to promote better matching between devices. Also with layout in mind, each device is later sized to have an even number of fingers so a common centroid pattern is possible. In the case where the minimum number of fingers and  $M_{tail}$  is at its minimum, but the fingers will not fit in a single row given the area prescribed for the LDO on a chip, the script can easily be modified to set a new guaranteed factor of the number of fingers for a device. For the  $M_{tail}$ , line 156 in the code in Appendix D, which guarantees an even number of fingers, can be changed from:

```

156 nf_tail = int(2*max(((2*op_load['ibias'])//Id_tail)+1,((2*op_in['ibias'

])//Id_tail)+1))

```

to the following to guarantee that the number of fingers is a multiple of four:

```

156 nf_tail = int(4*max(((2*op_load['ibias'])//Id_tail)+1,((2*op_in['ibias'

])//Id_tail)+1))

```

For  $M_{mir}$ , lines 147 through 149 can be changed from:

```

147 m_mir = iref/(2*op_mir['ibias'])

148 wm_mir = (m_mir%1 + 1)

149 nf_mir = 2*int(m_mir)

```

to the following to guarantee that the number of fingers is a multiple of four:

```

147 m_mir = iref/(4*op_mir['ibias'])

148 wm_mir = (m_mir%1 + 1)

149 nf_mir = 4*int(m_mir)

```

For  $M_{\text{load},p}$ ,  $M_{\text{load},n}$ ,  $M_{\text{in},p}$ , and  $M_{\text{in},n}$ , the guaranteed factor can be modified similarly to line 149 on lines 163 and 167 for the load devices and input devices respectively, additionally changing the multipliers within the max() function in line 153 from '2' to the desired factors. While these modifications will always produce a potential sizing if the load, input, or tail device factors are changed, increasing the guaranteed factor for the number of mirror device fingers may increase the total current at a given bias point past the value of *iref*, and that bias point will be ignored.

With the bias current *iref* as an input, the effective width of  $M_{mir}$  is uniquely determined (as long as *iref* is larger than twice the base finger width current at the bias point). All of the amplifier devices excluding the mirror are then set at minimum effective width based on which device has the largest base current, accounting for the fact that the tail device sinks the current of both input and load devices. Up to this point, the amplifier design in pseudocode (with ranges on the for loops to keep devices in saturation) is:

```

V^*_{amp} \leftarrow V^*_{load}

for V \in [0, V_{ref} - V_{th,in}] do

if V_{in}^* = V_{amp}^* then

V_{s,in} \leftarrow V

end if

end for

for V \in [V_{th,tail}, V_{s,in} + V_{th,tail}] do

if V_{in}^* = V_{amp}^* then

V_{g,tail} \leftarrow V

end if

end for

size M_{mir} for I_{ref}

W_{finger,tail} \leftarrow W_{finger,mir}

I_{tail} \leftarrow 2 * max(I_{tail, finger}, 2 * I_{in, finger}, 2 * I_{load, finger})

size M_{tail} for I_{tail}

size M_{in}, M_{load} for I_{tail}/2

```

The final part of the amplifier design checks that specs are met and adds capacitors to make the feedback loop stable. The specs that are most significantly affected by adding capacitors and sizing up the amplifier devices are the phase margin and the power supply rejection ratio bandwidth. There are two places to put the dominant pole in this circuit: at the output of the amplifier and at the output of the LDO. The primary advantages of placing the dominant pole at the output of the amplifier are low power and a lower value of explicit capacitance added to the circuit, which can take up a lot of space on a chip. Power consumption is generally lower with a dominant amplifier pole because the amplifier output resistance is highest with minimally sized devices, and a higher resistance means a lower pole, even with less capacitance than may be necessary for a dominant pole at the output of the LDO. The disadvantages of a dominant amplifier pole are that the PSRR bandwidth follows this pole closely, so a lower pole that is necessary for stability kills higher frequency noise rejection, and if the estimate of the LDO load capacitance is too low, the poles will be closer than expected and may lead to instability. In case the LDO load capacitance is unknown, one of the inputs to the design script load\_pole ensures that the dominant pole is placed at the LDO output and the attempt to set it at the amplifier output is skipped.

If a load pole at the amplifier output is allowed, the script begins by checking if the LDO meets the specs without any additional capacitance, then increases the capacitor tied to the amplifier output until either all specs are met, the PSRR bandwidth drops below the minimum spec, or the maximum allowable capacitance is added. In the case where the spec is not met or the dominant pole is placed at the output of the LDO, the script adds the maximum allowable capacitance to the LDO output to bring that pole as low as possible. This has little effect on the PSRR bandwidth, which is still tied to the amplifier output pole. If the phase margin and PSRR bandwidth are still too low, the script begins increasing the effective width of the amplifier devices to decrease the output resistance and drive the amplifier pole higher. This excludes the tail mirror device because the reference current it takes is fixed and does not affect the pole.

With the tail finger width fixed so it matches the reference current mirror, the only way to increase its effective width is by adding fingers. This script does so two fingers at a time to promote symmetry in layout as mentioned before. If the desired factor for the tail device is a number other than two, changing the number of fingers added to the number of tail fingers nf\_tail on line 237 to that factor will ensure the proper number of fingers. At this point in the loop, the tail device is resized but the amplifier load and input devices also have to be resized relative to the tail. Simply adding fingers to these devices will not be enough to match their currents because they don't necessarily have the same finger widths as the tail or each other, so they are resized relative to the new tail bias current. This process continues until either a solution is found, or the maximum amplifier current is exceeded. The pseudocode for upsizing transistors and ensuring stability is:

if specs met then return amplifier design end if if not load\_pole then  $C_{load} \leftarrow 0$ for  $C_{amp} < \max \operatorname{decap} \operatorname{do}$ if specs met then return amplifier design end if end for end if  $C_{load} \leftarrow C_{max}$  $C_{amp} \leftarrow 0$ while  $I_{tail} < I_{max}$  do if specs met then return amplifier design end if  $nf_tail \leftarrow nf_tail + 2$ size  $M_{in}$ ,  $M_{load}$  for  $I_{tail}/2$ end while

return no design

Once the amplifier at a bias point is designed, the function op\_compare(op1,op2) is called in meet\_spec(\*\*params) to determine whether to keep or ignore the current iteration. This function is set to compare only the amplifier bias current but can be changed to optimize for any other performance parameter specified in the design input file. Line 335 also sets the maximum amplifier bias current to the bias current of the best amplifier design found up to that point. This line may be slightly redundant considering that the previous line calling op\_compare(op1,op2) also compares the amplifier bias currents and will always choose the new design because of the assignment in line 335, but calling op\_compare(op1,op2) allows for the optimized parameter to be swapped out more easily, and the assignment of the maximum bias current may shorten the run time of the while loop on line 213 in the amplifier design if the bias current is already greater than will be considered for the final design.

This script utilizes the LTICircuit class as defined in BAG\_framework/data/lti.py, which can use the transistor parameters obtained for the design and solve the small signal equations of the circuit model when the nodes each component connects to are defined. The resulting circuit model can be used to calculate the transfer function between any two nodes with voltage or current inputs, giving the gain and bandwidth of a particular transfer function. Using this class to calculate the circuit performance parameters is advantageous because it allows for more rigorous calculations of small signal circuits (i.e. including all parasitic capacitors) and can easily be used to model more complicated amplifier topologies not require a license to use as other circuit modeling software like Cadence Virtuoso does.

| Reference Voltage | 1V              |

|-------------------|-----------------|

| Load Current      | 1mA             |

| Static Error      | -2.756m         |

| Amp Current       | 4.763µA         |

| Phase Margin      | 85.62°          |

| PSRR              | 43.87dB         |

| PSRR Bandwidth    | 461.9Hz         |

| Load Regulation   | 96.50µ          |

| Amp Capacitor     | 3.60pF          |

| Load Capacitor    | 452pF           |

| Total Gate Area   | $756.6 \mu m^2$ |

Table 2.3: SCµM 3C auxiliary and digital LDO performance.

### 2.4 Comparison to Hand-Designed LDOs

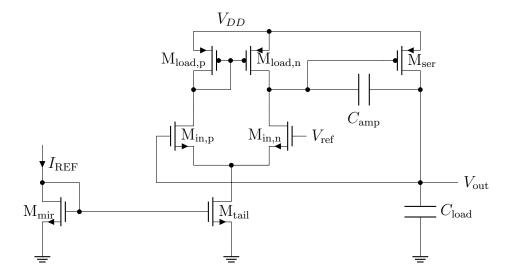

#### SCµM Digital and Auxiliary LDOs

SCµM is generally operated with an auxiliary and digital LDO reference and output voltage of 1V and a battery voltage of 1.5V. Both of these LDOs, which use the same schematic, have an PMOS series device. Table 1.1 lists the three main operating points of SCµM and their total operating current draws. With these numbers, a reasonable nominal current to design for seems to be about 1mA based on the increase in current when the radio is on.

The load capacitance of both the auxiliary and digital LDOs on SC $\mu$ M contributed by the layout and other circuits is unknown. For this application, PSRR bandwidth is not as important because the regulator loads are entirely digital, so the dominant pole will be placed at the output of the amplifier as it is on SC $\mu$ M 3C. With this in mind, what is necessary to generate a viable LDO for SC $\mu$ M is an upper bound on that unknown load capacitance. For this thesis, the assumed load capacitance value will be 100pF. If a better estimate is determined through extraction or measurement, the BAG design script can be rerun with a higher load capacitance by changing a single line in the input YAML file.

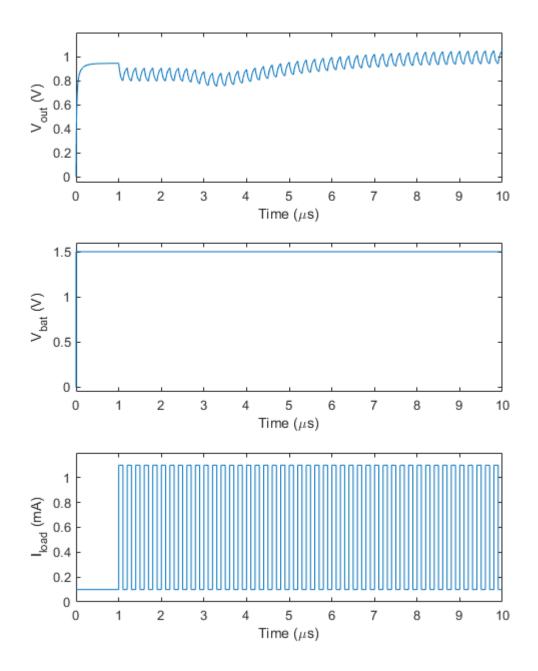

Tables 2.4 through 2.9 and Figures 2.6 through 2.8 show the inputs (in the format the design script would read them) and respective output performances of the LDO design script for various series device and amplifier channel lengths. There is a slight variation between the performance calculated by the script and the simulated performance, but generally the two are fairly close. The biggest issue with these designs is the bias points of the amplifier. The script uses the function estimate\_vth(db,is\_nch,lch,vgs,vbs) to estimate the threshold voltage of a device given a bias point, but is not very accurate. This function uses the the device's V\* and  $V_{gs}$  to estimate the threshold, assuming a quadratic model for vgs/lch <  $1V/\mu m$  and a linear model otherwise, which varies dramatically as  $V_{gs}$  changes. Due to the

Figure 2.5: SCµM 3C auxiliary and digital LDO transient response at 5MHz.

inaccuracies in the function it is difficult to ensure that all devices are close enough to the threshold to achieve high gain and low current consumption but are still in saturation. Even using the estimated threshold of the amplifier load (which is higher than the series device for the designs in the tables because of the channel length), the PMOS devices generally have a lower V\* than the NMOS, so the load devices can be in saturation with the input and tail devices pushed subthreshold. Of the LDOs listed in Tables 2.4 through 2.9, the designs with all devices in saturation are the ones with an amplifier channel length of 5µm. The remaining designs with amplifier channel lengths of 500nm and 1µm have the input and tail devices subthreshold (as determined by simulation), as well as the load devices for the designs with 280nm channel length series devices. On average, the subthreshold devices only had  $V_{gs}$  lower than the threshold by about 71mV, with the greatest difference being about 150mV.

The 5µm amplifier channel length designs are each better than the auxiliary and digital LDOs currently on SCµM for each parameter, with the exception of the phase margin, PSRR bandwidth, and peak to peak of the transient plots at 5MHz. Although the phase margin is slightly lower for these designs, they are all still well within the bounds for stability. The PSRR bandwidths are low, especially with larger series devices, but the PSRR bandwidth of SCµM is also only 461.9Hz, less than twice the PSRR bandwidth for the design with a 280nm series device channel length. Given that this script was designed to optimize for power, this design was very successful. Replacing the auxiliary and digital LDOs on SCµM with the 5µm amplifier channel length and 280nm series device channel length design would decrease the amplifier current consumption by 94.8% from 4.763µA to 248.1nA at a load current draw of 1mA. Without even considering the large resistors and capacitors needed for the LDOs presently on SCµM, this design only takes up 10.3% of the device gate area those LDOs need. On top of this, the design script runs much faster than it takes to design an LDO by hand, with a total runtime of about 80 seconds.

If having the amplifier devices slightly below the threshold is not an issue for matching in the particular process all nine designs listed in Tables 2.4 through 2.9 are viable options with significantly lower amplifier current consumption, the highest being  $1.432\mu$ A with an amplifier channel length of 500nm and device channel length of 320nm. Across every single option, the only specs that are worse than the parameters in Table 2.3 are again the phase margin and PSRR bandwidth, but all options are stable and some even have a higher PSRR bandwidth. The only point of concern is the slightly lower phase margin of the design with an amplifier channel length of 500nm and a series device channel length of 300nm in combination with the unknown parasitic load capacitance on SC $\mu$ M, but if that value is discovered to be more than 100pF, the PSRR bandwidth is high enough that adding a very small capacitor at the amplifier output will likely resolve the issue of stability without bringing the bandwidth down too far compared to the LDOs on SC $\mu$ M.

Each transient simulation in Figures 2.6 through 2.8 has a load current that switches between 100µA and 1.1mA at 5MHz, which is an overestimate of how quickly the current will change between two extreme values. At this frequency and magnitude, the output voltage only changes by about 300mVpp for amplifier channel lengths on 500nm and 1µm, and 200mVpp for an amplifier channel length of 5µm. The digital and auxiliary LDOs on SCµM only have a voltage variation of about 100mVpp, which is due to the larger explicit capacitor at the load.

While this data is only for the auxiliary and digital LDOs, with the right set of parameters the design script can also generate a new schematic for each of the other LDOs on  $SC\mu M$ . There has been discussion of moving  $SC\mu M$  to a different technology process. Given reasonable specs, this script can generate the LDO designs for that project with ease, leaving only the verification simulations and layout to be done manually.

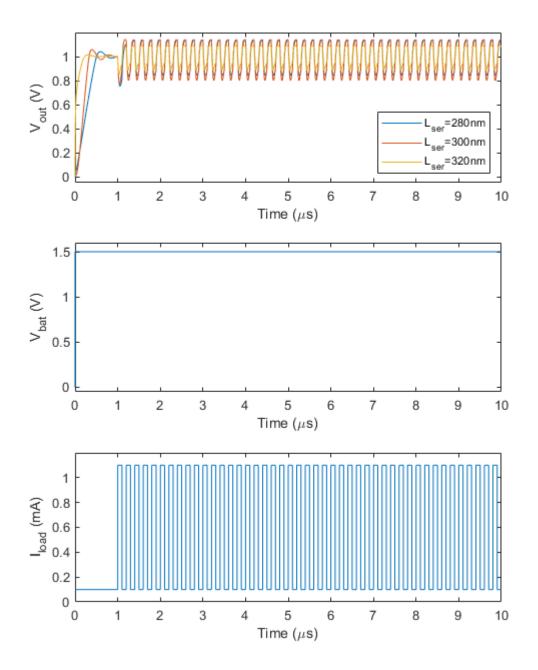

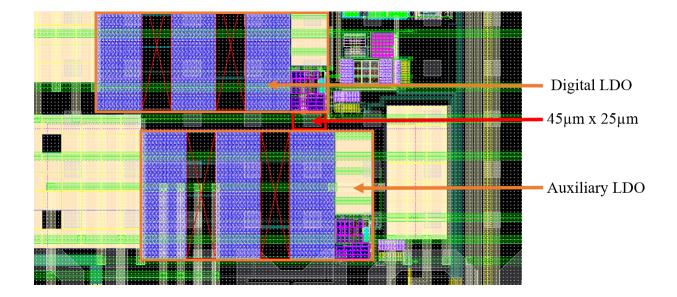

#### EE290C: 28nm SoC for IoT

For the Spring 2021 iteration of EE290C at UC Berkeley, the students collectively designed and taped out a system-on-a-chip (SoC) for internet-of-things (IoT) applications, with an on-chip CPU, radio, and Bluetooth Low Energy (BLE) and Advanced Encryption Standard (AES) compatibility. This chip design also includes two LDOs for the auxiliary and digital domains both of which use the same amplifier designs and device sizings. These LDOs were designed without the use of BAG. The simulated specs across temperature and process corners are shown in Table 2.10.

These LDOs were designed with 400nm channel length devices for the amplifier devices and a channel length of 150nm for the series device. Due to the nature of the course, these LDOs were designed at the same time as the rest of the chip, so almost no information about the load was known until about halfway through the design process. Even after the current draw from the analog and digital halves of the chip were estimated at 10mA or lower, the load capacitance was still unknown. Because of this, and a desire for a higher frequency power supply noise rejection bandwidth, the dominant pole was placed at the output of the LDO to keep the amplifier output pole and PSRR bandwidth higher and ensure the stability of the feedback loop. Although the phase margin for this design is very low, the simulated performance does not include the additional capacitance from the chip's power grid and circuit blocks attached to it. Because the LDO output is the dominant pole, that additional parasitic capacitance will only increase the phase margin. Through simulation, it also appears that the phase margin increases if the load does not draw the full 10mA allotted to each regulator.

With the same channel lengths for each device as the hand-designed LDO, the results of running the generator script with the parameters listed in Table 2.11 are shown in Table 2.12 (for a series device channel length of 150nm). For this set of inputs, the PSRR and phase margin improved significantly, with a slight decrease in required gate area. The static error has notably gotten worse, but the other parameters have stayed relatively similar. Each generated design of this LDO in Tables 2.11 through 2.14 has all devices in saturation, unlike the designs for SCµM in the 65nm process. Of the options, targeting low power and higher PSRR bandwidth, the 1µm amplifier channel length and 150nm series device channel length

<sup>&</sup>lt;sup>1</sup>Text in YAML file is the corner name instead of "nominal."

| Spec     | Value   |

|----------|---------|

| ser_type | р       |

| vdd      | 1.5     |

| vout     | 1       |

| iload    | 1e-3    |

| iref     | 500e-9  |

| iamp_max | 100e-6  |

| cload    | 100e-12 |

| cdecap   | 100e-12 |

| rsource  | 0       |

| Spec        | Value                |

|-------------|----------------------|

| err         | 1e-3                 |

| psrr        | 50                   |

| psrr_fbw    | 1e3                  |

| pm          | 60                   |

| loadreg     | 1e-3                 |

| load_pole   | False                |

| v_res       | 10e-3                |

| $sim_{env}$ | nominal <sup>1</sup> |

| Device   | Base Finger Width | Channel Type | Device Type |  |

|----------|-------------------|--------------|-------------|--|

| amp_in   | 500nm             | NMOS         | Input       |  |

| amp_load | 500nm             | PMOS         | Input       |  |

| amp_tail | 500nm             | NMOS         | Input       |  |

| amp_mir  | 500nm             | NMOS         | Input       |  |

| ser      | 500nm             | PMOS         | Input       |  |

Table 2.4: SCµM generated LDO input parameters for amplifier channel length of 500nm.

| $L_{ser}$       | 280nm           | 280nm               |                     | 300nm               |                     | 320nm               |                |

|-----------------|-----------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------|

| Data Source     | SCµM            | Script              | Sim.                | Script              | Sim.                | Script              | Sim.           |

| Static Error    | -2.756m         | 672.8µ              | 123.9µ              | 528.9µ              | $-225.5\mu$         | 462.4µ              | $-266.3\mu$    |

| Amp Current     | 4.763µA         | 465.3nA             | 297.8nA             | 878.9nA             | 727.4nA             | 1.462µA             | 1.432µA        |

| Phase Margin    | 85.62°          | 61.88°              | 69.07°              | 62.94°              | 60.53°              | 82.33°              | 80.06°         |

| PSRR            | 43.87dB         | $63.37 \mathrm{dB}$ | $60.77 \mathrm{dB}$ | $66.08 \mathrm{dB}$ | $68.31 \mathrm{dB}$ | $68.97 \mathrm{dB}$ | 71.48dB        |

| PSRR Bandwidth  | 461.9Hz         | 2.073kHz            | 3.040kHz            | 1.602kHz            | 2.116kHz            | 1.708kHz            | 717.1Hz        |

| Load Regulation | 96.50µ          | 170.4µ              | 132.8µ              | 162.9µ              | 10.95µ              | 10.50µ              | 11.87µ         |

| Amp Capacitor   | 3.60pF          | 0F                  | 0F                  | 0F                  | 0F                  | $625.7 \mathrm{fF}$ | 625.7fF        |

| Load Capacitor  | 452pF           | 0F                  | 0F                  | 0F                  | 0F                  | 0F                  | 0F             |

| Total Gate Area | $756.6 \mu m^2$ | $112.3 \mu m^2$     | $112.3 \mu m^2$     | $153.8 \mu m^2$     | $153.8 \mu m^2$     | $137.2 \mu m^2$     | $137.2\mu m^2$ |

Table 2.5: SCµM generated LDO performance for amplifier channel length of 500nm.

Figure 2.6: SCµM generated LDO transient for amplifier channel length of 500nm at 5MHz.

| Spec     | Value   |

|----------|---------|

| ser_type | р       |

| vdd      | 1.5     |

| vout     | 1       |

| iload    | 1e-3    |

| iref     | 500e-9  |

| iamp_max | 100e-6  |

| cload    | 100e-12 |

| cdecap   | 100e-12 |

| rsource  | 0       |

| Value                |

|----------------------|

| 1e-3                 |

| 50                   |

| 100                  |

| 60                   |

| 1e-3                 |

| False                |

| 10e-3                |

| nominal <sup>1</sup> |

|                      |

| Device   | Base Finger Width | Channel Type | Device Type |

|----------|-------------------|--------------|-------------|

| amp_in   | 500nm             | NMOS         | Input       |

| amp_load | 500nm             | PMOS         | Input       |

| amp_tail | 500nm             | NMOS         | Input       |

| amp_mir  | 500nm             | NMOS         | Input       |

| ser      | 500nm             | PMOS         | Input       |

Table 2.6: SCµM generated LDO input parameters for amplifier channel length of 1µm.

| $L_{ser}$       | 280nm           | 280                 | nm                  | 300nm               |                 | 320nm           |                |

|-----------------|-----------------|---------------------|---------------------|---------------------|-----------------|-----------------|----------------|

| Data Source     | SCµM            | Script              | Sim.                | Script              | Sim.            | Script          | Sim.           |

| Static Error    | -2.756m         | 513.2µ              | 116.8µ              | 294.8µ              | $-206.1\mu$     | 233.8µ          | $-274.5\mu$    |

| Amp Current     | 4.763µA         | 310.2nA             | 198.4nA             | 338.0nA             | 327.0nA         | 499.1nA         | 488.9nA        |

| Phase Margin    | 85.62°          | 70.80°              | 74.33°              | 77.64°              | 74.74°          | 79.56°          | 75.7°          |

| PSRR            | 43.87dB         | $62.27 \mathrm{dB}$ | $65.90 \mathrm{dB}$ | $66.86 \mathrm{dB}$ | 82.82dB         | 68.37dB         | 87.03dB        |

| PSRR Bandwidth  | 461.9Hz         | 1.252kHz            | 1.031kHz            | 529.2Hz             | 163.7Hz         | 404.1Hz         | 159.7Hz        |

| Load Regulation | 96.50µ          | 130.0µ              | 5.328µ              | 74.04µ              | 5.170µ          | 60.21µ          | 4.829µ         |

| Amp Capacitor   | 3.60pF          | 0F                  | 0F                  | 0F                  | 0F              | 0F              | 0F             |

| Load Capacitor  | 452pF           | 0F                  | 0F                  | 0F                  | 0F              | 0F              | 0F             |

| Total Gate Area | $756.6 \mu m^2$ | $122.9 \mu m^2$     | $122.9 \mu m^2$     | $157.1 \mu m^2$     | $157.1 \mu m^2$ | $233.0 \mu m^2$ | $233.0\mu m^2$ |

Table 2.7: SCµM generated LDO performance for amplifier channel length of 1µm.

Figure 2.7: SCµM generated LDO transient for amplifier channel length of 1µm at 5MHz.

| Spec     | Value   |

|----------|---------|

| ser_type | р       |

| vdd      | 1.5     |

| vout     | 1       |

| iload    | 1e-3    |

| iref     | 500e-9  |

| iamp_max | 100e-6  |

| cload    | 100e-12 |

| cdecap   | 100e-12 |

| rsource  | 0       |

| Spec        | Value                |

|-------------|----------------------|

| err         | 1e-3                 |

| psrr        | 70                   |

| psrr_fbw    | 100                  |

| pm          | 60                   |

| loadreg     | 1e-3                 |

| load_pole   | False                |

| v_res       | 10e-3                |

| $sim_{env}$ | nominal <sup>1</sup> |

| Device   | Base Finger Width | Channel Type | Device Type |

|----------|-------------------|--------------|-------------|

| amp_in   | 500nm             | NMOS         | Input       |

| amp_load | 500nm             | PMOS         | Input       |

| amp_tail | 500nm             | NMOS         | Input       |

| amp_mir  | 500nm             | NMOS         | Input       |

| ser      | 500nm             | PMOS         | Input       |

Table 2.8: SCµM generated LDO input parameters for amplifier channel length of 5µm.

| $L_{ser}$       | 280nm           | 280                 | nm                  | m 300nm         |                     | 320nm           |                |

|-----------------|-----------------|---------------------|---------------------|-----------------|---------------------|-----------------|----------------|

| Data Source     | SCµM            | Script              | Sim.                | Script          | Sim.                | Script          | Sim.           |

| Static Error    | -2.756m         | 126.7µ              | 38.46µ              | 121.3µ          | 11.21µ              | 110.6µ          | $-40.47\mu$    |

| Amp Current     | 4.763µA         | 314.1nA             | 248.1nA             | 638.1nA         | 495.8nA             | 990.4nA         | 991.1nA        |

| Phase Margin    | 85.62°          | 70.83°              | $71.38^{\circ}$     | 70.36°          | 70.35°              | 69.31°          | 66.81°         |

| PSRR            | 43.87dB         | $78.83 \mathrm{dB}$ | $75.08 \mathrm{dB}$ | 79.36dB         | $78.92 \mathrm{dB}$ | 81.42dB         | 93.80dB        |

| PSRR Bandwidth  | 461.9Hz         | 1.589kHz            | 244.6Hz             | 4.432kHz        | 199.2Hz             | 1.474kHz        | 52.13Hz        |

| Load Regulation | 96.50µ          | 47.49µ              | $2.325\mu$          | 44.67µ          | 2.117µ              | 44.67µ          | 2.242µ         |

| Amp Capacitor   | 3.60pF          | 168.9fF             | $168.9 \mathrm{fF}$ | 240.7fF         | 240.7fF             | 279.8fF         | 279.8fF        |

| Load Capacitor  | 452pF           | 0F                  | 0F                  | 0F              | 0F                  | 0F              | 0F             |

| Total Gate Area | $756.6 \mu m^2$ | $130.1 \mu m^2$     | $130.1 \mu m^2$     | $154.2 \mu m^2$ | $154.2 \mu m^2$     | $148.3 \mu m^2$ | $148.3\mu m^2$ |

Table 2.9: SCµM generated LDO performance for amplifier channel length of 5µm.

Figure 2.8: SCµM generated LDO transient for amplifier channel length of 5µm at 5MHz.

Figure 2.9: EE290C hand-designed LDO transient response at 5MHz.

|                 | Temperature (nominal <sup>1</sup> ) |                     | Corners $(27^{\circ}C)$ |                 | nominal <sup>1</sup> , $27^{\circ}C$ |                 |

|-----------------|-------------------------------------|---------------------|-------------------------|-----------------|--------------------------------------|-----------------|

| Parameter       | $0^{\circ}C$                        | $27^{\circ}C$       | $85^{\circ}C$           | Minimum         | Maximum                              | $R_{sup} = 10$  |

| Static Error    | 61.93µ                              | $-54.9\mu$          | -184.4µ                 | -1.076m         | 923.5µ                               | 260.8µ          |

| Amp Current     | 192.5µA                             | 196.4µA             | 203.8µA                 | 176.6µA         | 217.7µA                              | 192.1µA         |

| Phase Margin    | $49.57^{\circ}$                     | $50.54^{\circ}$     | 52.84°                  | 47.22°          | $55.95^{\circ}$                      | $50.35^{\circ}$ |

| PSRR            | 52.03dB                             | $52.47 \mathrm{dB}$ | 62.99dB                 | 50.17dB         | $59.25 \mathrm{dB}$                  | 49.89dB         |

| PSRR Bandwidth  | 733.8kHz                            | 663.0kHz            | 180.9kHz                | 316kHz          | 891.5kHz                             | 877.8kHz        |

| Load Regulation | 380.5µ                              | 408.1µ              | 471.5µ                  | 329.0µ          | 483.1µ                               | 488.6µ          |

| Amp Capacitor   | 0F                                  | 0F                  | 0F                      | 0F              | 0F                                   | 0F              |

| Load Capacitor  | 100nF                               | 100nF               | 100nF                   | 100nF           | 100nF                                | 100nF           |

| Total Gate Area | $208.7\mu m^2$                      | $208.7\mu m^2$      | $208.7\mu m^2$          | $208.7 \mu m^2$ | $208.7 \mu m^2$                      | $208.7 \mu m^2$ |

Table 2.10: EE290C LDO performance with 10mA load current.

design seems to be best. It has comparable power consumption, phase margin, and load regulation to the hand-designed LDO, with significant increases to both PSRR and PSRR bandwidth. The static error is a lot larger, but only amounts to about a 1mV offset from the nominal 900mV. The area is also slightly larger, but would still easily fit within the area bounds of the power block on the chip for EE290C. The transient responses of each generated LDO and the hand-designed LDO are shown in Figures 2.10 and 2.11. The chip for EE290C is designed to run at 100MHz, but the response at this frequency and the plot of the load current were too fast to show at the same scale as the startup transient due to the large output capacitor. The plots at 100MHz and 5MHz are virtually indistinguishable from each other, even between designs with different channel lengths. The main difference is the settling time of the startup transient due to the frequency of the secondary pole at the amplifier output. Although the difference in performance is not as dramatic as it is for the redesigned SCµM LDOs, the speed at which this script is able to generate this designs is still significantly faster than designing without it.

## 2.5 Approximations and Errors

The main sources of error in this script are likely from the device characterization and simplification of the model the LTICircuit functions use for calculation. The LTICircuit class assumes the canonical small signal model [4, Fig. 2.38]. Inaccuracies with this assumption produce the error seen in the design script outputs.

This script uses is the function estimate\_vth(db,is\_nch,lch,vgs,vbs) to approximate the threshold voltage for the output device, because this information is not included in the device characterization BAG uses due to the variation from linear or quadratic models in real devices. This estimation is very rough and usually inaccurate if the bias points the threshold is estimated at put the device out of saturation. To avoid this, the script estimates

| Spec     | Value  |

|----------|--------|

| ser_type | р      |

| vdd      | 1.5    |

| vout     | 0.9    |

| iload    | 10e-3  |

| iref     | 10e-6  |

| iamp_max | 500e-6 |

| cload    | 0      |

| cdecap   | 100e-9 |

| rsource  | 0      |

| Spec         | Value                        |

|--------------|------------------------------|

| err          | 0.01                         |

| psrr         | 40                           |

| psrr_fbw     | 500e3                        |

| pm           | 60                           |

| loadreg      | 10e-3                        |

| load_pole    | True                         |

| v_res        | 10e-3                        |

| $sim_{-}env$ | $\operatorname{nominal}^{1}$ |

| Device   | Base Finger Width | Channel Type | Device Type |

|----------|-------------------|--------------|-------------|

| amp_in   | 500nm             | NMOS         | Input       |

| amp_load | 500nm             | PMOS         | Input       |

| amp_tail | 270nm             | NMOS         | Input       |

| amp_mir  | 270nm             | NMOS         | Input       |

| ser      | 500nm             | PMOS         | Input       |

Table 2.11: EE290C generated LDO input parameters for amplifier channel length of 400nm.

| $L_{ser}$       | 150nm          | 150nm                  |                 | 180nm                |                 |

|-----------------|----------------|------------------------|-----------------|----------------------|-----------------|

| Data Source     | Original       | Script                 | Sim.            | Script               | Sim.            |

| Static Error    | $-54.9\mu$     | 2.523m                 | -1.848m         | 1.862m               | -2.123m         |

| Amp Current     | 196.4µA        | 251.0µA                | 258.3µA         | 393.2µA              | 405.4µA         |

| Phase Margin    | 50.54°         | 65.70°                 | $63.07^{\circ}$ | $64.48^{\circ}$      | $62.49^{\circ}$ |

| PSRR            | 52.47dB        | $59.56 \mathrm{dB}$    | 63.81dB         | $60.85 \mathrm{dB}$  | 84.72dB         |

| PSRR Bandwidth  | 663.0kHz       | 525.8kHz               | 436.7kHz        | $508.8 \mathrm{kHz}$ | 81.15kHz        |

| Load Regulation | 408.1µ         | 774.9µ                 | 432.5µ          | 694.1µ               | 400.3µ          |

| Amp Capacitor   | 0F             | 0F                     | 0F              | 0F                   | 0F              |

| Load Capacitor  | 100nF          | 100nF                  | 100nF           | 100nF                | 100nF           |

| Total Gate Area | $208.7\mu m^2$ | $185.4\mu\mathrm{m}^2$ | $185.4\mu m^2$  | $295.9 \mu m^2$      | $295.9\mu m^2$  |

Table 2.12: EE290C generated LDO performance for amplifier channel length of 400nm.

Figure 2.10: EE290C generated LDO transient for amplifier channel length of 400nm at 5MHz.

| Spec     | Value  |

|----------|--------|

| ser_type | р      |

| vdd      | 1.5    |

| vout     | 0.9    |

| iload    | 10e-3  |

| iref     | 10e-6  |

| iamp_max | 500e-6 |

| cload    | 0      |

| cdecap   | 100e-9 |

| rsource  | 0      |

| Spec         | Value       |  |

|--------------|-------------|--|

| err          | 0.01        |  |

| psrr         | 60          |  |

| psrr_fbw     | 1e6         |  |

| pm           | 60          |  |

| loadreg      | 10e-3       |  |

| load_pole    | True        |  |

| v_res        | 10e-3       |  |

| $sim_{-}env$ | $nominal^1$ |  |

| Device   | Base Finger Width | Channel Type | Device Type |  |

|----------|-------------------|--------------|-------------|--|

| amp_in   | 500nm             | NMOS         | Input       |  |

| amp_load | 500nm             | PMOS         | Input       |  |

| amp_tail | 270nm             | NMOS         | Input       |  |

| amp_mir  | 270nm             | NMOS         | Input       |  |

| ser      | ser 500nm PMOS    |              | Input       |  |

Table 2.13: EE290C generated LDO input parameters for amplifier channel length of 1µm.

| $L_{ser}$       | 150nm          | $150 \mathrm{nm}$      |                        | 180nm           |                   |

|-----------------|----------------|------------------------|------------------------|-----------------|-------------------|

| Data Source     | Original       | Script                 | Sim.                   | Script          | Sim.              |

| Static Error    | $-54.9\mu$     | 2.225m                 | 1.262m                 | 1.539m          | 489.0µ            |

| Amp Current     | 196.4µA        | 192.9µA                | 205.9µA                | 281.9µA         | 294.5 <i>u</i> µA |

| Phase Margin    | 50.54°         | $66.36^{\circ}$        | $54.90^{\circ}$        | $64.67^{\circ}$ | 54.24°            |

| PSRR            | 52.47dB        | $62.50\mathrm{dB}$     | 51.72dB                | 64.46dB         | 55.61dB           |

| PSRR Bandwidth  | 663.0kHz       | 1.039MHz               | $1.877 \mathrm{MHz}$   | 1.080MHz        | 1.434MHz          |

| Load Regulation | 408.1µ         | 963.9µ                 | 408.8µ                 | $958.4\mu$      | 393.6µ            |

| Amp Capacitor   | 0F             | $0\mathrm{F}$          | 0F                     | 0F              | 0F                |

| Load Capacitor  | 100nF          | 100nF                  | 100nF                  | 100nF           | 100nF             |

| Total Gate Area | $208.7\mu m^2$ | $235.0\mu\mathrm{m}^2$ | $235.0\mu\mathrm{m}^2$ | $302.7\mu m^2$  | $302.7\mu m^2$    |

Table 2.14: EE290C generated LDO performance for amplifier channel length of 1µm.

Figure 2.11: EE290C generated LDO transient for amplifier channel length of 1µm at 5MHz.

the threshold of the series device with its defined drain-source voltage (between the supply voltage and the output voltage) with the gate source voltage likely overestimated at half the supply voltage.

The static error is currently measured as the error caused by the non-infinite loop gain as shown in Equation 2.4. As mentioned briefly in Section 2.2, the static error calculated by this design script will likely be dominated by device offsets in the amplifier, which is not taken into account.

The PSRR is also approximated as the inverse of the gain from the power supply to the output rather than the gain from the input to the output divided by the power supply gain as described in Equation 2.5. The PSRR bandwidth would require the convolution of two lists of coefficients for both the numerator and denominator. For the purposes of this script, because the gain from the reference to the output is approximately 1 for a high loop gain, it was omitted from this calculation.

The YAML file that the specs of a completed generation are dumped into appears to have trouble with numbers such as the capacitances or device finger widths that are NumPy data types, but the data is stored properly even though the formatting is not as readable as a basic Python integer or float type is. The results are directly printed to that terminal, and if lost, can easily be generated again in very little time.

## Chapter 3 Conclusion

This report details the approach of a BAG design script to generate LDOs with real applications on chips like SC $\mu$ M. Although there are improvements to be made on this script, as it stands it is still an incredibly efficient and practical tool for LDO design. Using only the most basic LDO topology, design can be done quickly and is easily transferable between processes, allowing for fast estimates of performance and comparisons between designs, optimization goals, and technologies. With known specs for each LDO on SC $\mu$ M, it is possible to redesign lower power LDOs for each of the eight domains listed in Table 1.2 in under a day, potentially increasing their accuracy and noise reduction as well. The ability to design so many circuits in so little time is invaluable to so many projects, especially in an academic setting, allowing designers to focus more of their energy on the circuits powered by LDOs. With the necessity for power regulation on any chip, this script will undoubtedly see use in the future.

#### 3.1 Future Work

This design script does not check for the amplifier device thresholds, assuming that if the series device is in saturation the amplifier load will be as well, and then the V\* of the other amplifier devices will be set to match the load pair keeping them in saturation if they have similar V\* characteristics in the different regions of operation. If the channel length for the amplifier devices is significantly larger than the series device length, the amplifier load threshold will exceed the estimate for the series device and put all amplifier devices gate voltages subthreshold. If the script did include threshold estimates for the amplifier devices as well using the function estimate\_vth(db,is\_nch,lch,vgs,vbs), many of the tests run in Section 2.5 may not produce a solution due to the inaccuracy of the estimation function. A near-threshold biasing point improves the gain and power consumption of the amplifier significantly, and the overestimation of the threshold voltage may push devices too far from that point to meet more demanding specs. Each device that was operating subthreshold in Section 2.5 was within 100mV of the actual device threshold. Implementing a more accurate

threshold estimation or even extraction during characterization for BAG would significantly improve the performance of this design script and likely others as well.

Other features this script does not include but could be beneficial for any updated versions of this script are the frequency response of the load regulation, static error caused by device offsets, and the option of increasing the width of the amplifier devices for a pole at the amplifier output if the phase margin spec is met but the PSRR bandwidth spec is not. For the load regulation at higher frequencies, there may be peaking if the load capacitance is small, which depending on the operating frequency of the load circuits, could mean a significantly worse load regulation. This issue occurs most often if the dominant pole of the LDO is at the amplifier output. Adding estimates of the device offset contribution to static error will produce more accurate results in comparison to simulation, particularly at higher loops gains where Equation 2.4 is small. The modification to the amplifier device width for pole placement is only useful if the phase margin of a design is already higher than the spec without additional decap added, and if the PSRR spec is not met. Increasing the amplifier width increases the amplifier pole frequency, bringing the phase margin down and PSRR bandwidth up at the cost of power. It is possible that moving the pole to the output of the LDO will produce a design that meets both specs anyway and uses less power at the same time, but this may be a worthwhile modification if area for capacitors is limited and a higher PSRR bandwidth is necessary.

The final area in which this script could be expanded upon is automating layout. Approximating the area as the device gate area is easy to do by multiplying device widths and lengths. Some scripts do have the infrastructure to generate a layout from the produced design [5], which would be helpful in situations like with EE290C where the area allowed for the LDOs changed multiple times during the design process. Due to lack of setup in the processes used in this report and time, this script does not contain layout functionality, but adding it to this script will unquestionably speed up the design process further.

Appendix D describes additional issues with the power systems on SCµM that have not been resolved to date and possible routes to finding a solution.

### Bibliography

- Eric Chang et al. "BAG2: A process-portable framework for generator-based AMS circuit design". In: 2018 IEEE Custom Integrated Circuits Conference (CICC). 2018, pp. 1–8. DOI: 10.1109/CICC.2018.8357061.

- Filip Maksimovic. "Monolithic Wireless Transceiver Design". PhD thesis. EECS Department, University of California, Berkeley, May 2020, pp. 64-65. URL: http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-33.html.

- [3] Alex Moreno et al. "Single-Chip micro-Mote for Microrobotic Platforms". In: Government Microcircuit Applications & Critical Technology Conference. GOMACTech, 2020.

- Behzad Razavi. Design of Analog CMOS Integrated Circuits. first. McGraw-Hill, 2001, p. 36.

- [5] Nicholas Werblun. "Closing the Analog Design Loop with the Berkeley Analog Generator". MS. EECS Department, University of California, Berkeley, May 2019. URL: http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-23.html.

# Appendix A BAG Setup

#### Workspace Repository

To get the files needed to run BAG in the TSMC 65nm LP process, clone the repository at https://bwrcrepo.eecs.berkeley.edu/tsmc65/tsmc65lp/bag2\_tsmc65lp\_workspace by running in a terminal:

```

$ git clone git@bwrcrepo.eecs.berkeley.edu:tsmc65/tsmc65lp/

bag2_tsmc65lp_workspace

```

To get the files needed to run BAG in the TSMC 28nm process, clone the repository at https://bwrcrepo.eecs.berkeley.edu/tstech28/bag2\_tsmc28\_workspace by running in a terminal:

\$ git clone git@bwrcrepo.eecs.berkeley.edu:tstech28/ bag2\_tsmc28\_workspace \$ git checkout ee194\_290c

Switching to the ee194\_290c branch is necessary for TSMC 28nm to avoid an error with submodule paths missing in setup. After cloning the repository, add submodules in the BAG workspace directory with the following commands:

```

$ git submodule add https://github.com/PisterLab/span_ion

span_ion_proj

$ git submodule add https://github.com/PisterLab/bag2_analog

$ git submodule add https://github.com/PisterLab/bag2_digital