## Co-design of Algorithms, Hardware, and Scheduling for Deep Learning Applications

Qijing Huang

### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-202 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-202.html

August 16, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Co-design of Algorithms, Hardware, and Scheduling for Deep Learning Applications

by

Qijing Huang

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor John Wawrzynek, Chair Professor Yakun Sophia Shao Professor Joseph E. Gonzalez Doctor Aravind Kalaiah

Summer 2021

Co-design of Algorithms, Hardware, and Scheduling for Deep Learning Applications

Copyright 2021 by Qijing Huang

#### Abstract

Co-design of Algorithms, Hardware, and Scheduling for Deep Learning Applications

by

Qijing Huang

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor John Wawrzynek, Chair

For decades, ever-increasing computing power has been a driving force behind many technology revolutions, including the recent advances in artificial intelligence. However, due to the slowing of integrated circuit process scaling, for system architects to continue to satisfy the ever-growing compute appetite of today's applications, they must now resort to employing heterogeneous systems with specialized accelerators.

Building these accelerator systems, though, is extremely expensive and time-consuming. First, the development cycle for hardware is notoriously long, making it difficult to keep up with the rapid progress in algorithms. Meanwhile, existing compilers are incapable of navigating the intractable mapping space exposed by the novel accelerator architectures. Lastly, algorithms are often designed without hardware efficiency as a key metric, and therefore, pose extra challenges in designing efficient hardware.

This thesis tackles the significant challenges in jointly designing and optimizing algorithms, scheduling, and hardware designs for acceleration. We aim to advance the state-of-theart through a three-pronged approach: the development of methodologies and tools that automatically generate accelerator systems from high-level abstractions, shortening the hardware development cycle; the adaptation of machine learning and other optimization techniques to improve accelerator design and compilation flows; and the co-design of algorithms and accelerators to exploit more optimization opportunities.

The target application domain of this thesis is deep learning which has achieved unprecedented success in a wide range of tasks such as computer vision, neural language processing, etc. As intelligent devices prevail, deep learning is foreseeably becoming a major computation demand in our everyday life. Therefore, by performing end-to-end system optimization with hardware acceleration, the dissertation aims to unleash the ubiquitous adoption of cutting-edge deep learning algorithms to transform various aspects of life.

To my parents Shaobin and Lianhua, who taught me about love and faith. To my friends, who taught me that giving is receiving.

# Contents

| Co       | Contents i |        |                                                  |      |

|----------|------------|--------|--------------------------------------------------|------|

| Li       | st of      | Figure | es                                               | vii  |

| Li       | st of      | Tables | 3                                                | xi   |

| 1        | Intr       | oducti | on                                               | 1    |

|          | 1.1        | Challe | nges and Opportunities                           | . 2  |

|          | 1.2        | Thesis | Contributions                                    |      |

|          |            | 1.2.1  | Hardware and Software Co-Design                  | . 3  |

|          |            | 1.2.2  | Algorithm and Hardware Co-Design                 |      |

|          |            | 1.2.3  | Scheduling and Hardware Co-Design                |      |

|          |            | 1.2.4  | Machine Learning for Hardware                    | . 5  |

| <b>2</b> | Har        | dware  | and Software Co-Design                           | 6    |

|          | 2.1        | Accele | rator Design Methodology                         |      |

|          | 2.2        | Backgr | round and Motivation                             | . 7  |

|          |            | 2.2.1  | Related Work                                     | . 8  |

|          | 2.3        |        | fuge Overview                                    |      |

|          | 2.4        | Centri | fuge Design Flow                                 | . 9  |

|          |            | 2.4.1  | Generating a Base SoC with Rocket Chip           | . 10 |

|          |            | 2.4.2  | Integrating Accelerators into the SoC            | . 11 |

|          |            |        | 2.4.2.1 RoCC Accelerators                        |      |

|          |            |        | 2.4.2.2 TileLink-attached accelerators           |      |

|          |            |        | 2.4.2.3 Network-attached accelerators            |      |

|          |            | 2.4.3  | Generating Accelerators with Vivado HLS          |      |

|          |            | 2.4.4  | Generating the software stack for a complete SoC | . 13 |

|          |            |        | 2.4.4.1 Running Bare-metal                       |      |

|          |            |        | 2.4.4.2 Running on Linux                         |      |

|          | 2.5        | Centri | fuge Case Studies                                |      |

|          |            | 2.5.1  | Smart-House Hub                                  |      |

|          |            |        | 2.5.1.1 Evaluating the Baseline Application      | . 16 |

|   |     | 2.5.1.2Generating Accelerators172.5.1.3Evaluating Accelerators17                                                                   |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 2.5.1.3 Evaluating Accelerators                                                                                                    |

|   |     | 2.5.1.4 Continue Hardware and Software Development                                                                                 |

|   |     | 2.5.2 Distributed Matrix Multiplication Accelerator                                                                                |

|   |     | 2.5.3.1 Design for New Algorithms                                                                                                  |

|   |     | 2.5.3.2 Distributed Accelerators                                                                                                   |

|   |     | 2.5.3.2         Distributed Accelerators         2.2           2.5.4         Graph Accelerator         22                          |

|   | 2.6 | Parallel Abstraction for HLS   25                                                                                                  |

|   | 2.0 | 2.6.1       Communicating Sequential Processes       25                                                                            |

|   |     | 2.6.1       Communicating Sequential Processes       2.5         2.6.2       Go-to-Verilog HLS       25                            |

|   |     | 2.6.2       Go-to-vernog HLS       2.5         2.6.3       Discussion       2.7                                                    |

|   | 2.7 | Z.0.5         Discussion         Z7           Conclusion         27         27                                                     |

|   | 2.1 | Conclusion                                                                                                                         |

| 3 | Alg | orithm and Hardware Co-Design 28                                                                                                   |

|   | 3.1 | Co-design for Image Classification                                                                                                 |

|   | 3.2 | Synetgy Background and Motivation                                                                                                  |

|   |     | 3.2.1 Efficient CNN Models                                                                                                         |

|   |     | 3.2.2 CNN Quantization                                                                                                             |

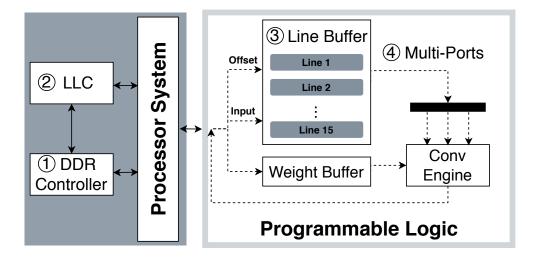

|   |     | 3.2.3 Hardware Designs                                                                                                             |

|   | 3.3 | Synetgy CNN Design                                                                                                                 |

|   |     | 3.3.1 ShuffleNetV2 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                      |

|   |     | 3.3.2 DiracDeltaNet $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 34$                                     |

|   |     | 3.3.3 CNN Quantization                                                                                                             |

|   | 3.4 | Synetgy Hardware Design 40                                                                                                         |

|   |     | 3.4.1 The accelerator architecture                                                                                                 |

|   |     | 3.4.1.1 Dataflow Architecture                                                                                                      |

|   |     | $3.4.1.2  \text{Convolution Unit}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                |

|   |     | $3.4.1.3  \text{Conversion Unit}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                 |

|   |     | $3.4.1.4  \text{Pooling Unit}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    |

|   |     | $3.4.1.5  \text{Shift Unit}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                      |

|   |     | 3.4.1.6 Shuffle Unit                                                                                                               |

|   |     | 3.4.1.7 Fully Connected Unit                                                                                                       |

|   |     | 3.4.2 Software                                                                                                                     |

|   | 3.5 | Synetgy Experimental Results                                                                                                       |

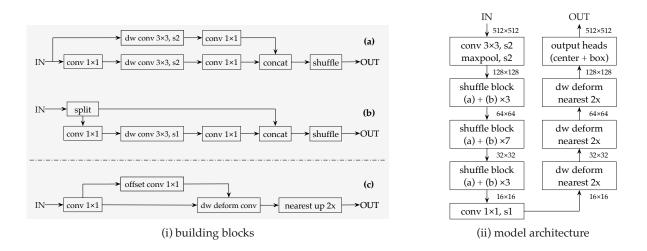

|   | 3.6 | Co-design for Object Detection                                                                                                     |

|   | 3.7 | CoDeNet Background and Motivation                                                                                                  |

|   |     | 3.7.1 Object Detection                                                                                                             |

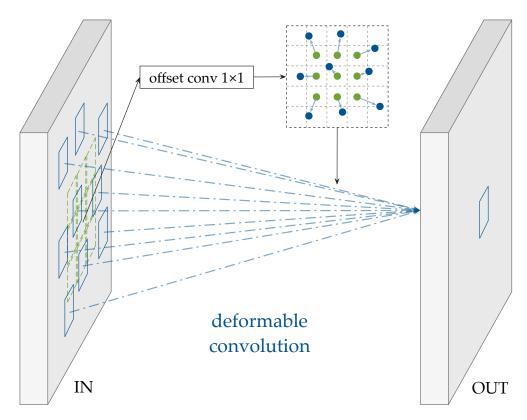

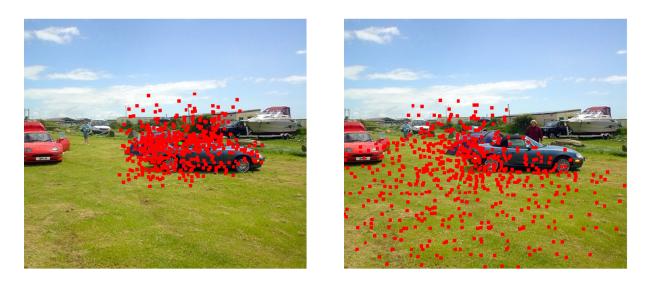

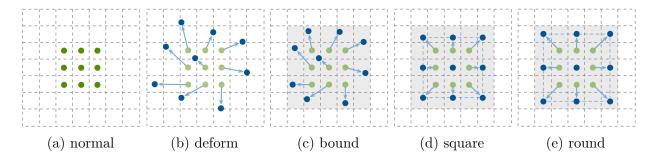

|   |     | 3.7.2 Deformable Convolution                                                                                                       |

|   |     | 3.7.3 Algorithm-hardware Co-design for Object Detection                                                                            |

|   |     | $3.7.4$ Quantization $\ldots \ldots 53$ |

|   | 3.8 | CoDeNet Deformable Operation Co-design                                                                                             |

|   |      | $3.8.1 \\ 3.8.2$ | Algorithm Modifications5Hardware Optimizations5                                   | 4  |

|---|------|------------------|-----------------------------------------------------------------------------------|----|

|   | 3.9  |                  | 1                                                                                 | 8  |

|   | 0.0  | 3.9.1            | CoDeNet Neural Network Design                                                     |    |

|   |      | 3.9.2            | 8                                                                                 | 51 |

|   | 3 10 |                  |                                                                                   | 4  |

|   |      |                  | $1 \sin 1 \cdot $ |    |

|   | 0.11 | Control          |                                                                                   | Ű  |

| 4 |      |                  | g and Hardware Co-design 6                                                        |    |

|   | 4.1  |                  | vare-Aware Scheduling                                                             |    |

|   | 4.2  | 0                |                                                                                   | 0  |

|   |      | 4.2.1            | 01                                                                                | 0  |

|   |      | 4.2.2            |                                                                                   | '1 |

|   |      |                  | 4.2.2.1 Brute-force Approaches                                                    | '1 |

|   |      |                  | 4.2.2.2 Feedback-based Approaches                                                 | '1 |

|   |      |                  | 4.2.2.3 Constrained-optimization Approaches                                       | 2  |

|   | 4.3  | The C            | oSA Framework                                                                     | 4  |

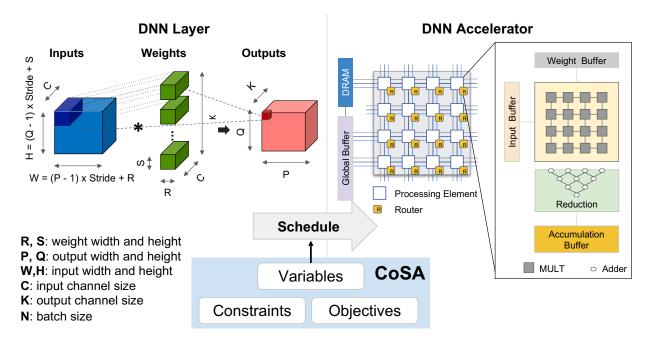

|   |      | 4.3.1            | CoSA Overview                                                                     | 4  |

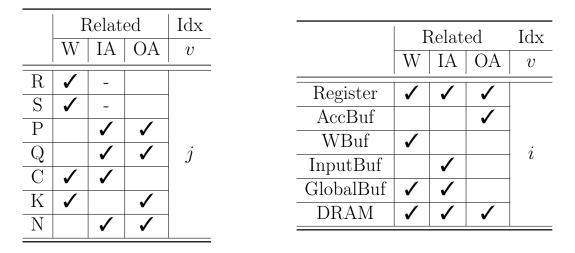

|   |      |                  | 4.3.1.1 Target Workload                                                           | 5  |

|   |      |                  | 4.3.1.2 Target Architecture                                                       | 5  |

|   |      |                  | 4.3.1.3 Target Scheduling Decisions                                               | 6  |

|   |      | 4.3.2            |                                                                                   | 7  |

|   |      |                  |                                                                                   | 7  |

|   |      |                  | -                                                                                 | 9  |

|   |      | 4.3.3            |                                                                                   | 0  |

|   |      |                  | 4.3.3.1 Buffer Capacity Constraint                                                | 0  |

|   |      |                  | 4.3.3.2 Spatial Resource Constraint                                               |    |

|   |      | 4.3.4            | 1                                                                                 | 31 |

|   |      |                  | 5                                                                                 | 31 |

|   |      |                  | 3                                                                                 | 31 |

|   |      |                  | 4.3.4.3 Traffic-Driven Objective                                                  |    |

|   |      |                  |                                                                                   | 4  |

|   |      | 4.3.5            | •                                                                                 | 4  |

|   | 4.4  |                  | bology                                                                            |    |

|   | 1.1  | 4.4.1            |                                                                                   | 5  |

|   |      | 4.4.2            | Baseline Schedulers                                                               |    |

|   |      | 4.4.3            | Experiment Setup                                                                  |    |

|   | 4.5  |                  | 1 1                                                                               | 7  |

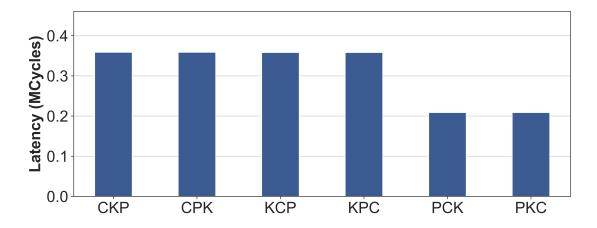

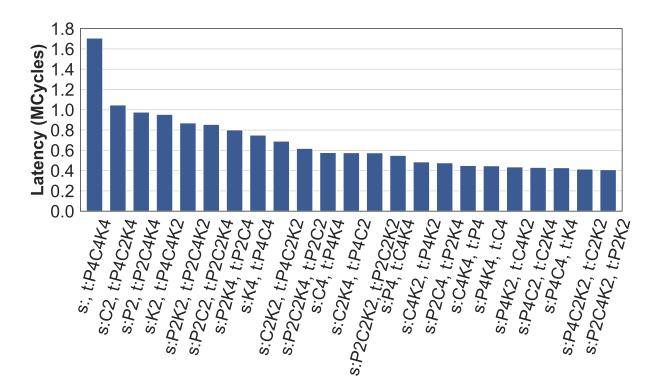

|   | 4.0  | 4.5.1            |                                                                                   | 7  |

|   |      | 4.5.1<br>4.5.2   |                                                                                   | 7  |

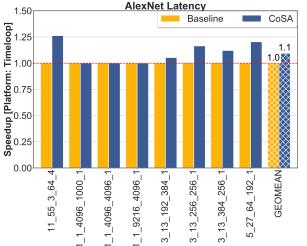

|   |      | 4.9.2            | 4.5.2.1 Performance                                                               |    |

|   |      |                  |                                                                                   |    |

|   |      |                  | 4.5.2.2 Energy                                                                    | 9  |

iv

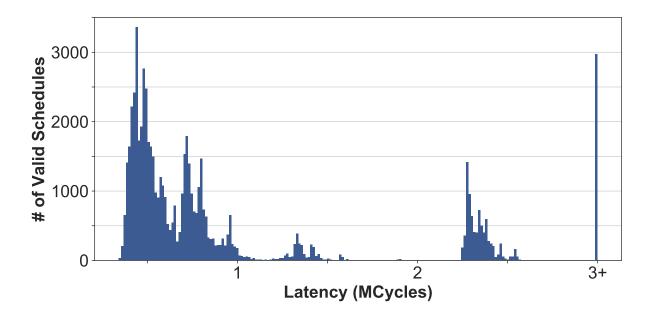

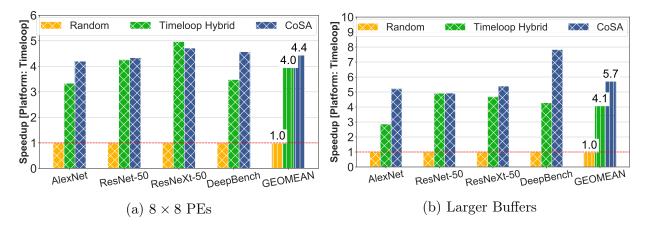

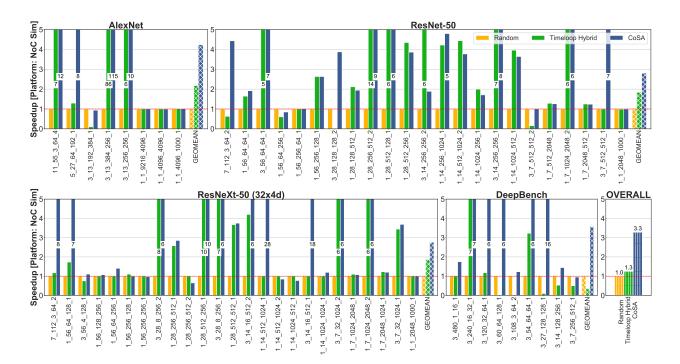

| 4.5.2.4Different HW Architectures894.5.3Evaluation on NoC Simulator914.5.4Evaluation on NoC Simulator924.6Scheduling-Informed Hardware Design934.7On-chip Memory Partitioning with CoSA934.7.0.1Formulation934.7.0.2Evaluation on On-chip Memory Partitioning945Machine Learning for Hardware Design965.1Machine Learning for Phase Ordering965.2Background and Motivation995.2.1Compiler Phase-ordering995.2.2Reinforcement Learning Algorithms1005.2.3Evolutionary Algorithms1015.3AutoPhase Framework for Automatic Phase Ordering1025.3.1HLS Compiler1035.3.3IR Feature Extractor1035.3.4Random Program Generator1045.4.1Importance of Program Features1045.4.2Importance of Program Features1085.5.3Normalization1085.5.4Applied Passes per Action1095.6.1Performance1095.6.2Generalization1115.7Conclusions1146Discussion and Future Work1156.1Performance1156.1Cordesign of algorithm, software, and hardware1156.1.2Automatic Design and Verification Methodology1166.1.3Machine Learning and Optimization for Hardware117 <th></th> <th></th> <th>4.5.2.3 Objective Breakdown</th> <th></th>                                                                                                                                                            |          |      | 4.5.2.3 Objective Breakdown                                                                                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

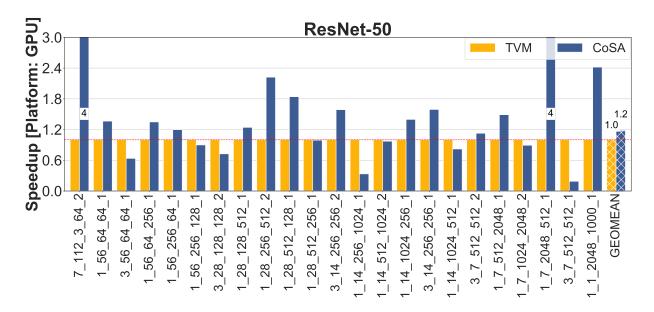

| 4.5.4       Evaluation on GPU       92         4.6       Scheduling-Informed Hardware Design       93         4.7       On-chip Memory Partitioning with CoSA       93         4.7.0.1       Formulation       93         4.7.0.2       Evaluation on On-chip Memory Partitioning       94         5       Machine Learning for Hardware Design       96         5.1       Machine Learning for Phase Ordering       96         5.2       Background and Motivation       99         5.2.2       Reinforcement Learning Algorithms       100         5.2.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Proviously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multipl                                                |          |      |                                                                                                                                                             |  |

| 4.6       Scheduling-Informed Hardware Design       93         4.7       On-chip Memory Partitioning with CoSA       93         4.7.0.1       Formulation       93         4.7.0.2       Evaluation on On-chip Memory Partitioning       94         4.8       Conclusion       94         5       Machine Learning for Hardware Design       96         5.1       Machine Learning for Phase Ordering       96         5.2       Background and Motivation       99         5.2.1       Compiler Phase-ordering       96         5.2       Reinforcement Learning Algorithms       100         5.2.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       106         5.4.2       Importance of Program Features       106         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition <t< td=""><td></td><td></td><td></td><td></td></t<>          |          |      |                                                                                                                                                             |  |

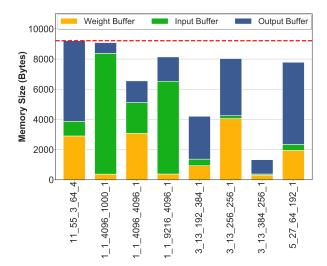

| 4.7On-chip Memory Partitioning with CoSA934.7.0.1Formulation934.7.0.2Evaluation on On-chip Memory Partitioning944.8Conclusion945Machine Learning for Hardware Design965.1Machine Learning for Phase Ordering965.2Background and Motivation995.2.1Compiler Phase-ordering995.2.2Reinforcement Learning Algorithms1005.2.3Evolutionary Algorithms1015.3AutoPhase Framework for Automatic Phase Ordering1025.3.1HLS Compiler1035.3.3IR Feature Extractor1035.3.4Random Program Generator1045.3.5Overall Flow of AutoPhase1045.4.1Importance of Pregram Features1065.4.2Importance of Pregram Features1065.4.3Inportance of Pregram Features1065.4.4Importance of Previously Applied Passes1085.5.5Problem Formulation1085.5.1The RL Environment Definition1095.6.2Generalization Techniques1095.6.3Normalization Techniques1095.6.4performance1095.6.5Generalization1115.7Conclusions1146Discussion1156.1.1Co-design of algorithm, software, and hardware1156.1.2Automatic Design and Verification Methodology1166.1.3<                                                                                                                                                                                                                                             |          | 1.0  |                                                                                                                                                             |  |

| 4.7.0.1Formulation934.7.0.2Evaluation on On-chip Memory Partitioning944.8Conclusion945Machine Learning for Hardware Design965.1Machine Learning for Phase Ordering965.2Background and Motivation995.2.1Compiler Phase-ordering995.2.2Reinforcement Learning Algorithms1005.2.3Evolutionary Algorithms1015.3AutoPhase Framework for Automatic Phase Ordering1025.3.1HLS Compiler1035.3.2Clock-cycle Profiler1035.3.3IR Feature Extractor1035.3.4Random Program Generator1045.4.5Overall Flow of AutoPhase1045.4.1Importance of Program Features1045.4.2Importance of Previously Applied Passes1085.5.1The RL Environment Definition1085.5.2Applying Multiple Passes per Action1095.6.1Performance1095.6.2Generalization1115.7Conclusions1146Discussion and Future Work1156.1.1Co-design of algorithm, software, and hardware1156.1.2Automatic Design and Verification Methodology1166.1.3Machine Learning and Optimization for Hardware1176.2.1Cor-Design for Broader Applications118                                                                                                                                                                                                                                                                             |          |      |                                                                                                                                                             |  |

| 4.7.0.2Evaluation on On-chip Memory Partitioning944.8Conclusion945Machine Learning for Hardware Design965.1Machine Learning for Phase Ordering965.2Background and Motivation995.2.1Compiler Phase-ordering995.2.2Reinforcement Learning Algorithms1005.2.3Evolutionary Algorithms1015.3AutoPhase Framework for Automatic Phase Ordering1025.3.1HLS Compiler1025.3.2Clock-cycle Profiler1035.3.3IR Feature Extractor1035.3.4Random Program Generator1045.4.2Importance of Program Features1045.4.3Importance of Previously Applied Passes1085.5Problem Formulation1085.5.1The RL Environment Definition1085.5.2Applying Multiple Passes per Action1095.6.1Performance1095.6.2Generalization1115.7Conclusions1146Discussion and Future Work1156.1.1Co-design of algorithm, software, and hardware1156.1.2Automatic Design and Verification Methodology1166.1.3Machine Learning and Optimization for Hardware1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                          |          | 4.7  |                                                                                                                                                             |  |

| 4.8       Conclusion       94         5       Machine Learning for Hardware Design       96         5.1       Machine Learning for Phase Ordering       96         5.2       Background and Motivation       99         5.2.1       Compiler Phase-ordering       99         5.2.2       Reinforcement Learning Algorithms       100         5.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.1       HLS Compiler       103         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Pregram Features       106         5.4.2       Importance of Pregram Features       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7                                                                                          |          |      |                                                                                                                                                             |  |

| 5       Machine Learning for Hardware Design       96         5.1       Machine Learning for Phase Ordering       96         5.2       Background and Motivation       99         5.2.1       Compiler Phase-ordering       99         5.2.2       Reinforcement Learning Algorithms       100         5.3       Evolutionary Algorithms       101         5.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.1       HLS Compiler       103         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Importance of Program Features       104         5.4.1       Importance of Previously Applied Passes       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6.3       Normalization Techniques       109         5.6.4       Performance       109         5.6.5       Performance       109         5.6.1 <td></td> <td>1.0</td> <td></td> <td></td>                                           |          | 1.0  |                                                                                                                                                             |  |

| 5.1       Machine Learning for Phase Ordering       96         5.2       Background and Motivation       99         5.2.1       Compiler Phase-ordering       99         5.2.2       Reinforcement Learning Algorithms       100         5.2.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.1       HLS Compiler       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4.2       Importance of Program Features       104         5.4.1       Importance of Program Features       104         5.4.2       Importance of Previously Applied Passes       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6.1       Performance       109         5.6.2       Generalization Techniques       109         5.6.3       Normalization Techniques       109         5.6.4       Performance       109         5.                                                                                  |          | 4.8  | Conclusion                                                                                                                                                  |  |

| 5.2       Background and Motivation       99         5.2.1       Compiler Phase-ordering       99         5.2.2       Reinforcement Learning Algorithms       100         5.2.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.1       HLS Compiler       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115 <td< td=""><td><b>5</b></td><td></td><td></td><td></td></td<>                            | <b>5</b> |      |                                                                                                                                                             |  |

| 5.2.1       Compiler Phase-ordering       99         5.2.2       Reinforcement Learning Algorithms       100         5.2.3       Evolutionary Algorithms       101         5.3       Evolutionary Algorithms       101         5.3       Evolutionary Algorithms       102         5.3.1       HLS Compiler       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Program Features       104         5.4       Importance of Program Features       106         5.4.1       Importance of Previously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work                                                                                           |          |      |                                                                                                                                                             |  |

| 5.2.2Reinforcement Learning Algorithms1005.2.3Evolutionary Algorithms1015.3AutoPhase Framework for Automatic Phase Ordering1025.3.1HLS Compiler1025.3.2Clock-cycle Profiler1035.3.3IR Feature Extractor1035.3.4Random Program Generator1045.3.5Overall Flow of AutoPhase1045.4Correlation of Passes and Program Features1045.4.1Importance of Program Features1065.4.2Importance of Program Features1085.5Problem Formulation1085.5.1The RL Environment Definition1085.5.2Applying Multiple Passes per Action1095.6.1Performance1095.6.2Generalization1115.7Conclusions1146Discussion and Future Work1156.1.1Co-design of algorithm, software, and hardware1156.1.2Automatic Design and Verification Methodology1166.1.3Machine Learning and Optimization for Hardware1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 5.2  |                                                                                                                                                             |  |

| 5.2.3       Evolutionary Algorithms       101         5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.1       HLS Compiler       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5.4       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1       Discussion (algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology </td <td></td> <td></td> <td>I O</td> <td></td> |          |      | I O                                                                                                                                                         |  |

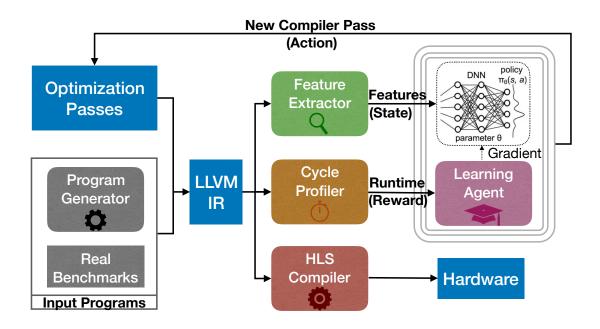

| 5.3       AutoPhase Framework for Automatic Phase Ordering       102         5.3.1       HLS Compiler       103         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       104         5.4.2       Importance of Previously Applied Passes       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization Techniques       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.                                                                                  |          |      |                                                                                                                                                             |  |

| 5.3.1       HLS Compiler       102         5.3.2       Clock-cycle Profiler       103         5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117     <                                                             |          |      |                                                                                                                                                             |  |

| 5.3.2Clock-cycle Profiler103 $5.3.3$ IR Feature Extractor103 $5.3.4$ Random Program Generator104 $5.3.5$ Overall Flow of AutoPhase104 $5.4$ Correlation of Passes and Program Features104 $5.4$ Correlation of Passes and Program Features104 $5.4.1$ Importance of Program Features106 $5.4.2$ Importance of Previously Applied Passes108 $5.5$ Problem Formulation108 $5.5.1$ The RL Environment Definition108 $5.5.2$ Applying Multiple Passes per Action109 $5.5.3$ Normalization Techniques109 $5.6.1$ Performance109 $5.6.2$ Generalization111 $5.7$ Conclusions111 $6$ Discussion and Future Work115 $6.1.1$ Co-design of algorithm, software, and hardware115 $6.1.2$ Automatic Design and Verification Methodology116 $6.1.3$ Machine Learning and Optimization for Hardware117 $6.2.1$ Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 5.3  |                                                                                                                                                             |  |

| 5.3.3       IR Feature Extractor       103         5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization Techniques       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       111         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116                                                                            |          |      | -                                                                                                                                                           |  |

| 5.3.4       Random Program Generator       104         5.3.5       Overall Flow of AutoPhase       104         5.4       Correlation of Passes and Program Features       104         5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6.1       Performance       109         5.6.2       Generalization       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications                                                               |          |      | ·                                                                                                                                                           |  |

| 5.3.5Overall Flow of AutoPhase1045.4Correlation of Passes and Program Features1045.4.1Importance of Program Features1065.4.2Importance of Previously Applied Passes1085.5Problem Formulation1085.5.1The RL Environment Definition1085.5.2Applying Multiple Passes per Action1095.5.3Normalization Techniques1095.6.1Performance1095.6.2Generalization1095.6.3Sense enclose1115.7Conclusions1115.7Conclusions1156.1.1Discussion and Future Work1156.1.2Automatic Design and Verification Methodology1166.1.3Machine Learning and Optimization for Hardware1176.2Future Work1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |      |                                                                                                                                                             |  |

| 5.4       Correlation of Passes and Program Features       104         5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6.4       Evaluation       109         5.6.5       Generalization       109         5.6.6       Evaluation       109         5.6.2       Generalization       109         5.6.2       Generalization       111         5.7       Conclusions       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                           |          |      | 0                                                                                                                                                           |  |

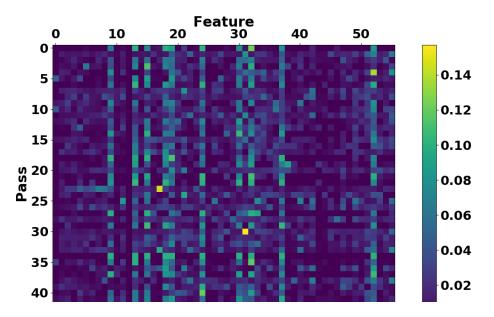

| 5.4.1       Importance of Program Features       106         5.4.2       Importance of Previously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       109         5.6.2       Generalization       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                              |          |      |                                                                                                                                                             |  |

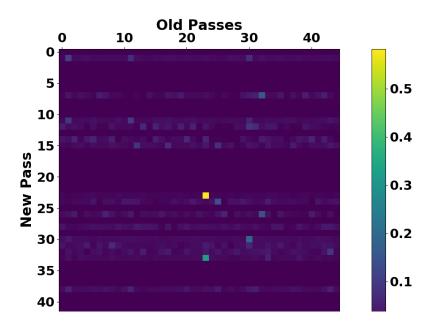

| 5.4.2       Importance of Previously Applied Passes       108         5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       109         5.6.2       Generalization       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                           |          | 5.4  | Correlation of Passes and Program Features                                                                                                                  |  |

| 5.5       Problem Formulation       108         5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       109         5.6.2       Generalization       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                          |          |      |                                                                                                                                                             |  |

| 5.5.1       The RL Environment Definition       108         5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       109         5.7       Conclusions       111         5.7       Conclusions       111         5.7       Conclusions       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                   |          |      | 5.4.2 Importance of Previously Applied Passes                                                                                                               |  |

| 5.5.2       Applying Multiple Passes per Action       109         5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       109         5.7       Conclusions       111         5.7       Conclusions       111         5.7       Conclusions       111         5.7       Conclusions       111         5.7       Conclusions       115         6.1       Discussion and Future Work       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                                     |          | 5.5  | Problem Formulation                                                                                                                                         |  |

| 5.5.3       Normalization Techniques       109         5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       101         5.7       Conclusions       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |      | 5.5.1 The RL Environment Definition                                                                                                                         |  |

| 5.6       Evaluation       109         5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       111         6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2       Future Work       117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |      | 5.5.2 Applying Multiple Passes per Action                                                                                                                   |  |

| 5.6.1       Performance       109         5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |      | 5.5.3 Normalization Techniques                                                                                                                              |  |

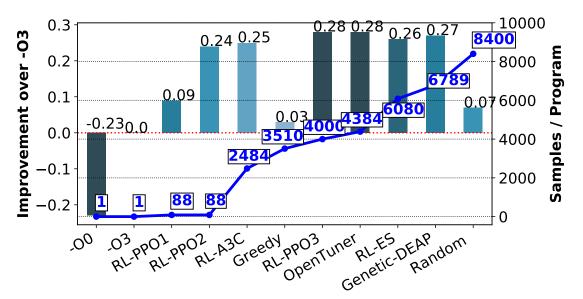

| 5.6.2       Generalization       111         5.7       Conclusions       114         6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 5.6  | Evaluation                                                                                                                                                  |  |

| 5.7       Conclusions       114         6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |      | 5.6.1 Performance                                                                                                                                           |  |

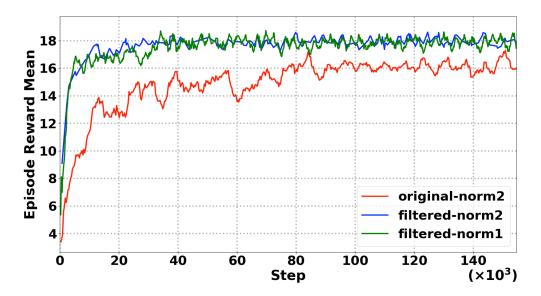

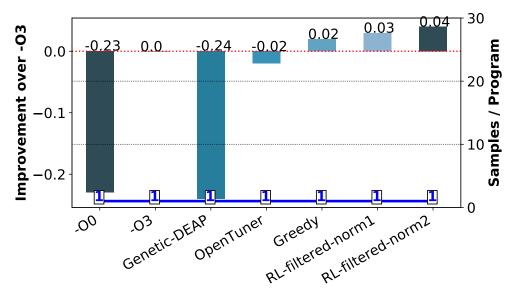

| 6       Discussion and Future Work       115         6.1       Discussion       115         6.1.1       Co-design of algorithm, software, and hardware       115         6.1.2       Automatic Design and Verification Methodology       116         6.1.3       Machine Learning and Optimization for Hardware       117         6.2       Future Work       117         6.2.1       Co-Design for Broader Applications       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |      | 5.6.2 Generalization $\ldots \ldots \ldots$ |  |

| <ul> <li>6.1 Discussion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 5.7  | Conclusions                                                                                                                                                 |  |

| <ul> <li>6.1.1 Co-design of algorithm, software, and hardware</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6        | Disc | cussion and Future Work 115                                                                                                                                 |  |

| 6.1.2Automatic Design and Verification Methodology1166.1.3Machine Learning and Optimization for Hardware1176.2Future Work1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 6.1  | Discussion                                                                                                                                                  |  |

| 6.1.3Machine Learning and Optimization for Hardware1176.2Future Work1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |      | 6.1.1 Co-design of algorithm, software, and hardware                                                                                                        |  |

| 6.2Future Work1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |      | 6.1.2 Automatic Design and Verification Methodology                                                                                                         |  |

| 6.2Future Work1176.2.1Co-Design for Broader Applications118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |      | 6.1.3 Machine Learning and Optimization for Hardware                                                                                                        |  |

| 6.2.1 Co-Design for Broader Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 6.2  | ÷ -                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |      | 6.2.1 Co-Design for Broader Applications                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |      |                                                                                                                                                             |  |

| 6.2.3 Machine Learning and Optimization for Systems |     |

|-----------------------------------------------------|-----|

| Bibliography                                        | 120 |

# List of Figures

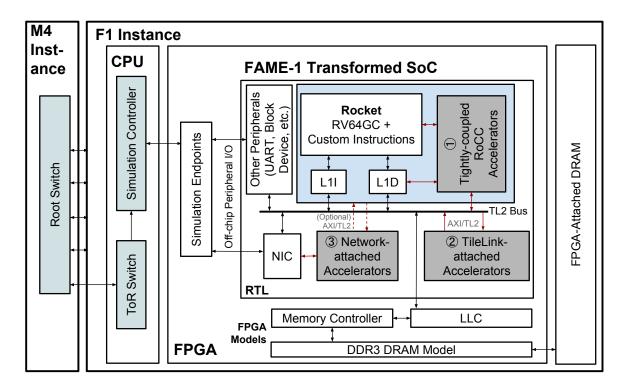

| 2.1        | Block Diagram of FireSim Simulating Centrifuge-generated SoC with Accelerators                        | 10         |

|------------|-------------------------------------------------------------------------------------------------------|------------|

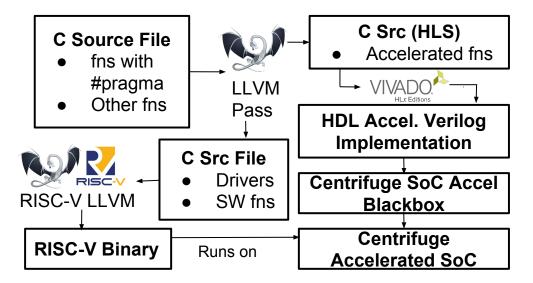

| 2.2        | Centrifuge HLS Flow, C to Acclerator RTL + Software Driver/Application                                | 13         |

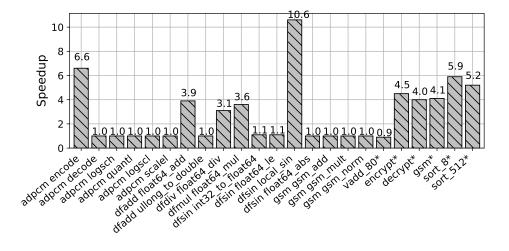

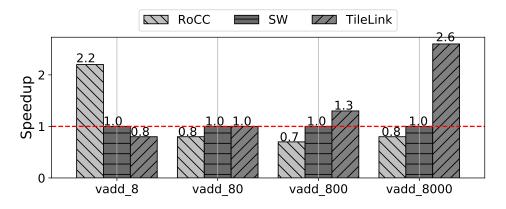

| 2.3        | RoCC Accelerators SpeedUp Compared to Software(* indicates accelerator with                           |            |

|            | pointer type inputs)                                                                                  | 15         |

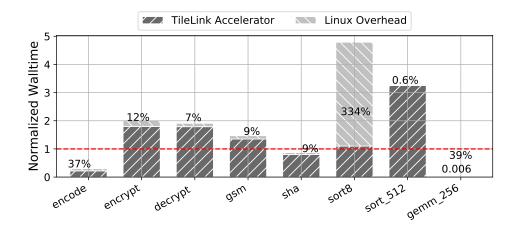

| 2.4        | Tilelink Accelerators with Linux Driver                                                               | 16         |

| 2.5        | Different Coupling for <i>vadd</i> Accelerator                                                        | 16         |

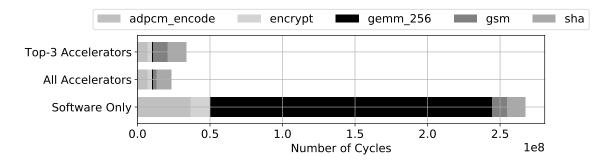

| 2.6        | Breakdown of key computational kernels in a hypothetical smart-house assis-                           |            |

|            | tant SoC. The top-3 accelerators for end-to-end performance are <i>adpcm_encode</i> ,                 |            |

|            | $gemm_256$ , and $encrypt$                                                                            | 17         |

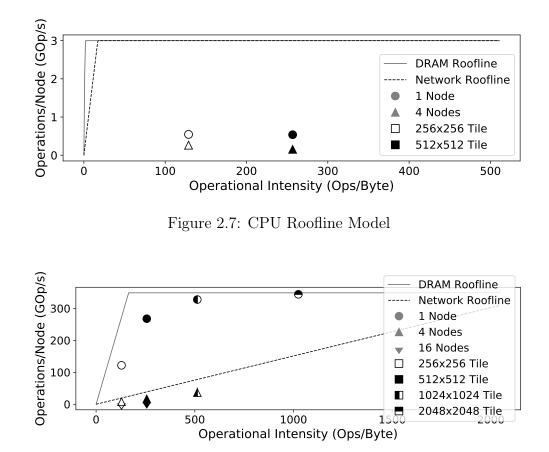

| 2.7        | CPU Roofline Model                                                                                    | 19         |

| 2.8        | Accelerator Roofline Model                                                                            | 19         |

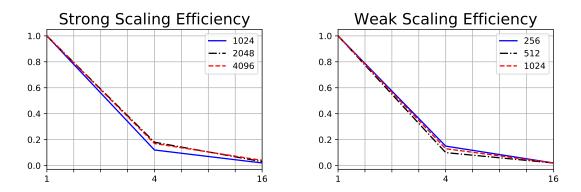

| 2.9        | Scaling Efficiency                                                                                    | 20         |

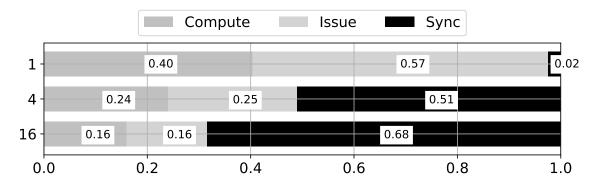

| 2.10       | DGEMM Runtime Breakdown for $1024 \times 1024$ Tiles                                                  | 20         |

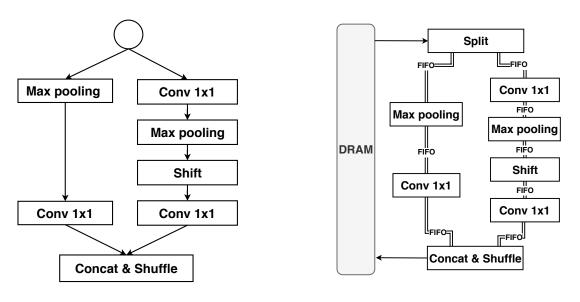

| 2.11       | DiracDeltaNet                                                                                         | 21         |

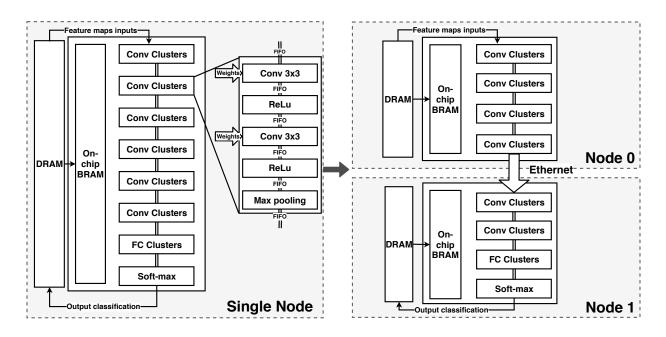

| 2.12       | Hardware Design                                                                                       | 21         |

| 2.13       | Multi-node accelerators, connected via Ethernet                                                       | 23         |

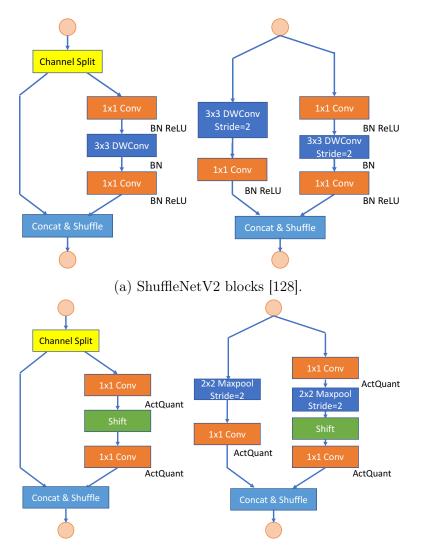

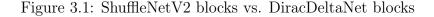

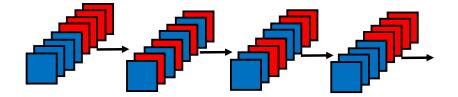

| 3.1        | ShuffleNetV2 blocks vs. DiracDeltaNet blocks                                                          | 33         |

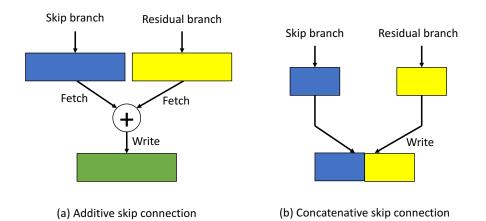

| 3.2        | Additive Skip Connections vs. Concatenative Skip Connections. Rectangles                              |            |

|            | represent data tensors                                                                                | 34         |

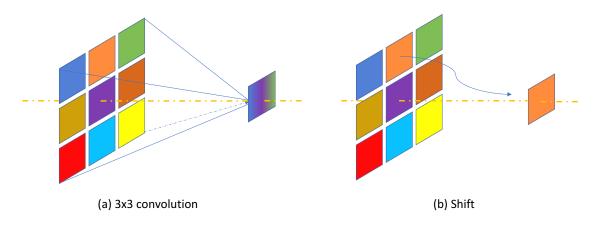

| 3.3        | $3 \times 3$ Convolution vs. Shift. In $3 \times 3$ convolutions, pixels in a $3 \times 3$ region are |            |

|            | aggregated to compute one output pixel at the center position. In the shift                           | ~ ~        |

| 0.4        | operation, a neighboring pixel is directly copied to the center position.                             | 35         |

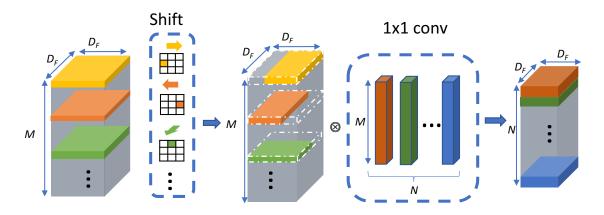

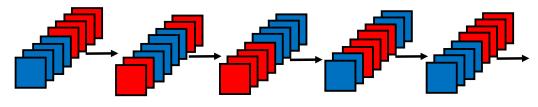

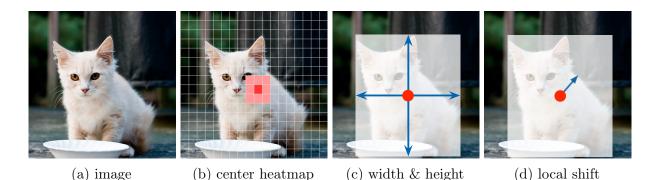

| 3.4        | Using shift and $1 \times 1$ convolutions to replace $3 \times 3$ convolutions. This figure is        | <u>م</u> ۲ |

| ۰ <i>۲</i> | from $[206]$                                                                                          | 35         |

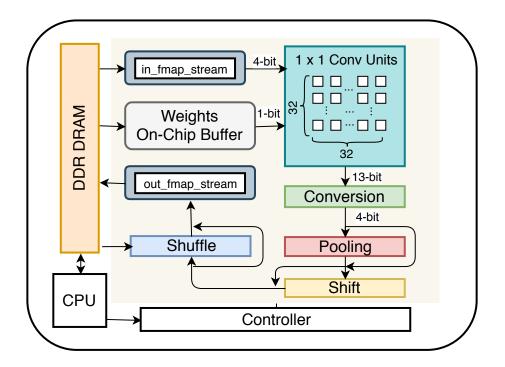

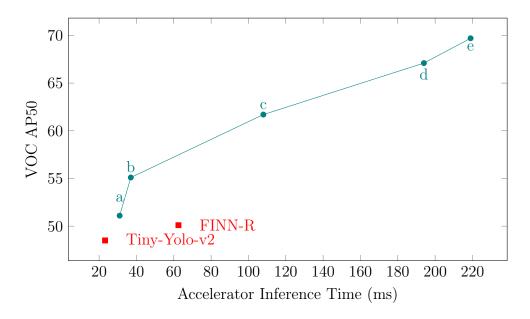

| 3.5        | Transpose Based Shuffle (ShuffleNetV2) vs. Our HW Efficient Shuffle (DiracDeltaNet)                   | 36         |

| 3.6        | Quantization Grid                                                                                     | 38         |

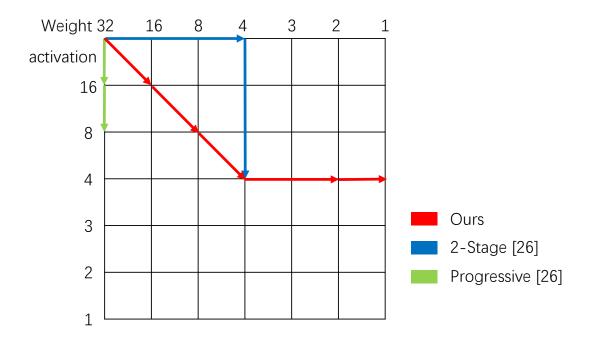

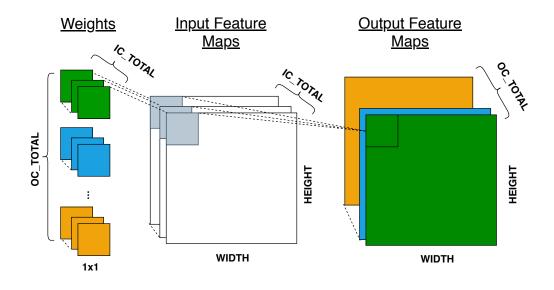

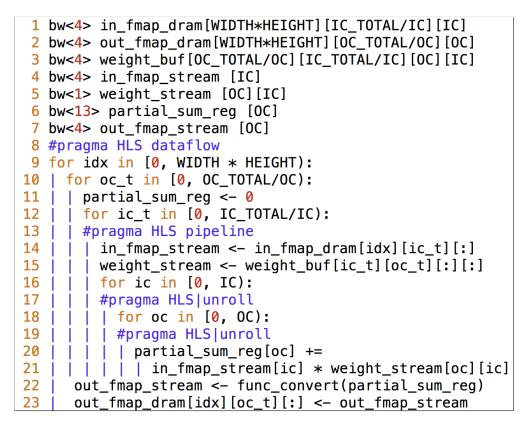

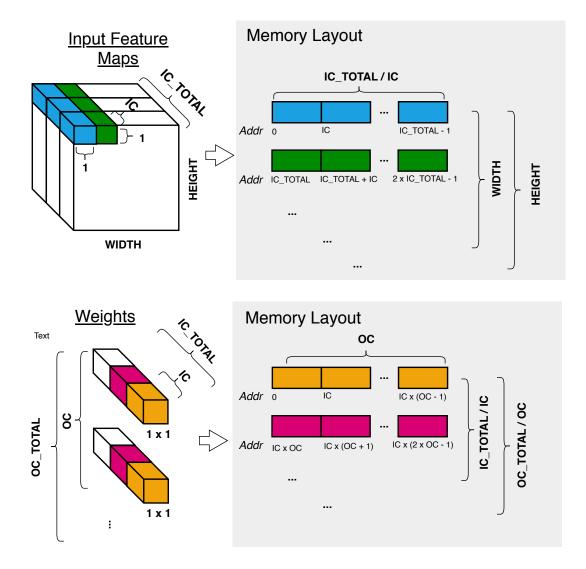

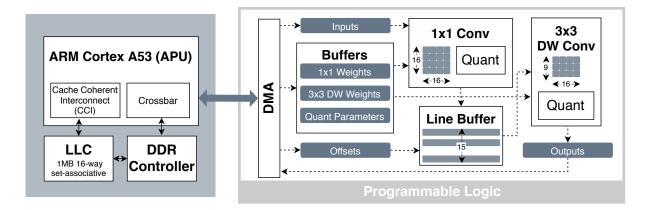

| 3.7        | Accelerator Architecture                                                                              | 41         |