### Hybrid Switched-Capacitor Converters for High-Performance Power Conversions

Wen Chuen Liu

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-25 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-25.html

May 1, 2021

# Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Acknowledgement

I would like to express my sincere gratitude to my advisor, Professor Robert Pilawa. Without his support and guidance throughout the years, all of my hard work might not lead to today's success. Besides that, I am grateful to get professional and insightful advice with the Professor Van Carey, Professor Ali Niknejad, and Professor Seth Sanders. Last but not least, it was my pleasure to be part of Pilawa's team. Everyone in the team not only has a very high passion for their work but also with high engineering curiosity. I have learned a lot from them, not only as an engineer but also as a person! Thank you very much.

#### Hybrid Switched-Capacitor Converters for High-Performance Power Conversions

by

#### Wen Chuen Liu

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert C. N. Pilawa-Podgurski, Chair Professor Van P. Carey Professor Ali M. Niknejad Professor Seth R. Sanders

Spring 2020

Copyright © 2020

by

Wen Chuen Liu

#### Abstract

Hybrid Switched-Capacitor Converters for High-Performance Power Conversions

by

#### Wen Chuen Liu

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert C. N. Pilawa-Podgurski, Chair

High-performance power conversions are essential in many applications, especially in the fast-growing computing industries as well as the wireless sensor networks. A common example in mobile devices is the dc-dc converter that converts the energy from a 4 V Li-ion battery to 1 V CPU / GPU chips, where efficiency and form factor are of the most important concerns. Meanwhile, the source voltage increases with the processed power to reduce wire conduction loss, e.g. 48 V DC grid for data centers. In particular, a hybrid approach has shown great potential in achieving high efficiency, high power density and high conversion ratio, due to its efficient passives and switch utilization compared to the conventional buck and switched capacitor (SC) converters.

In this work, the development of a hybrid or resonant SC (ReSC) converter, along with its soft-charging feature, is illustrated to address the fundamental limits of conventional SC converters and efficiently utilize the high energy density of capacitors. On top of that, various SC topologies are synthesized from a single unit cell for obtaining higher conversion ratios. While several optimization approaches for switch utilizations have been established in recent studies, they mainly focus on the ideal switch model but with the absence of practical considerations. Therefore, a more comprehensive design and comparison framework for commercially available switches and passive components with various voltage domains will be elaborated throughout this work, in conjunction with the analysis and experimental results. The proposed framework serves as a selection guideline for topologies, and it is further solidified through various power converters with optimized switch employment, i.e. an on-chip 4-to-1 V Dickson converter and an on-chip three-level boost converter implemented using the custom switch sizing and voltage rating in 65 nm CMOS process; a 48-to-4 V two-stage ReSC and a 4-to-1 bi-lateral energy resonant converter (BERC) built using ultra-low on-resistance discrete silicon switches.

One of the most critical challenges for all hybrid SC converters is the flying capacitor balancing issues. Any occurrence of imbalance in the flying capacitor voltage leads to increased

voltage stress on the switching transistors; meanwhile, the inductor current ripple is increased leading to higher conduction loss. An auto-capacitor-compensation pulse frequency modulation (ACC-PFM) controller for three-level converters is proposed to address it by inherent negative feedback between unbalanced voltage and injected charge. The hybrid approach employed in ACC-PFM, i.e. peak current-mode control with constant-off time and valley current-mode with constant-on time, establishes not only a balanced flying capacitor voltage but also a full-range output voltage regulation.

To further improve the efficiency and power density, two main types of floating supplies, i.e. voltage borrowing technique (employ an existing voltage) and bootstrap circuit (generate a new voltage), are introduced, compared and implemented in different situations. It is found that the capacitance density ratio between the transistor gate capacitance and available capacitors determines which type of floating supplies provides a more area-efficient solution. On the other hand, the gate driving of a power MOSFET is investigated. A segmented gate driver with multiple driving strengths is proposed, which is dedicated to reducing the ringing issue by a low-strength driver and maintaining a low conduction loss by a high-strength gate driver after the ringing-sensitive region. Gate driving techniques including floating supplies and segmented gate drivers are also required by other classes of power converters, particularly when dealing with high voltage using low-voltage devices.

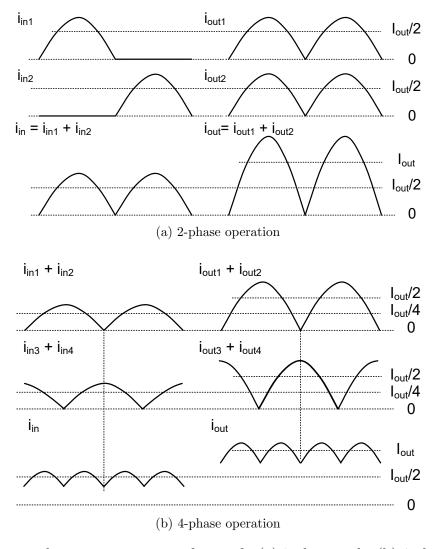

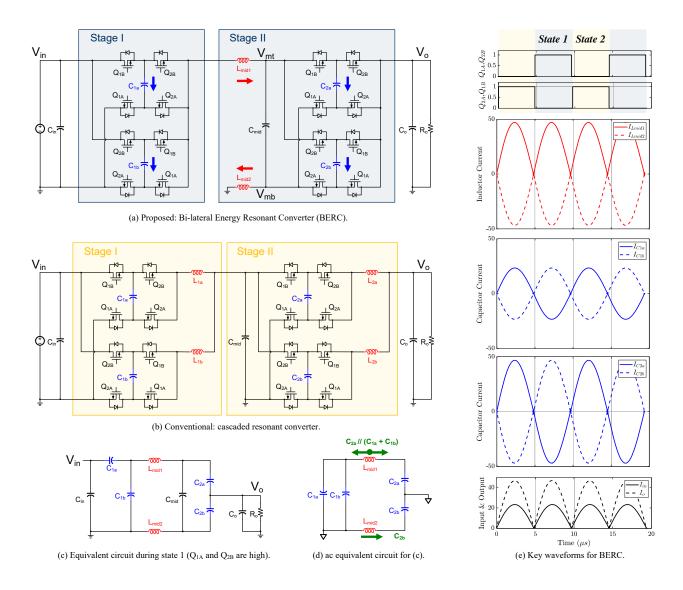

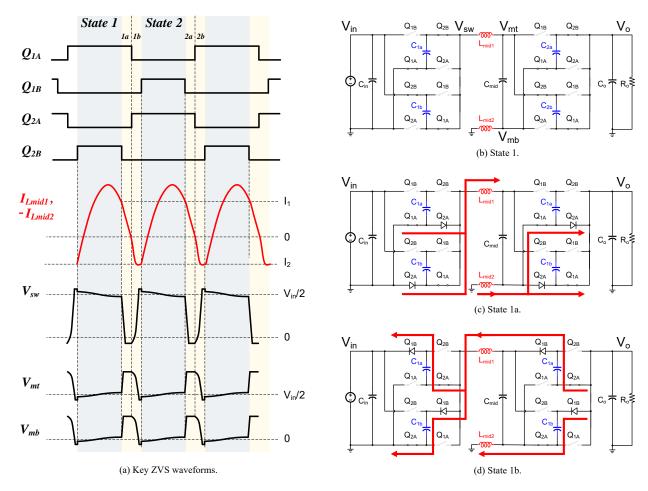

Lastly, passive reduction techniques are developed to further enhance the energy utilization of the passive components, along with the quantitative analysis of multiphase interleaving in hybrid SC converters. A novel BERC concept merges the resonant inductors for the multistage approach, by simultaneously using voltage- and current-type hybrid SC converters. Both passive reduction techniques not only significantly reduce the converter size, but they are also beneficial for high-current applications since lower inductance with higher saturation current can be employed. Therefore, an excellent high power density can be achieved.

Several on-chip and discrete hardware prototypes for hybrid SC converters have been implemented, measured and showing promising performance in *efficiency*, *power density* and *conversion ratios* compared to prior arts, which are suitable for applications ranging from point-of-load (PoL), data center power deliveries and energy harvesting. Meanwhile, the hybrid approach offers a lot more design freedom in optimizing the switches and passives utilization, providing more opportunities in further improvement and research topics for high-performance power converters.

To my family

# Contents

| Co | ntents                                                                                                                                                                                                                                                                                                 | ii                                           |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Li | t of Figures                                                                                                                                                                                                                                                                                           | iv                                           |

| Li | t of Tables                                                                                                                                                                                                                                                                                            | ix                                           |

| 1  | Introduction                                                                                                                                                                                                                                                                                           | 1                                            |

| 2  | Fundamentals of Power Converters  2.1 Basic Elements - Passives and Actives                                                                                                                                                                                                                            | <b>5</b> 5 7 9                               |

| 3  | Soft-Charging Techniques  3.1 Two-Capacitor Problem — Hard Charging                                                                                                                                                                                                                                    | 11<br>11<br>13<br>13<br>18                   |

| 4  | Topologies of Hybrid SC Converter  4.1 Generation and Synthesis of SC Topologies  4.2 Output Voltage Regulation  4.3 Optimal Switch Utilization  4.4 Output Conductance Density — Figure of Merit (FoM)  4.5 Topological Comparison Framework  4.6 Practical Layout Consideration  4.7 Chapter Summary | 22<br>22<br>27<br>28<br>37<br>39<br>40<br>44 |

| 5  | On-Chip Hybrid Dickson for High Switch Utilization  5.1 Operating Principle                                                                                                                                                                                                                            | 46<br>47<br>51<br>52<br>57                   |

| $\mathbf{B}^{\mathbf{i}}$ | Bibliography 1 |                                                                                                          |                   |  |

|---------------------------|----------------|----------------------------------------------------------------------------------------------------------|-------------------|--|

| 9                         | Cor            | nclusions                                                                                                | 128               |  |

|                           | 8.3<br>8.4     | Bi-lateral Energy Resonance Converter (BERC)                                                             | 122<br>127        |  |

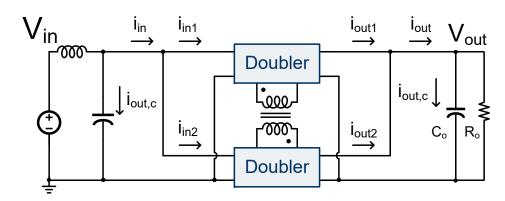

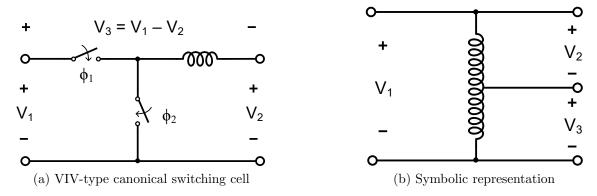

|                           | 8.2            | Canonical Switching Cells for Hybrid Switched-Capacitor Converter                                        | 120               |  |

| 8                         | <b>Pas</b> 8.1 | sives Reduction Techniques  Filter Capacitor Ripple Reduction                                            | <b>116</b><br>117 |  |

|                           | 7.6            | Chapter Summary                                                                                          | 114               |  |

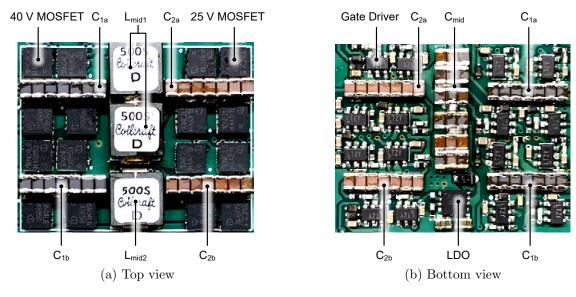

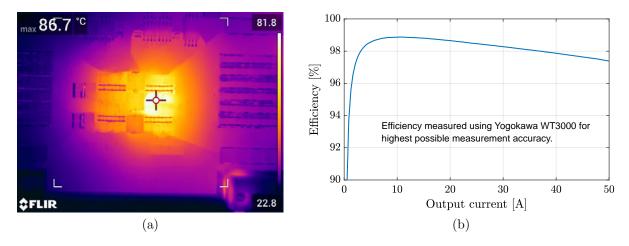

|                           | 7.5            | Measurement Results                                                                                      | 108               |  |

|                           | 7.4            | Floating Gate Driver Techniques                                                                          | 107               |  |

|                           | 7.3            | Zero Voltage Switching (ZVS) Techniques                                                                  | 102               |  |

|                           | 7.2            | Two-Stage Resonant SC Converter                                                                          | 99                |  |

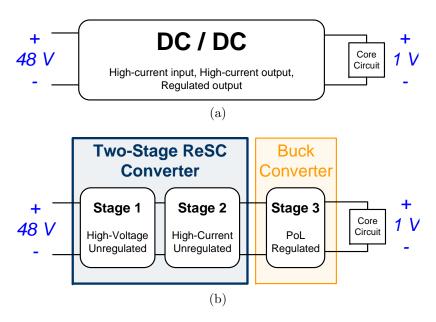

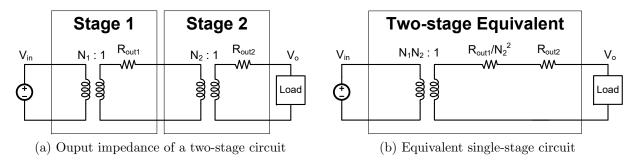

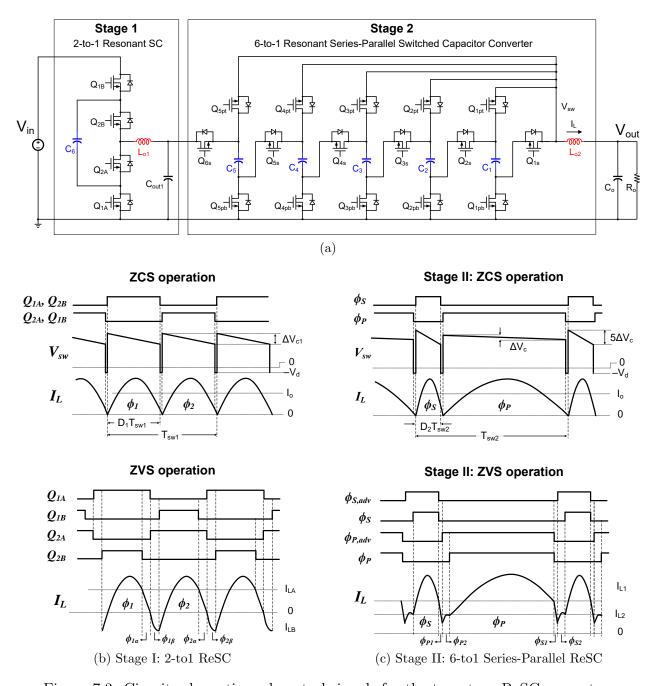

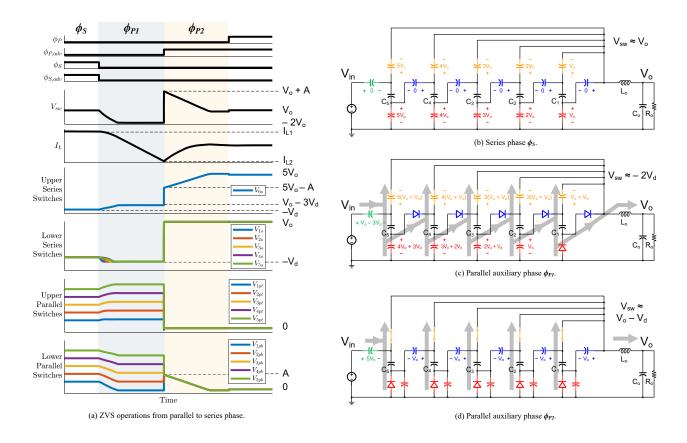

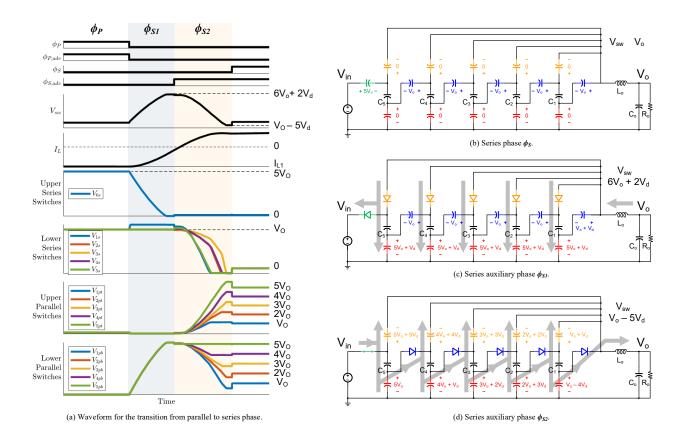

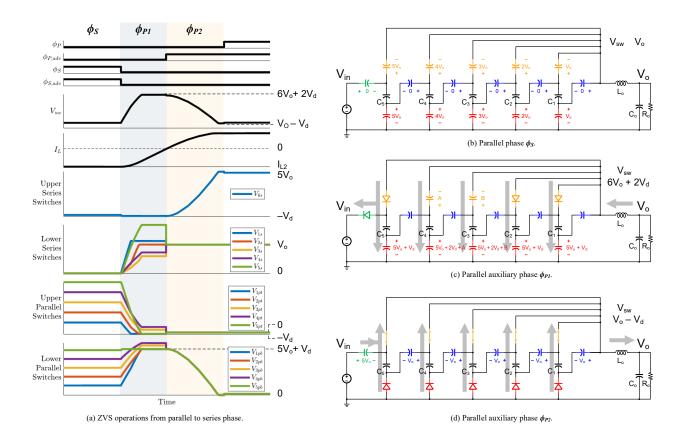

| 7                         | 7.1            | lti-stage Approach for High Conversion Ratios Output Impedance for Multi-stage Approaches                | 98                |  |

| -                         | ъ. г           |                                                                                                          | 97                |  |

|                           | 6.7            | Chapter Summary                                                                                          | 96                |  |

|                           | 6.6            | Measurement Results                                                                                      | 88                |  |

|                           | 6.5            | Key Functional Blocks                                                                                    | 85                |  |

|                           | 6.4            | Dual-Mode Timing Controller (DMTC)                                                                       | 82                |  |

|                           | 6.2<br>6.3     | Auto-Capacitor-Compensation Pulse Frequency Modulation (ACC-PFM) Delay-Equalized Level Shifter (D-Eq LS) | 74<br>79          |  |

|                           | 6.1            | Charge Flows of Flying Capacitors                                                                        | 72                |  |

| 6                         |                | Chip Flying Capacitor Balancing Techniques                                                               | <b>71</b>         |  |

|                           | 5.7            | Chapter Summary                                                                                          | 69                |  |

|                           | 5.6            | Measurement Results                                                                                      | 66                |  |

|                           | 5.5            | Segmented Gate Driver                                                                                    | 63                |  |

|                           |                |                                                                                                          |                   |  |

# List of Figures

| 1.1 | Applications that requested high-performance voltage step-up power conversion.                                                                                     |    |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

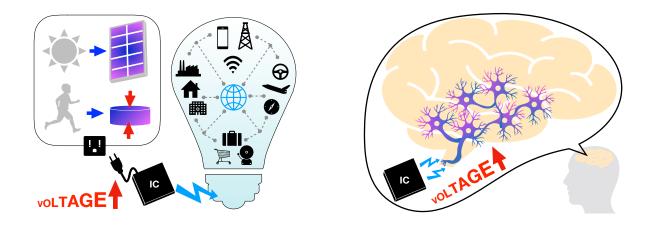

| 2.1 | Design requirement and framework for power converters                                                                                                              | 6  |  |  |

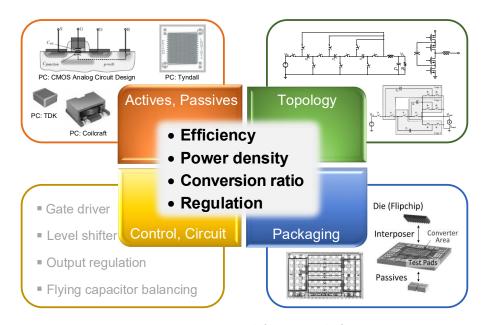

| 2.2 | Step response of various low-pass filters                                                                                                                          | 6  |  |  |

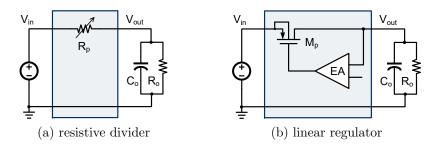

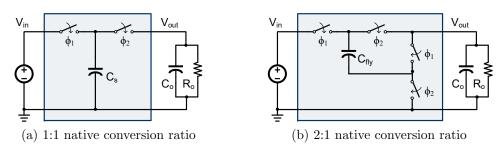

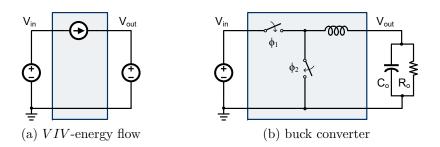

| 2.3 | Operating principle and schematic of a linear regulator                                                                                                            | 8  |  |  |

| 2.4 | Schematics of capacitor-based converters                                                                                                                           | 8  |  |  |

| 2.5 | Operating principle and schematic of a magnetic-based converter                                                                                                    | 8  |  |  |

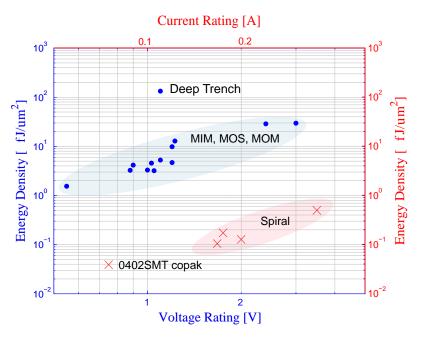

| 2.6 | Energy density of on-chip inductors and capacitors. Data points are collected from integrated solutions with different fabrication processes in literature review. | 10 |  |  |

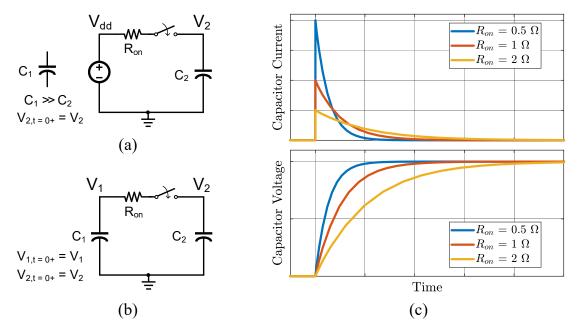

| 3.1 | Capacitor charging by (a) a voltage source and (b) another capacitor, along with                                                                                   |    |  |  |

|     | the (c) capacitor voltage and current waveform                                                                                                                     | 12 |  |  |

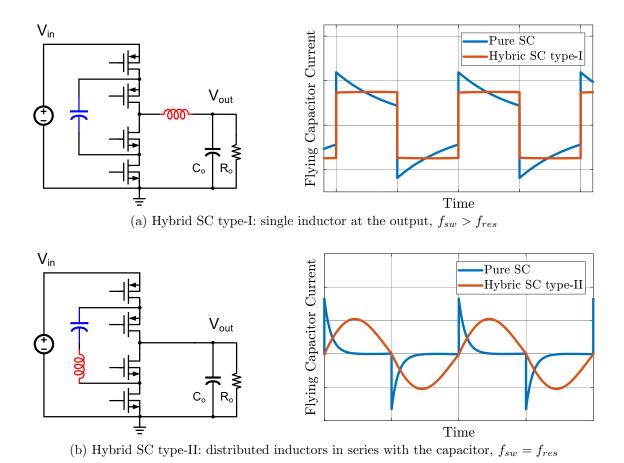

| 3.2 | Smooth capacitor current in hybrid switched-capacitor converters                                                                                                   | 14 |  |  |

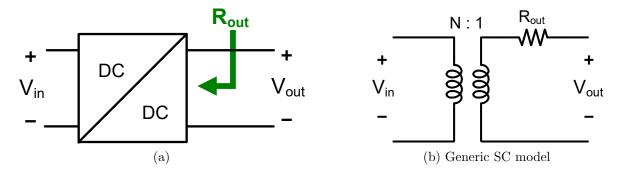

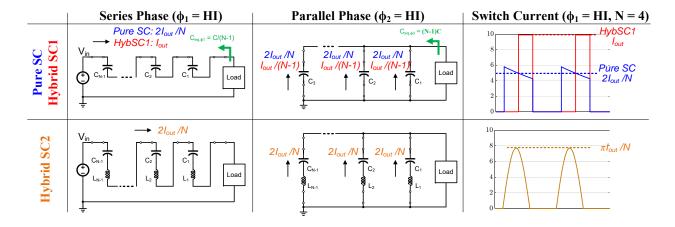

| 3.3 | Output impedance for characterizing power converters                                                                                                               | 15 |  |  |

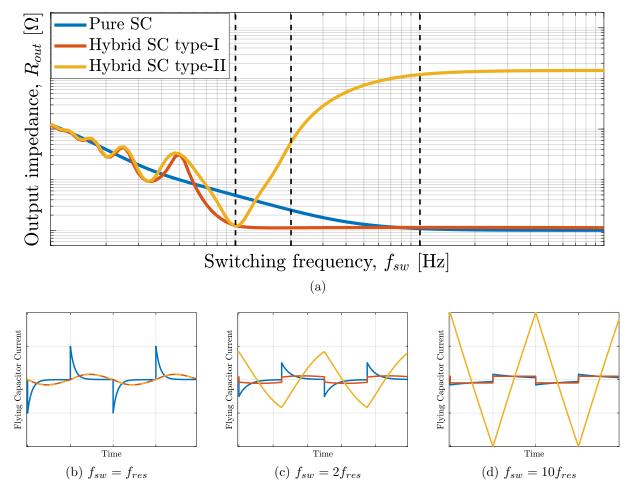

| 3.4 | Output impedance and time-domain waveforms for pure SC, hybrid SC type-I and hybrid SC type-II                                                                     | 16 |  |  |

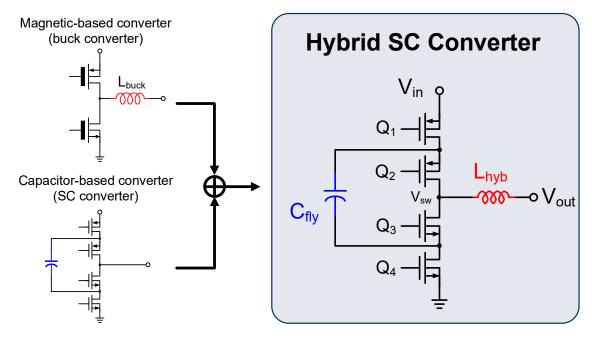

| 3.5 | Hybrid SC converter — a merged combination of magnetic-based and capacitor-                                                                                        |    |  |  |

|     | based converters                                                                                                                                                   | 18 |  |  |

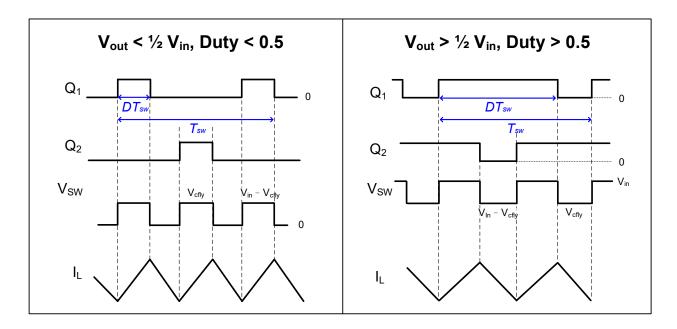

| 3.6 | Operational waveforms of a three-level buck converter                                                                                                              | 19 |  |  |

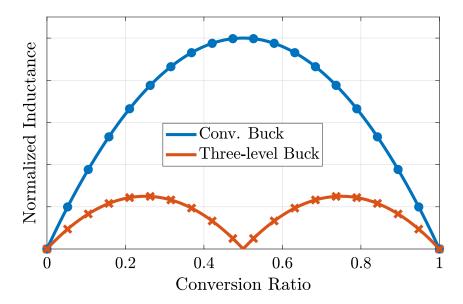

| 3.7 | Inductance requirement reduction in a hybrid SC converter                                                                                                          | 20 |  |  |

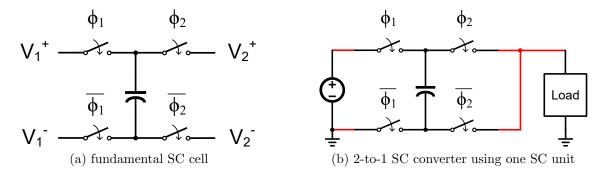

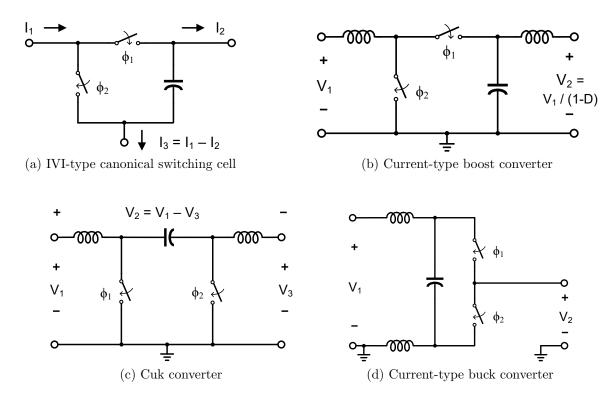

| 4.1 | Fundamental SC cell and 2-to-1 converter                                                                                                                           | 23 |  |  |

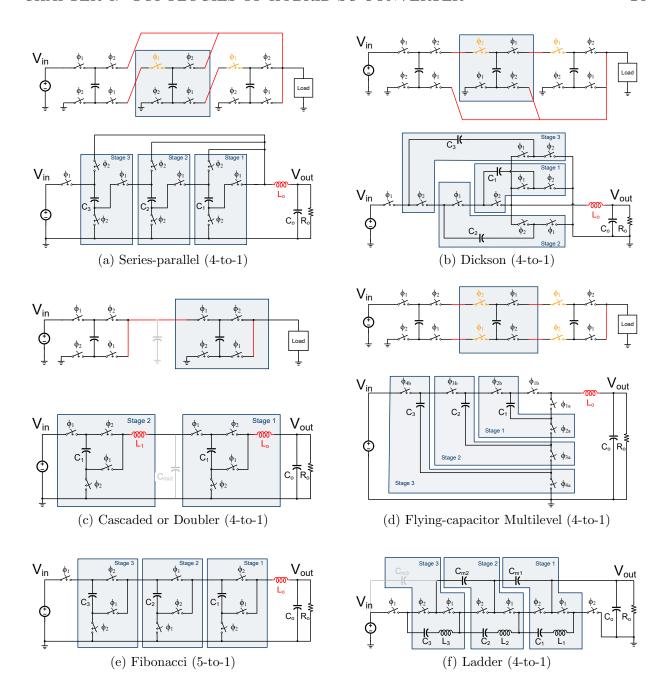

| 4.2 | SC topologies generation through recursively added fundamental SC cells                                                                                            | 24 |  |  |

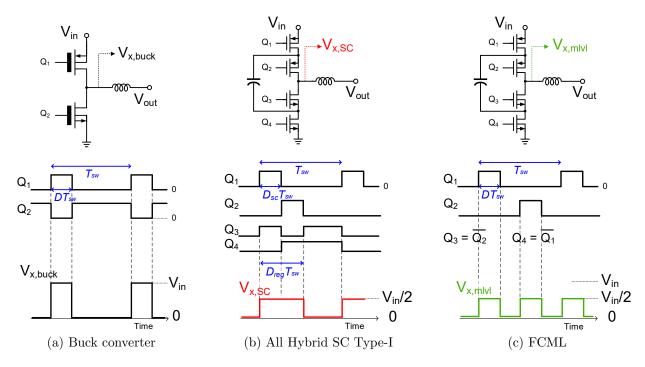

| 4.3 | Switching scheme to achieve output voltage regulation for a buck converter and                                                                                     |    |  |  |

|     | hybrid SC topologies                                                                                                                                               | 27 |  |  |

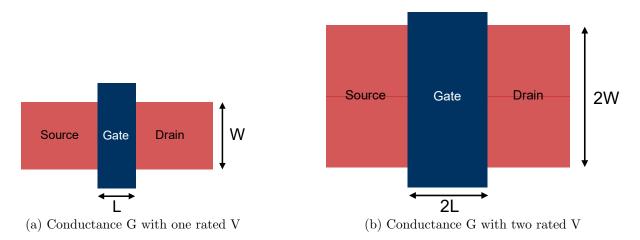

| 4.4 | MOSFET transistor scaling                                                                                                                                          | 29 |  |  |

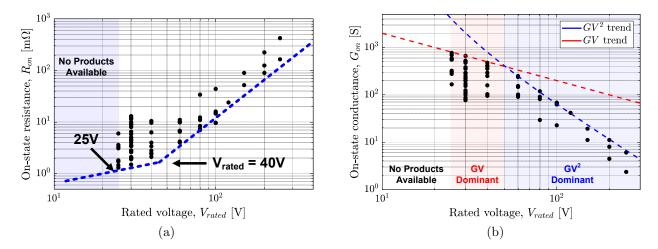

| 4.5 | Survey of high-performance discrete silicon transistors. Data points are from active Infineon Optimos <sup>TM</sup> products in S3O8 package (3.3 mm x 3.3 mm x 1  |    |  |  |

|     | mm). [64]                                                                                                                                                          | 30 |  |  |

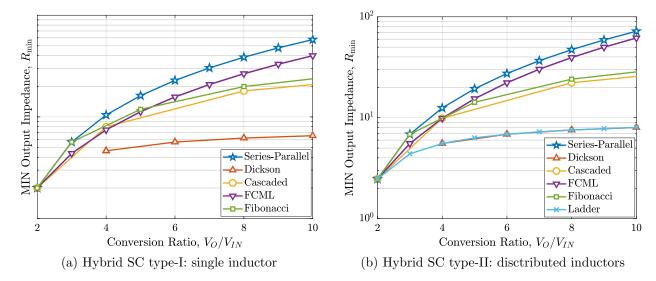

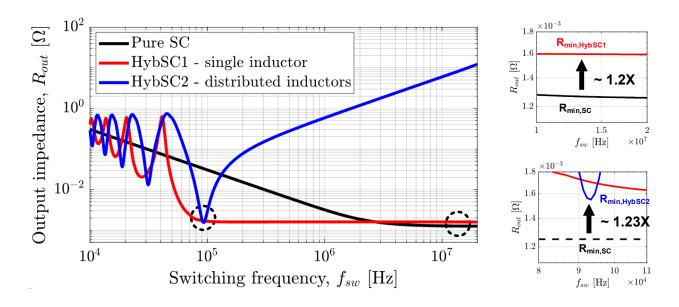

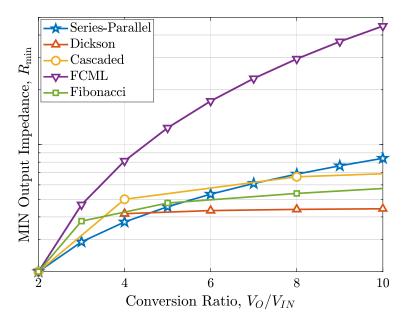

| 4.6 | Optimal output impedance given fully customized switches, and the switch area                                                                                      |    |  |  |

|     | constraint is $\sum G_{on}V_{rated}^2$                                                                                                                             | 32 |  |  |

| 4.7 | Optimal output impedance given the uniform $V_{rated}$ switches, and the switch area                                                                               |    |  |  |

|     | constraint is $\sum G_{on}$ ( $V_{rated}$ is not considered due to unavailable voltage selection).                                                                 | 33 |  |  |

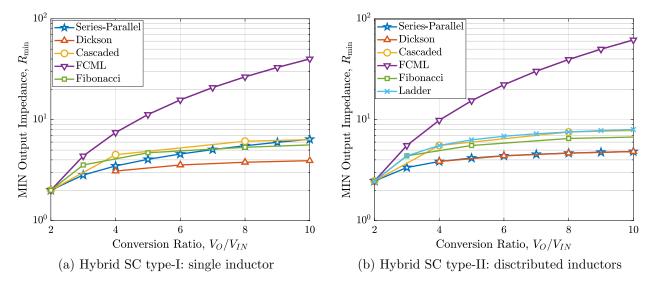

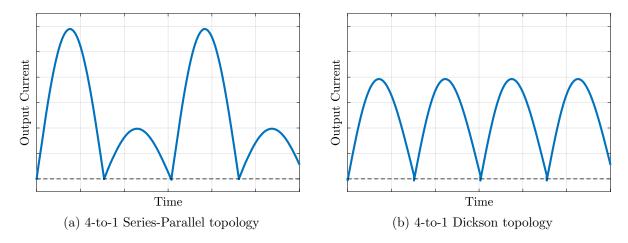

| 4.8<br>4.9 | Switch current of an N-to-1 series-parallel topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34<br>35 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.10       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36       |

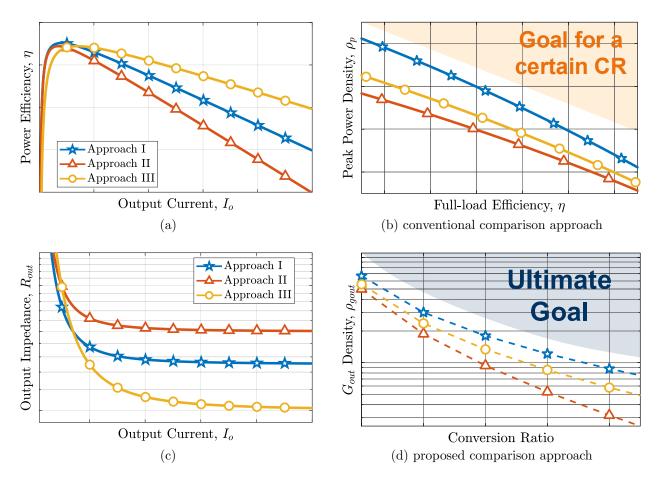

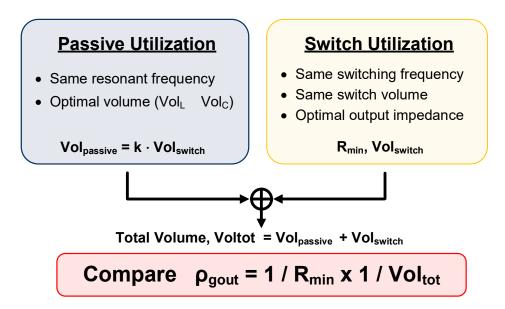

| 4.11       | Development of the proposed figure of merit (FoM): (a) efficiency vs. output current, (b) conventional comparison approach - peak power density vs. full-load current, (c) output impedance vs. output current and (d) proposed comparison approach. Three different cases are exemplified, with the scenario as follows: i) Topology I and II have the same form factor but different performance, ii) dual-phase interleaved topology II has some advantage in passive reduction. All of the compared cases have the same input voltage and conversion ratio unless otherwise | 30       |

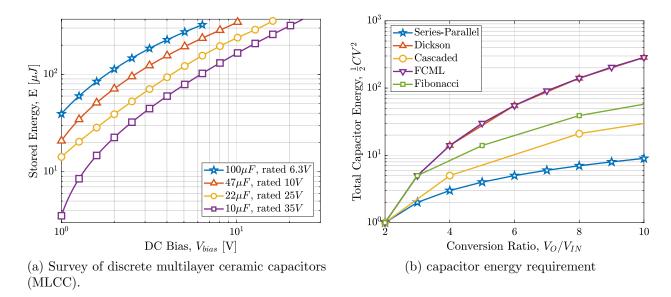

| 4.12       | Stated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37       |

| 4 10       | capacitor volume and fair comparison.) and capacitor energy requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40       |

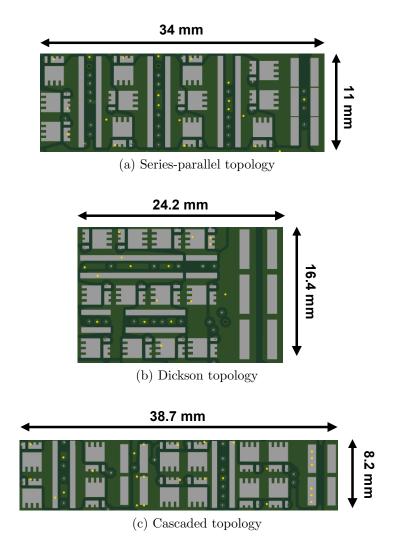

|            | Comparison framework using output conductance density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41<br>42 |

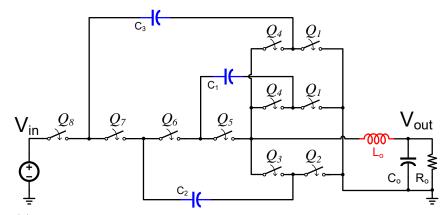

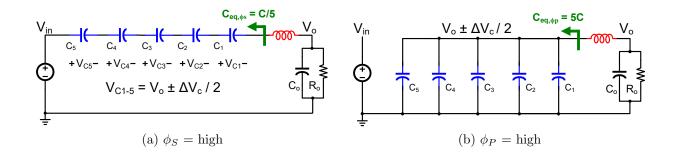

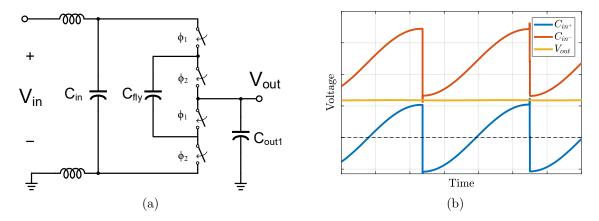

| 5.1        | A 4-to-1 hybrid Dickson converter and its switching signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47       |

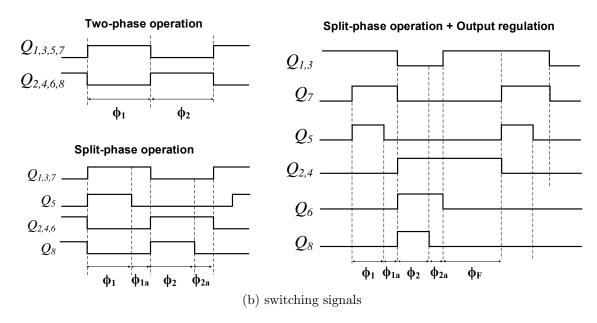

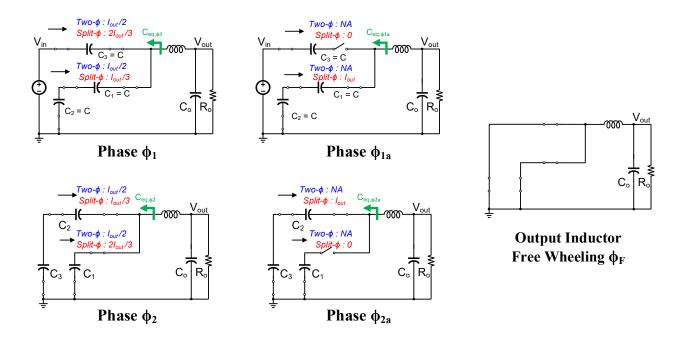

| 5.2        | Operational states of a 4-to-1 hybrid Dickson converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48       |

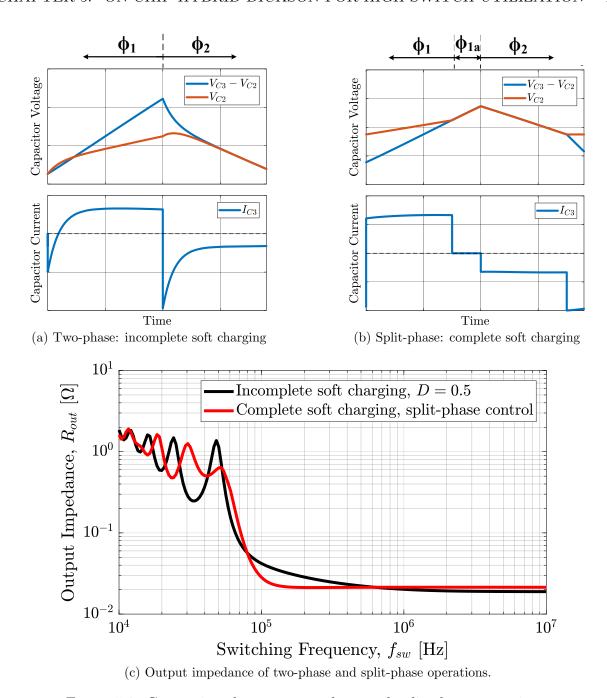

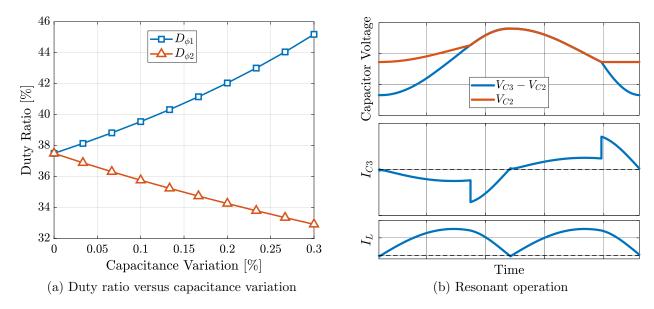

| 5.3<br>5.4 | Comparison between two-phase and split-phase operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49       |

|            | complete soft-charging operation is achieved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50       |

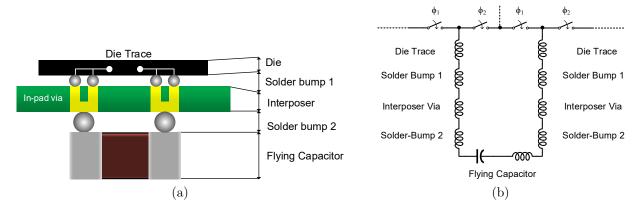

| 5.5        | Parasitic inductance of a power converter using flip-chip ball grid array (FCBGA).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

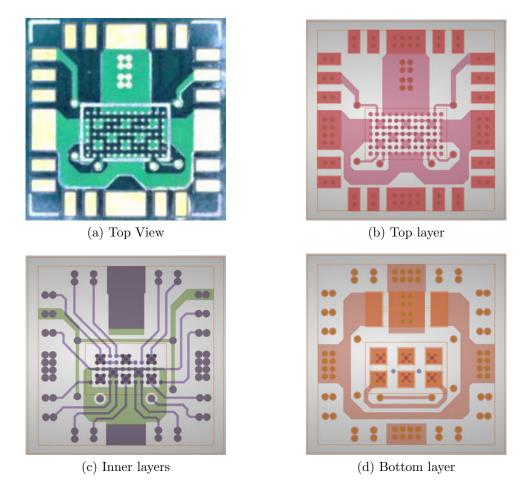

| 5.6        | Chip interposer and its each layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55       |

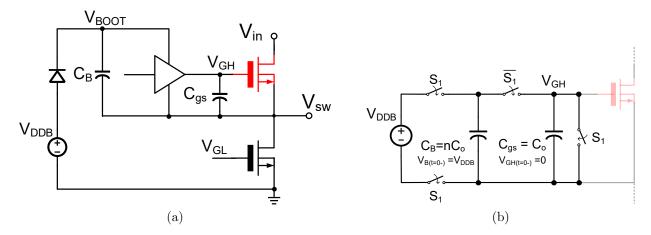

| 5.7        | (a) Schematic and (b) simplified circuit of a conventional bootstrap circuit for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.8        | driving high-side NMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57       |

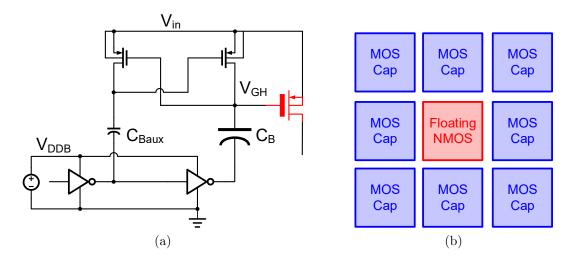

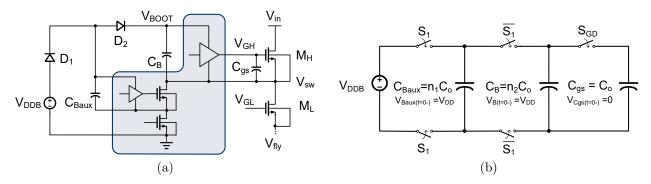

|            | circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58       |

| 5.9        | (a) Schematic and (b) simplified circuit of a modified bootstrap circuit for driving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|            | high-side NMOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59       |

|            | Voltage borrowing technique in a 4-to-1 Dickson converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60       |

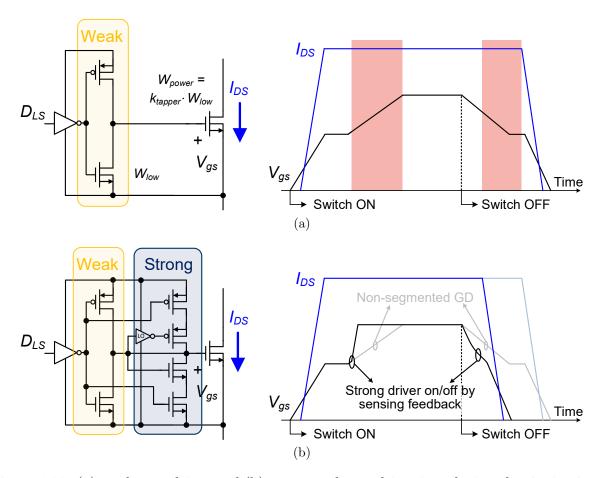

| 5.11       | (a) weak gate driver and (b) segmented gate driver in reducing the ringing issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63       |

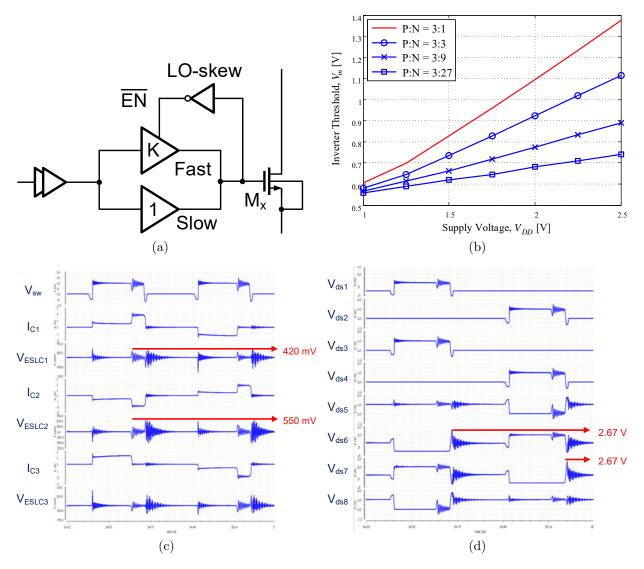

| 5.12       | (a) Simplified schematic of segmented gate drivers, (b) inverter threshold design of the $V_{plateau}$ -sensing inverter, (c) current and voltage across the parasitic inductance and (d) switch blocking voltage when applying with the segmented gate                                                                                                                                                                                                                                                                                                                         |          |

|            | driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65       |

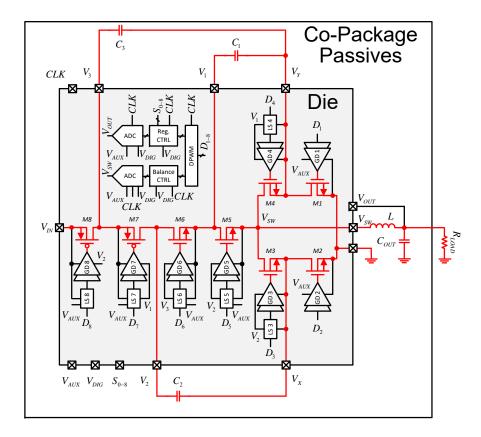

| 5.13       | Block Diagram and Packaging of a 4-to-1 Dickson Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66       |

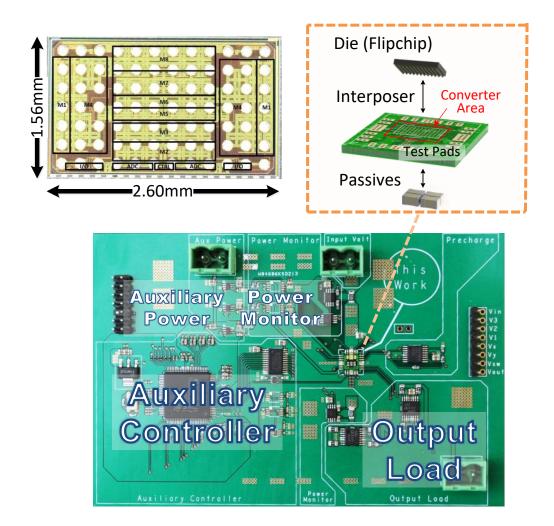

|            | Whole testing system with the die photo, converter packaging and testing board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67       |

|            | Key waveforms of the proposed 4-to-1 Dickson converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68       |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 5.16         | Efficiency measurement and performance comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

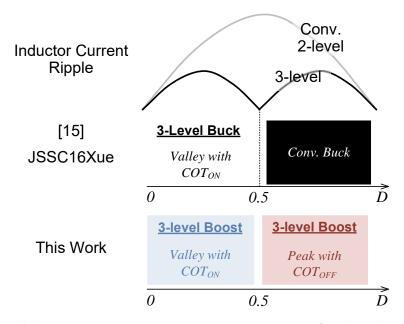

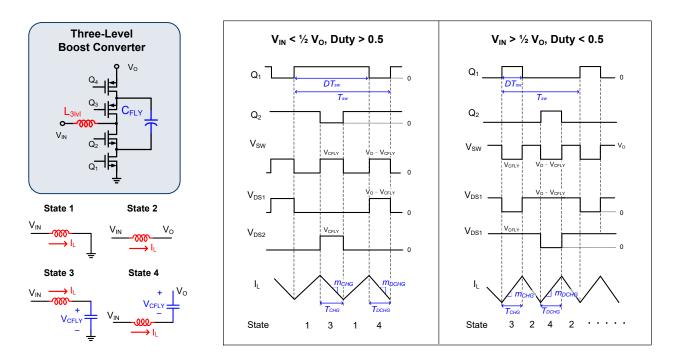

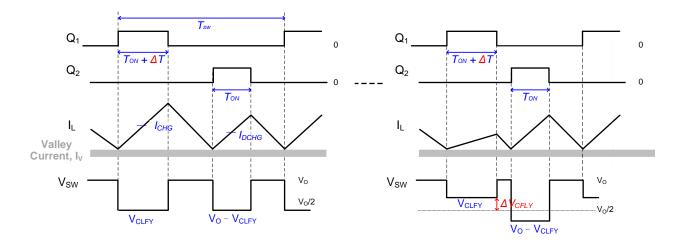

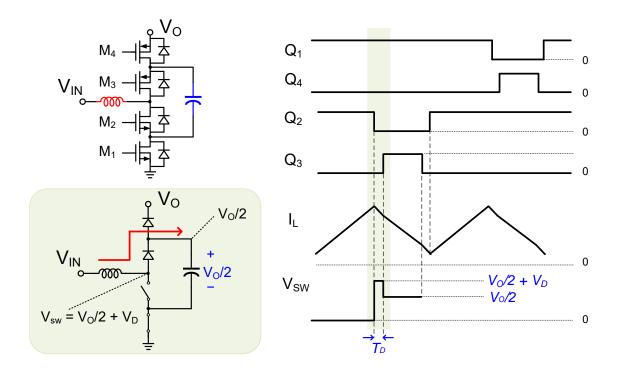

| 6.1<br>6.2   | Full-duty-ratio region capacitor compensation for three-level converters Circuit configurations and operational waveforms of a three-level boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72<br>73   |

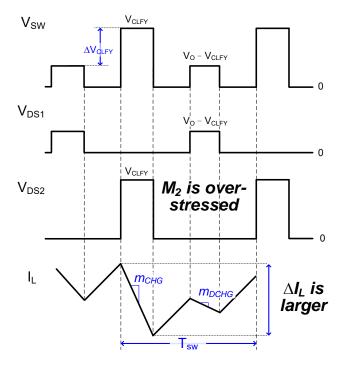

| 6.3          | Flying capacitor unbalance along with the issues in switch blocking voltage and inductor ripple, under the condition of $V_{CFLY} > V_O/2$ when $D > 0.5.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74         |

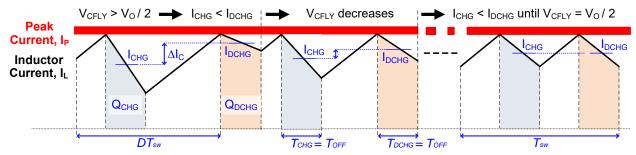

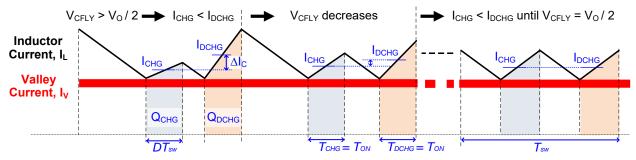

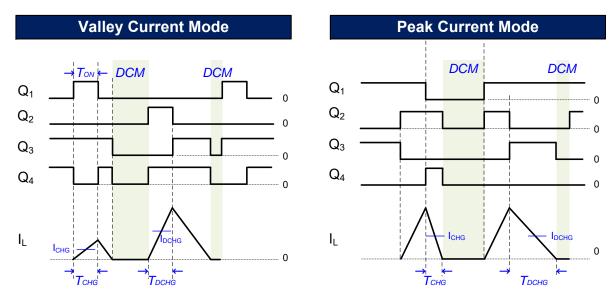

| 6.4          | Capacitor-compensation mechanism of the ACC-PFM controller over the entire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •          |

| 6.5          | operating range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>7</b> 5 |

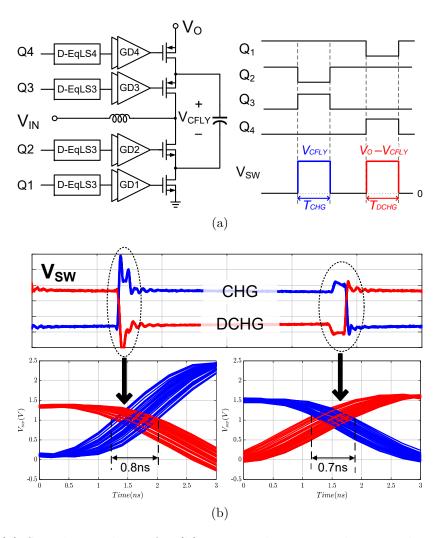

|              | tration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79         |

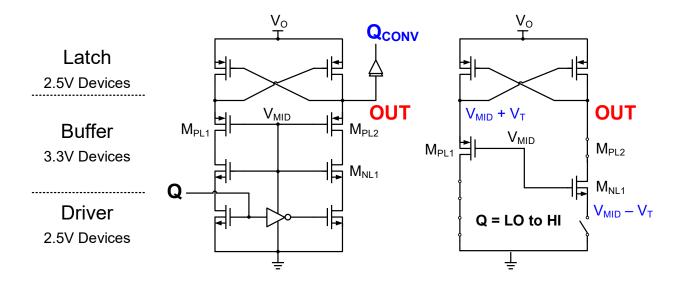

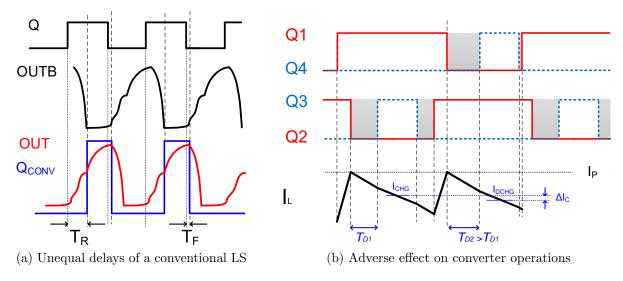

| 6.6<br>6.7   | Long falling delays in a conventional stacked up level shifter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80         |

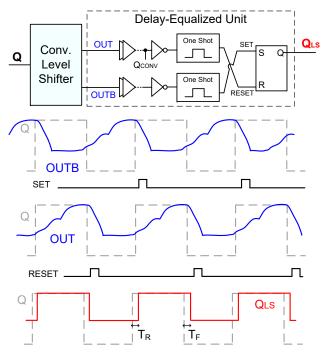

| 6.8          | Delay equalized level shifter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82         |

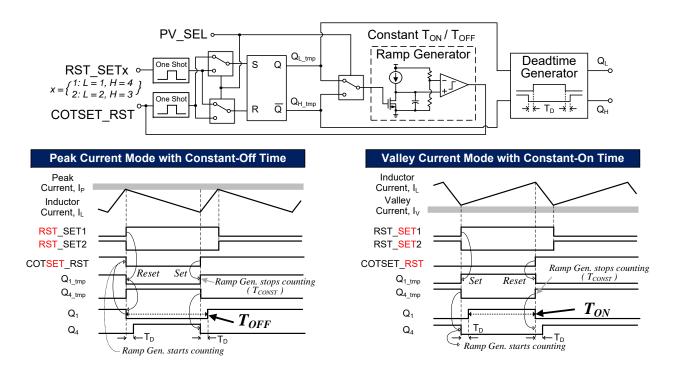

| 6.9          | Dual-mode timing controller (DMTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83         |

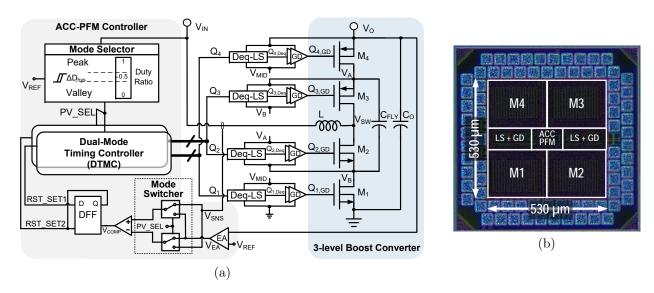

| 6.10<br>6.11 | Possible inaccuracy of ACC-PFM controller at high switching frequency operations.  (a) Block diagram and (b) die micrograph of an ACC-PFM controlled three-level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

| 0.11         | boost converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85         |

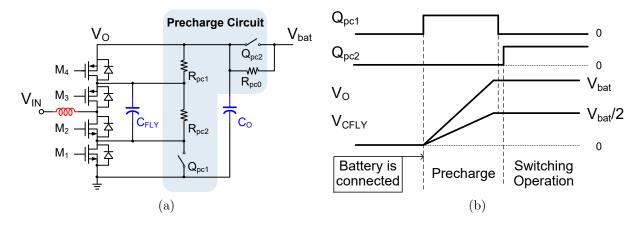

| 6 12         | Precharge circuit for three-level boost converters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87         |

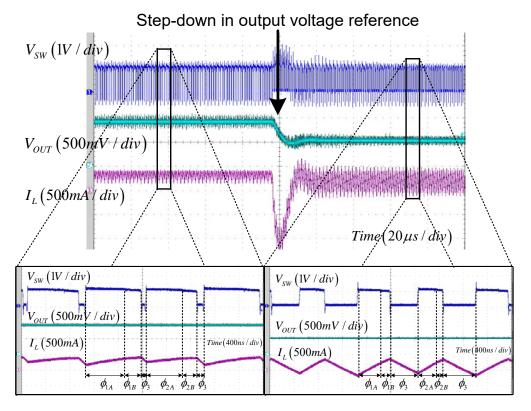

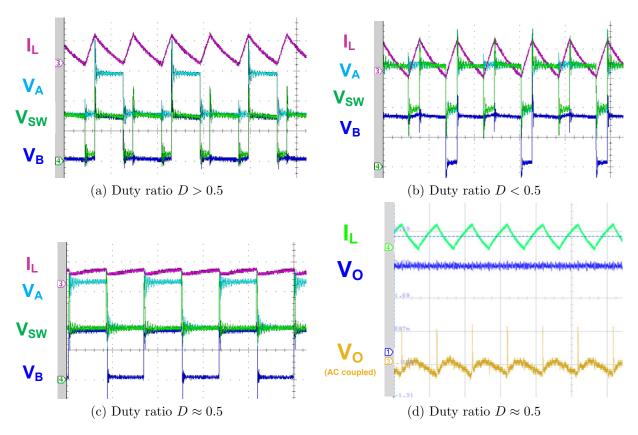

|              | Steady-state waveforms when (a) duty ratio $> 0.5$ , (b) duty ratio $< 0.5$ , and (c) duty ratio $\approx 0.5$ . (d) Output voltage ripple when duty ratio $> 0.5$ . The scales for waveforms are as follows, time: $1\mu s/\text{div}$ , $I_L$ : 200 mA/div, $V_A$ : 1 V/div, $V_B$ : 1 V/div, $V_S$ : 1 V/div, | 89         |

| 6 14         | Body diode conduction and overshoot at $V_{SW}$ of a three-level boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90         |

| 6.15         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50         |

|              | duty ratio for $Q_1$ and $Q_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91         |

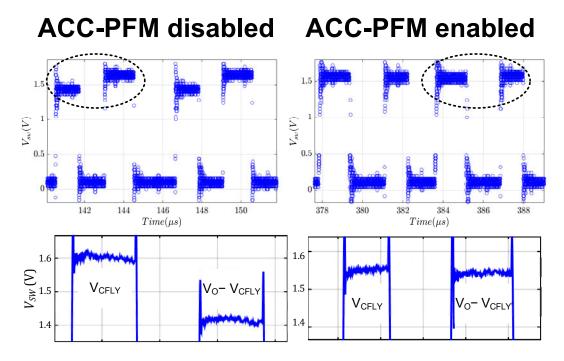

| 6.16         | Validation of the ACC-PFM's capacitor balancing mechanism. Measured pulse-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|              | heights that are even demonstrate effective balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 92         |

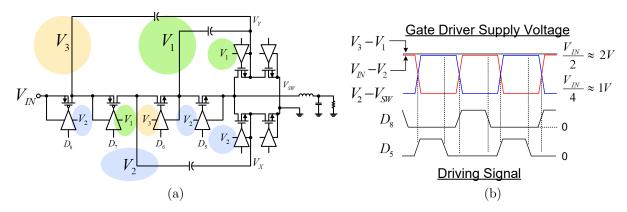

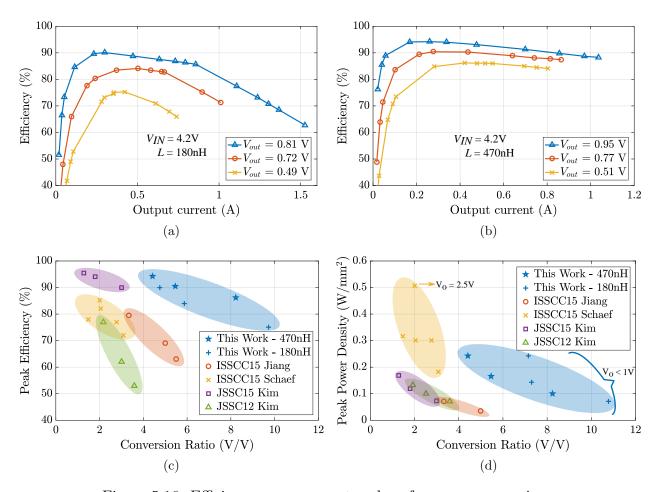

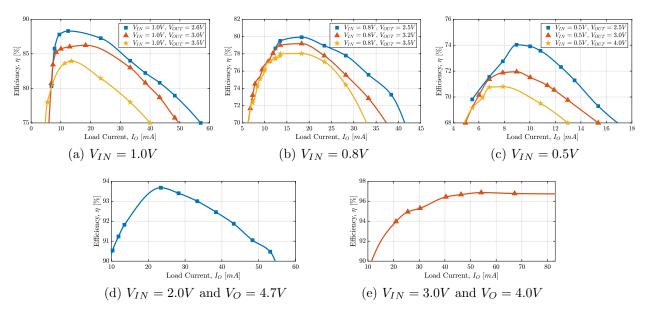

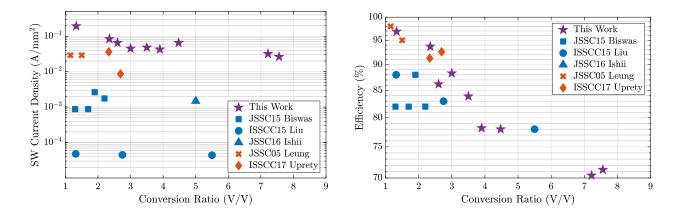

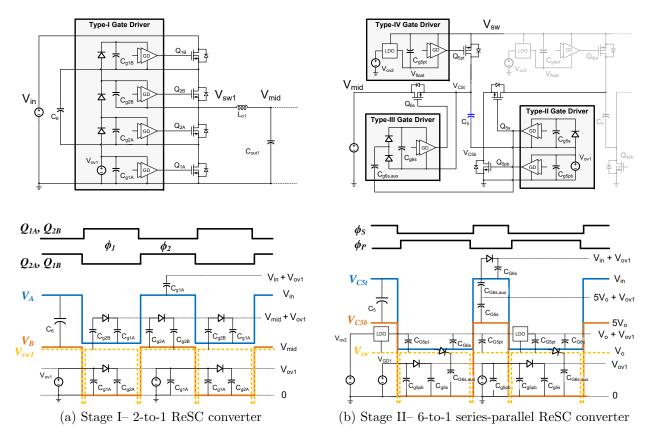

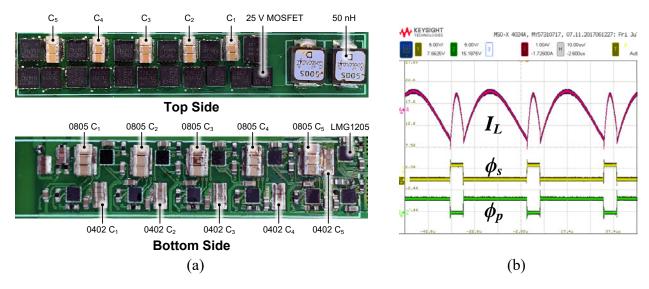

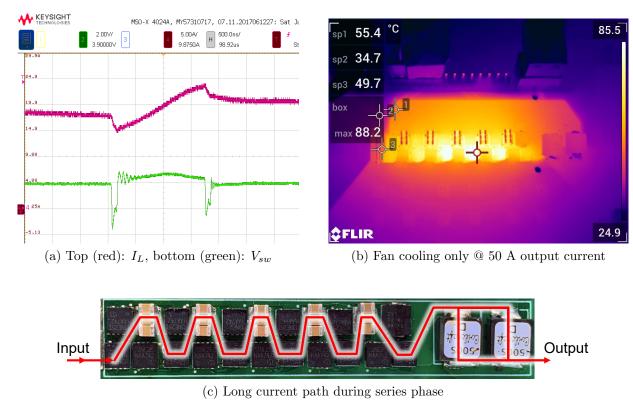

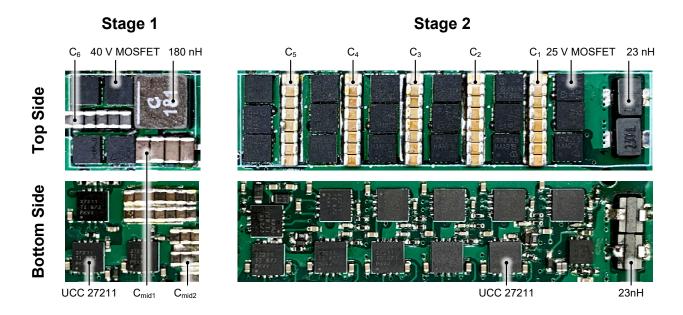

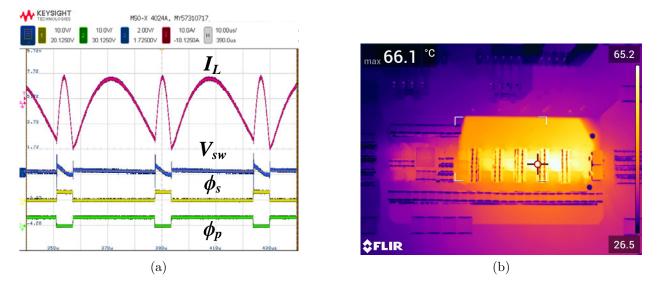

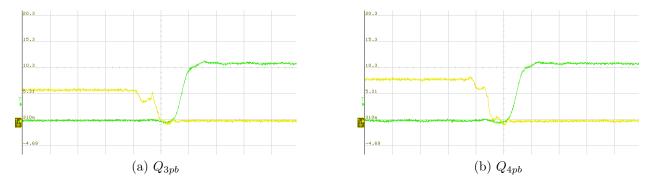

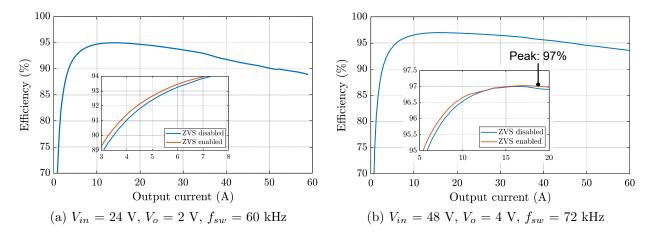

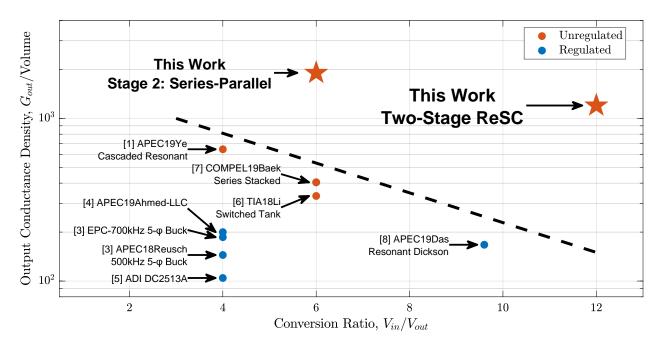

|              | Measured efficiency versus load current with various $V_{IN} - V_O$ conditions Efficiency versus conversion ratio compared to prior arts. Color code: purple - this work (three-level boost converter), red - conventional boost converter, blue -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93         |