# Improving FPGA Simulation Capacity with Automatic Resource Multi-Threading

Albert Magyar

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-24 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-24.html

May 1, 2022

Copyright © 2022, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Improving FPGA Simulation Capacity with Automatic Resource Multi-Threading

by

#### Albert Forte Magyar

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Krste Asanović, Co-chair Adjunct Assistant Professor Jonathan Richard Bachrach, Co-chair Professor Sanjit Seshia Associate Professor Kyle Steinfeld

Spring 2021

# Improving FPGA Simulation Capacity with Automatic Resource Multi-Threading

Copyright 2021 by Albert Forte Magyar

#### Abstract

Improving FPGA Simulation Capacity with Automatic Resource Multi-Threading

by

Albert Forte Magyar

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Krste Asanović, Co-chair

Adjunct Assistant Professor Jonathan Richard Bachrach, Co-chair

Modern system-on-a-chip (SoC) development is a highly complex process that spans multiple levels of design abstraction and cross-cutting requirements. With a rapidly evolving ecosystem of domain-specific accelerators and wide design spaces to search, the ability to rapidly evaluate potential chip designs has never been more important. In the modern chip-design landscape, field-programmable gate arrays (FPGAs) play a critical role in delivering this simulation capability due to their unique ability to emulate concrete, register-transfer level (RTL) designs at speeds sufficient to run real applications spanning trillions of cycles of simulated target-design execution. However, the use of FPGAs for logic emulation presents challenges, including the perennial difficulty of effectively mapping large target designs to the finite resources of a given FPGA platform.

To help address this challenge, this dissertation presents a novel approach to manage these limitations through the use of automatic resource-efficiency optimizations that reduce the number of FPGA resources required to faithfully implement cycle-accurate emulators of large chips, all without requiring the tedious manual effort and complexity of previous FPGA-optimized simulation techniques. By substituting target-design memories with logic-intensive read and write ports for resource-efficient, cycle-accurate models that serially access FPGA memory primitives, GOLDEN GATE simulators can avoid the disproportionate impact of FPGA-hostile memory design patterns on simulators of high-performance processor cores. Drawing inspiration from software simulators and specialized emulators, where common code may be repeatedly executed to model an arbitrary number of copies of a given block, I also introduce an automatic instance-threading optimization, through which the logic resources required to simulate a given module may be shared across multiple instances, radically reducing their collective footprint.

To support the use of these optimizations across a broad array of user designs, they are integrated as contributions to Golden Gate, an extensible compiler that translates RTL designs into cycle-accurate FPGA simulators as part of the open-source FireSim FPGA simulation framework. By structuring simulators as modular dataflow networks, GOLDEN GATE provides the flexibility to compose the two optimizations along with the ability to combine them with software co-simulation or other advanced simulation features. To evaluate the performance of the optimizations and to validate the optimizing compiler stack, these techniques are applied to two input designs: a general-purpose SoC with multiple out-oforder cores and a domain-specific accelerator with multiple systolic array co-processors. In each case, finite programmable logic resources limit the maximum number of cores-and therefore the size of the system-that can effectively be simulated on a simulation platform consisting of cloud-hosted Xilinx VU9P FPGAs. However, by enabling optimizations in GOLDEN GATE through simple compiler directives, the same FPGA platform was able to support configurations of each system with an eight-fold increase in core count relative to the baseline, providing the ability to simulate sixteen out-of-order cores or eight accelerator cores at high speed, with deterministic, cycle-accurate results. Ultimately, this significant increase in per-FPGA capability broadens the utility of commodity FPGAs in simulating ever-growing chips, while the convenience of automatic compiler optimization helps support designer productivity in a rapidly accelerating hardware ecosystem.

# Contents

| $\mathbf{C}_{\mathbf{C}}$ | onter               | nts                                                           | i      |

|---------------------------|---------------------|---------------------------------------------------------------|--------|

| Li                        | st of               | Figures                                                       | iv     |

| Li                        | st of               | Tables                                                        | vi     |

| G                         | lossa               | ry of Terms                                                   | vii    |

| $\mathbf{A}$              | ckno                | wledgements                                                   | viii   |

| 1                         | <b>Int</b> r<br>1.1 | Previous Publication, Collaboration, and Funding              | 1<br>3 |

| <b>2</b>                  | Bac                 | kground                                                       | 5      |

|                           | 2.1                 | Prior Work in FPGA Emulation                                  | 5      |

|                           |                     | 2.1.1 FPGA Prototyping                                        | 5      |

|                           |                     | 2.1.2 Commercial Emulation Systems                            | 6      |

|                           |                     | 2.1.3 Decoupled FPGA-Accelerated Simulators                   | 7      |

|                           |                     | 2.1.4 The FAME Simulator Taxonomy                             | 8      |

|                           |                     | 2.1.5 FireSim and GOLDEN GATE                                 | 11     |

|                           | 2.2                 | Chisel: A Modern Language for Hardware                        | 12     |

|                           | 2.3                 | The FIRRTL Hardware Compiler Framework                        | 14     |

|                           |                     | 2.3.1 FIRRTL Intermediate Representation                      | 14     |

|                           |                     | 2.3.2 The Reference FIRRTL Compiler                           | 15     |

|                           | 2.4                 | The Rocket Chip Generator                                     | 15     |

|                           |                     | 2.4.1 Rocket                                                  | 15     |

|                           |                     | 2.4.2 BOOM                                                    | 16     |

| 3                         |                     | aflow Simulation with Golden Gate                             | 18     |

|                           | 3.1                 | All Simulators are Hybrid Simulators                          | 18     |

|                           |                     | 3.1.1 Refining the Notion of Decoupling                       |        |

|                           |                     | 3.1.2 Incorporating RTL-Specified Models in Hybrid Simulators | 20     |

|                           |                     | 3.1.3 Hybrid Simulators and Optimization                      | 21     |

|   | 3.2        |                                                                           | 21 |

|---|------------|---------------------------------------------------------------------------|----|

|   | 3.3        | V                                                                         | 22 |

|   |            |                                                                           | 26 |

|   | 2 4        | 1                                                                         | 27 |

|   | 3.4        | Compiling Target RTL to LI-BDN Simulators                                 | 28 |

| 4 | The        | Golden Gate Toolchain 2                                                   | 29 |

|   | 4.1        | FireSim and Golden Gate                                                   | 29 |

|   | 4.2        | A FIRRTL-Based Simulator Compiler                                         | 30 |

|   |            | 4.2.1 Fine-Grained Incremental Lowering with Core FIRRTL Passes 3         | 32 |

|   |            | 4.2.2 Harnessing the Extensible FIRRTL Annotation Interface               | 33 |

|   |            | 4.2.3 Built-in FIRRTL Analyses and Consistency Checks                     | 35 |

|   |            | 4.2.4 Differing Requirements of RTL Compilers and Simulator Compilers . 3 | 36 |

|   | 4.3        | Compiler Organization                                                     | 37 |

|   |            | 4.3.1 Target Transformation                                               | 38 |

|   |            | 4.3.2 Decomposed Target Form                                              | 38 |

|   |            | 4.3.3 Simulator Synthesis                                                 | 10 |

|   | 4.4        |                                                                           | 10 |

|   | 4.5        | Adding New Optimizations                                                  | 11 |

|   | 4.6        | Summary                                                                   | 13 |

| 5 | Opt        | imizing Multi-Ported Memories 4                                           | 4  |

|   | $5.1^{-2}$ | <u> </u>                                                                  | 15 |

|   |            |                                                                           | 16 |

|   | 5.2        |                                                                           | 16 |

|   | 5.3        |                                                                           | 16 |

|   | 5.4        | Evaluation                                                                | 17 |

|   |            | 5.4.1 Applying the Optimization to Rocket Chip                            | 18 |

|   |            |                                                                           | 18 |

|   |            | 5.4.3 Improving Performance with Host RAM Banking                         | 52 |

|   |            | 5.4.4 Summary                                                             | 54 |

| 6 | Opt        | imizing Repeated Instances via Threading 5                                | 55 |

|   | 6.1        | 0 <b>1</b>                                                                | 56 |

|   | 6.2        |                                                                           | 56 |

|   | 6.3        |                                                                           | 57 |

|   |            | 9                                                                         | 57 |

|   |            |                                                                           | 60 |

|   |            |                                                                           | 60 |

|   |            | -                                                                         | 31 |

|   |            | · · ·                                                                     | 32 |

|   | 6.4        | ~                                                                         | 70 |

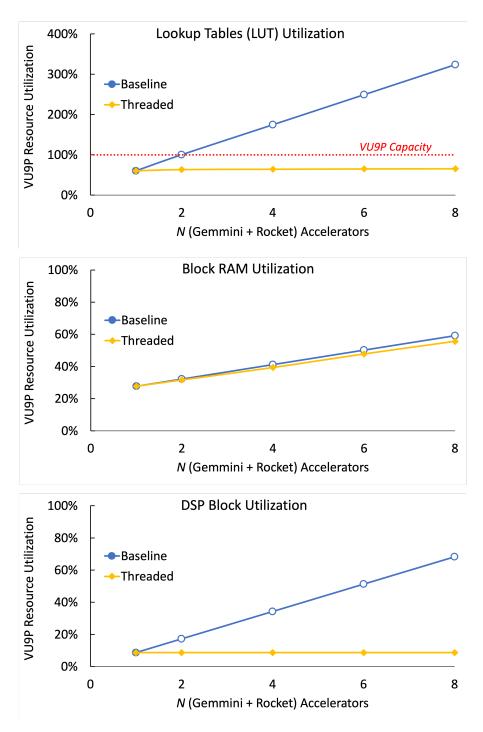

|     | 6.5  | Evaluation76.5.1 Applying the Optimization to Rocket Chip76.5.2 Experimental Results with Multi-Core BOOM Systems76.5.3 Broader Applicability to Accelerator-Based Systems7 | '1<br>'2 |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 7   | Con  | nposing Multiple Resource Optimizations 8                                                                                                                                   | 0        |

|     | 7.1  | Combining Complementary Optimizations                                                                                                                                       | 1        |

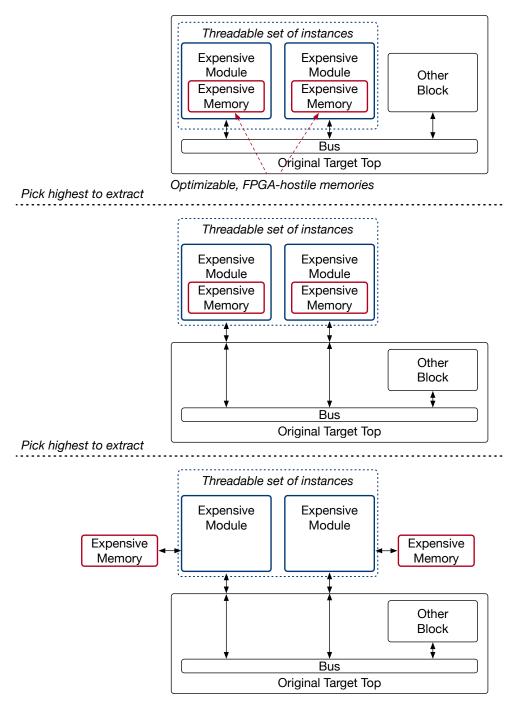

|     |      | 7.1.1 Transforming Target Design Topologies                                                                                                                                 | 3        |

|     |      | 7.1.2 Hiding Optimization Latency with Threading 8                                                                                                                          | 3        |

|     | 7.2  | Evaluation                                                                                                                                                                  | 5        |

|     |      | 7.2.1 Applying Multiple Optimizations to Rocket Chip 8                                                                                                                      |          |

|     |      | 7.2.2 Experimental Results                                                                                                                                                  | 7        |

| 8   | Δ C  | Chisel Temporal Property Verification Toolkit 9                                                                                                                             | 2        |

| G   | 8.1  | Background                                                                                                                                                                  |          |

|     | 0.1  | 8.1.1 Related Work in Chisel Verification                                                                                                                                   |          |

|     |      | 8.1.2 Linear Temporal Logic Properties                                                                                                                                      |          |

|     | 8.2  | UCLID5                                                                                                                                                                      |          |

|     | 8.3  | A Chisel-Based LTL Property Verification Flow                                                                                                                               |          |

|     | 0.0  | 8.3.1 LTL Property Annotations                                                                                                                                              |          |

|     |      | 8.3.2 Control Annotations                                                                                                                                                   | 7        |

|     |      | 8.3.3 Chisel LTL Property API                                                                                                                                               | 7        |

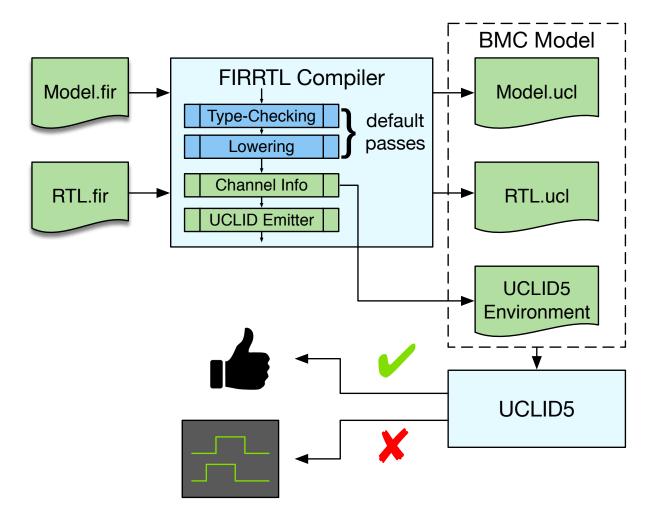

|     |      | 8.3.4 Verification Library Transforms                                                                                                                                       | 8        |

|     |      | 8.3.5 A UCLID5 Backend for FIRRTL                                                                                                                                           | 0        |

|     | 8.4  | Case Study: Verifying a Queue                                                                                                                                               | 1        |

|     | 8.5  | Leveraging Generators & Object Orientation                                                                                                                                  | 3        |

| 9   | LIM  | IE: Verifying Multi-Cycle Models                                                                                                                                            | )5       |

|     | 9.1  | Structure of the LIME Checker                                                                                                                                               |          |

|     |      | 9.1.1 A UCLID5 Backend for FIRRTL                                                                                                                                           | 6        |

|     |      | 9.1.2 Modeling Environment Generation                                                                                                                                       | 6        |

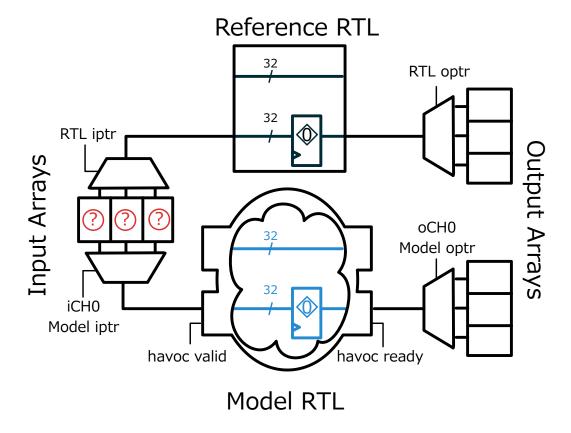

|     | 9.2  | Model Checking LI-BDNs                                                                                                                                                      | 7        |

|     |      | 9.2.1 Partial Implementation                                                                                                                                                | 8        |

|     |      | 9.2.2 No Extraneous Dependencies                                                                                                                                            | 9        |

|     |      | 9.2.3 Self-Cleaning                                                                                                                                                         | 0        |

|     | 9.3  | Verifying Multi-Ported Memory Models with LIME                                                                                                                              | 1        |

| 10  | Con  | iclusion 11                                                                                                                                                                 | 9        |

| 10  |      | Current Status and Future Work                                                                                                                                              |          |

| ъ., |      |                                                                                                                                                                             |          |

| ВI  | onog | graphy 11                                                                                                                                                                   | .0       |

# List of Figures

| 2.1<br>2.2                             | A 32-bit adder model and environment simulating a single cycle of target time BOOM pipeline diagram: evolution across three versions                                                                                                                                                | 7<br>17                                                              |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

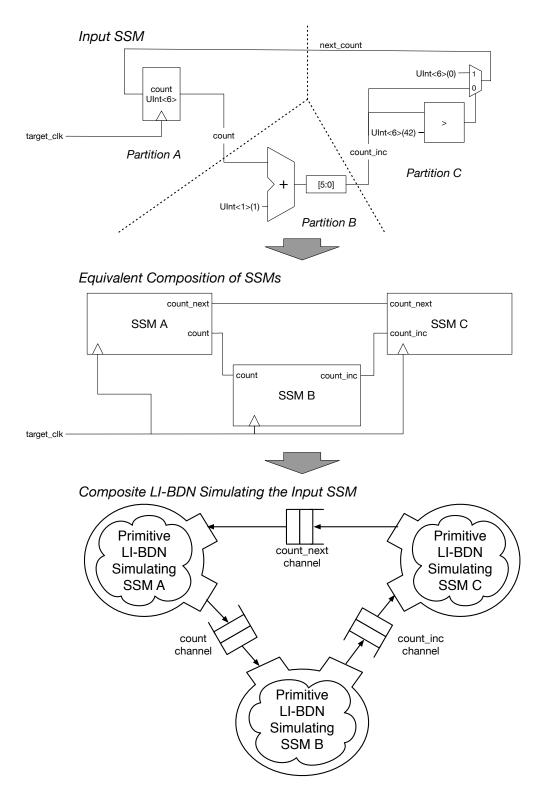

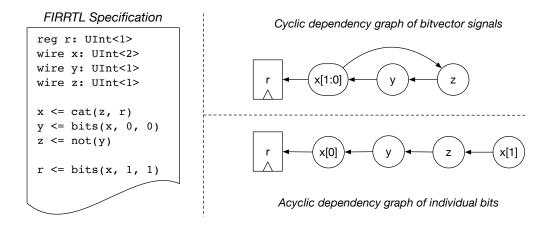

| 3.1<br>3.2                             | Composing primitive LI-BDNs to simulate a single synchronous state machine . Combinational loops vs. bitvector dependency loops                                                                                                                                                     | $\frac{24}{27}$                                                      |

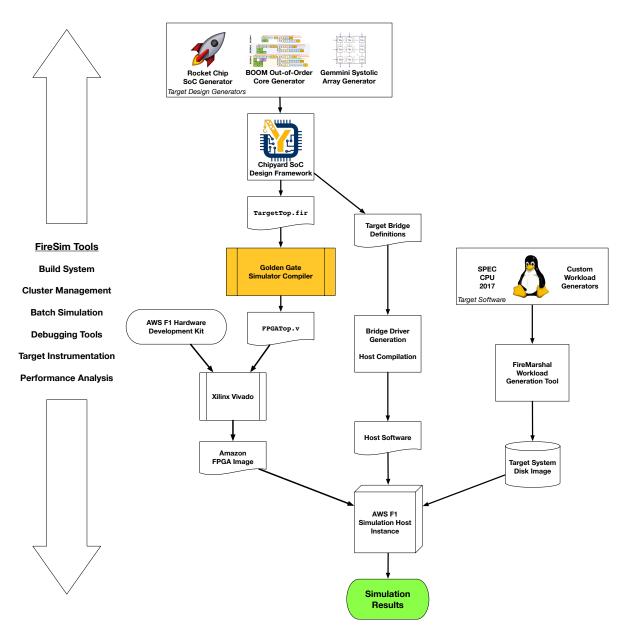

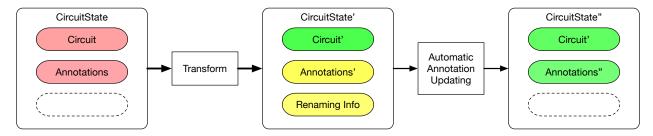

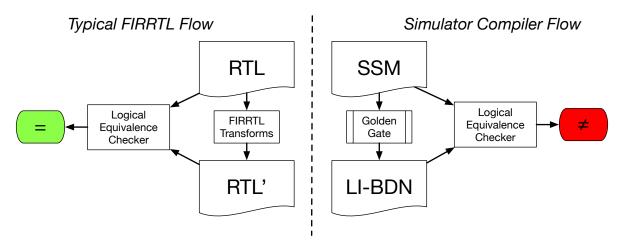

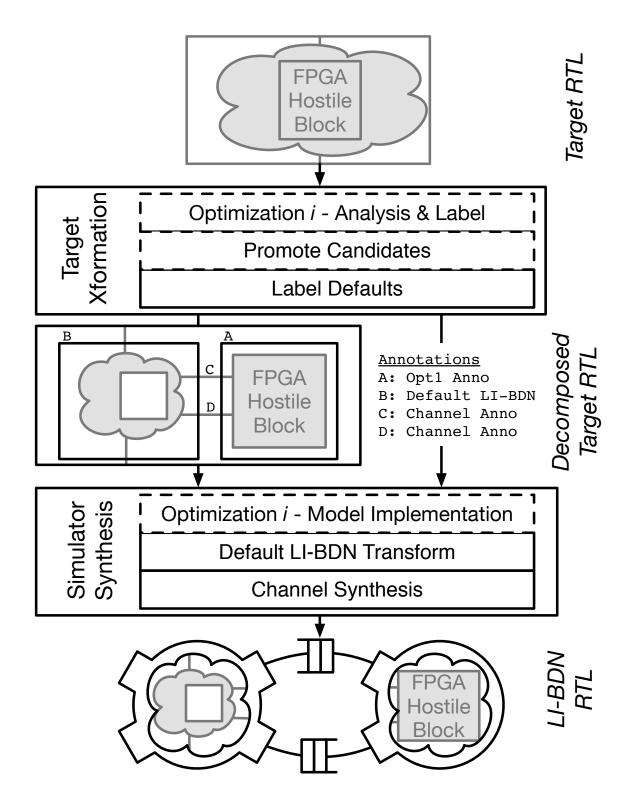

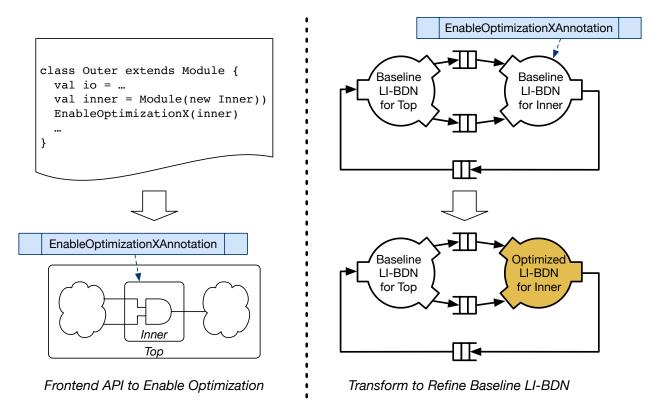

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | GOLDEN GATE within the broader FireSim stack  Structure of a FIRRTL transform  Comparison of a typical FIRRTL flow with a simulator compiler  The GOLDEN GATE compiler flow  Elements of a modular optimization  Separating simulation-specific annotations from RTL specifications | 31<br>33<br>36<br>39<br>41<br>42                                     |

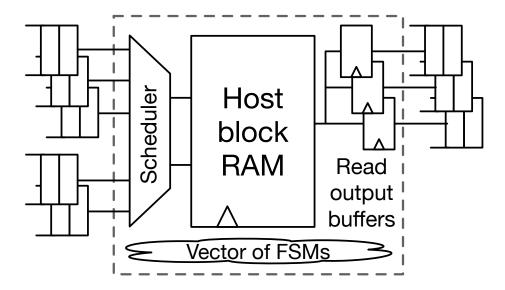

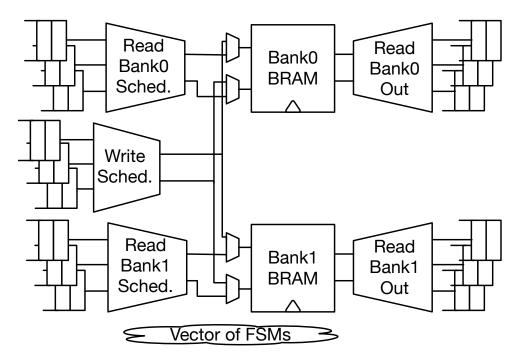

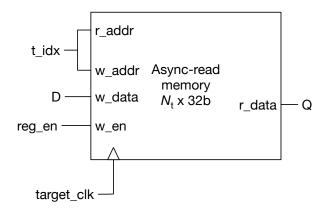

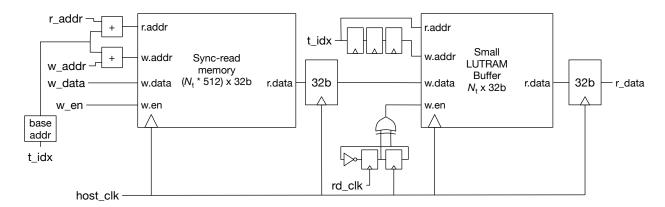

| 5.1<br>5.2<br>5.3<br>5.4               | Microarchitecture of an optimized memory model                                                                                                                                                                                                                                      | 47<br>49<br>51<br>53                                                 |

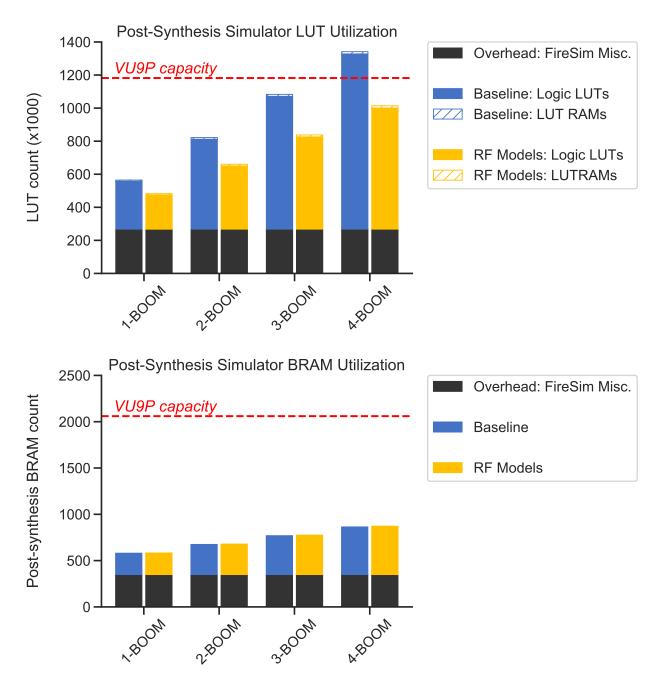

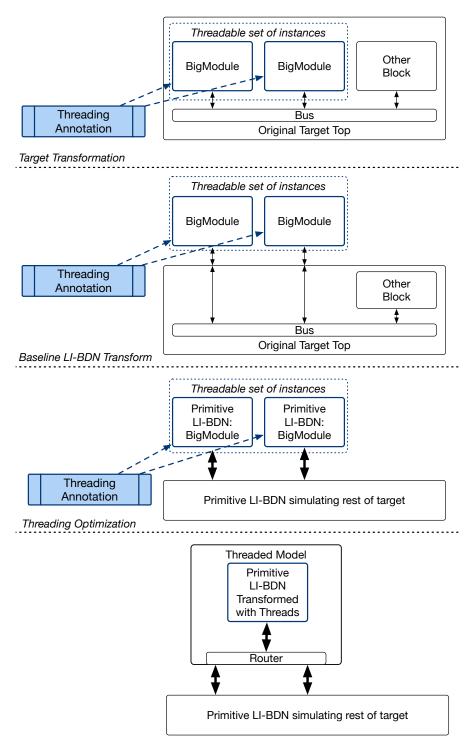

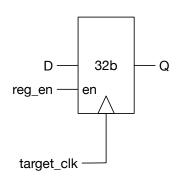

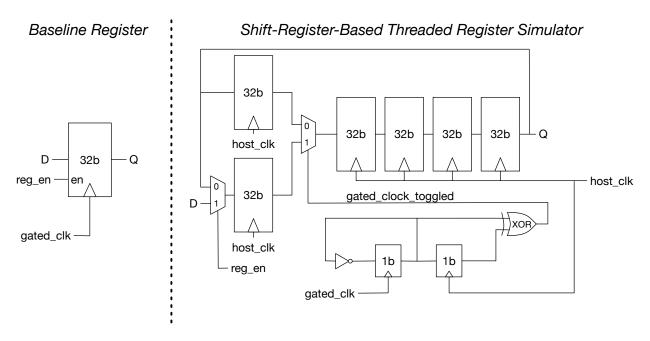

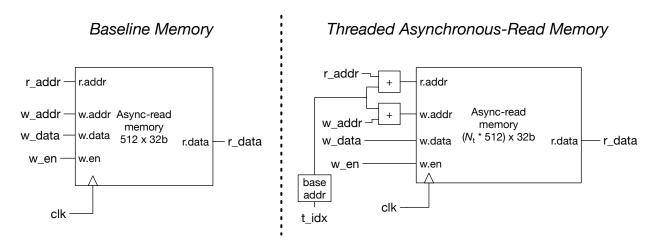

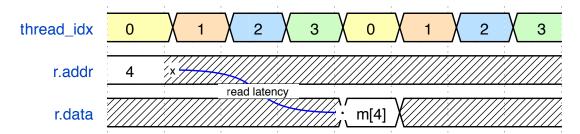

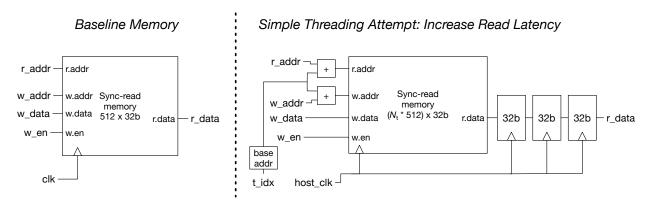

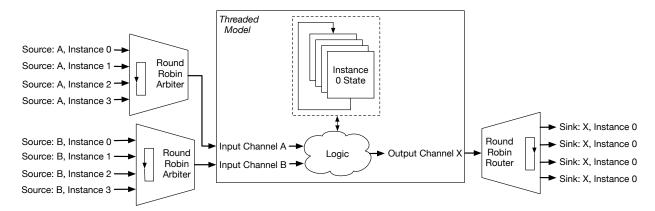

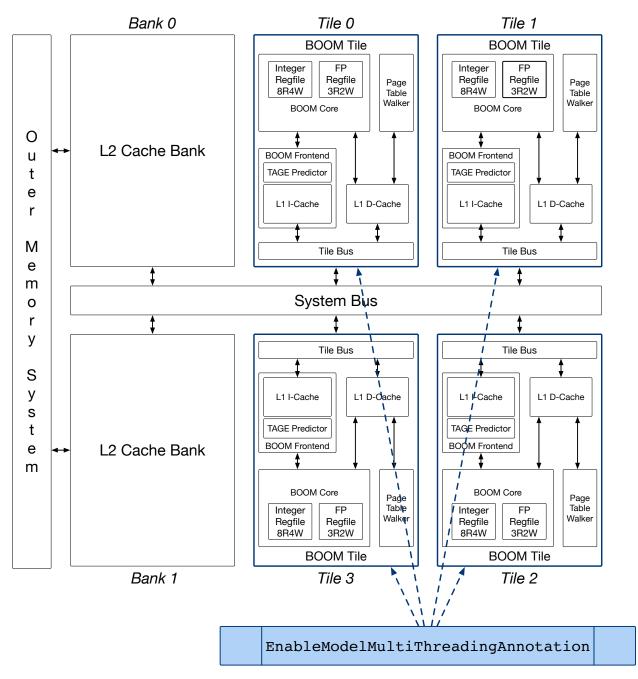

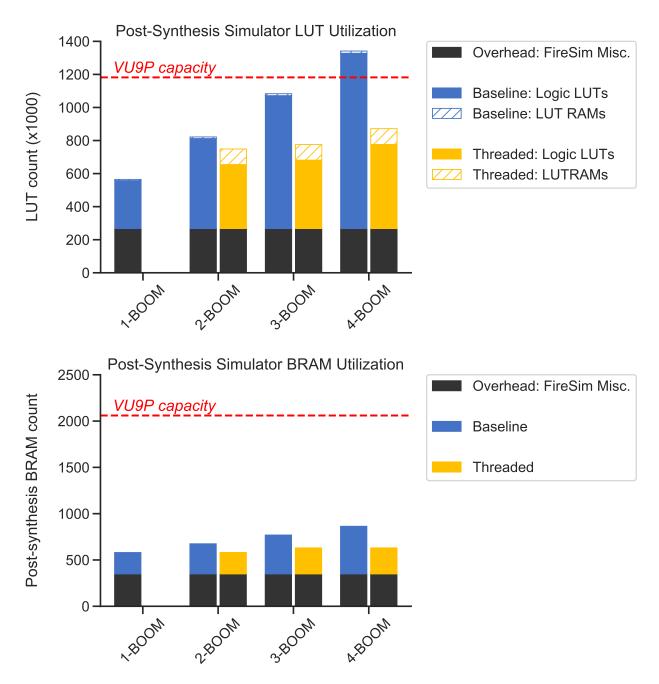

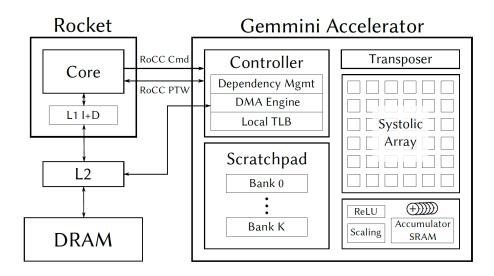

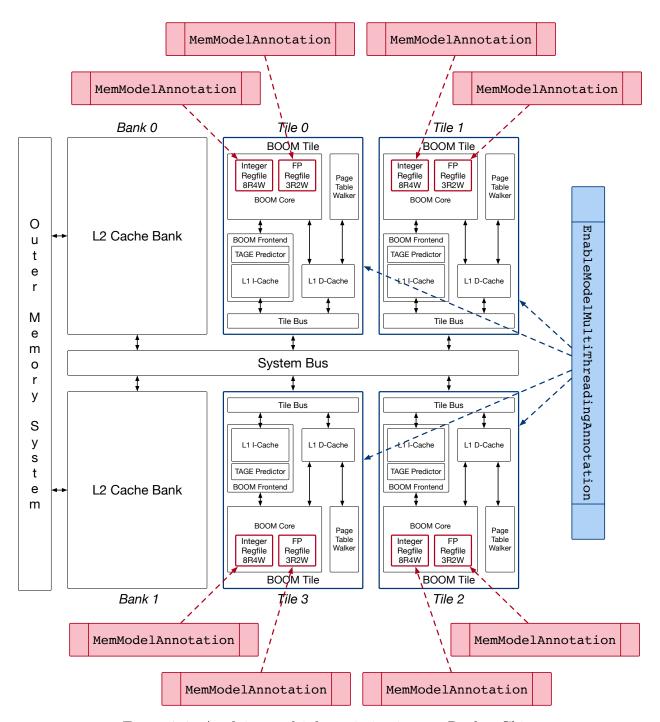

|                                        | Elements of a modular optimization                                                                                                                                                                                                                                                  | 58<br>61<br>64<br>65<br>67<br>68<br>68<br>69<br>70<br>73<br>74<br>77 |

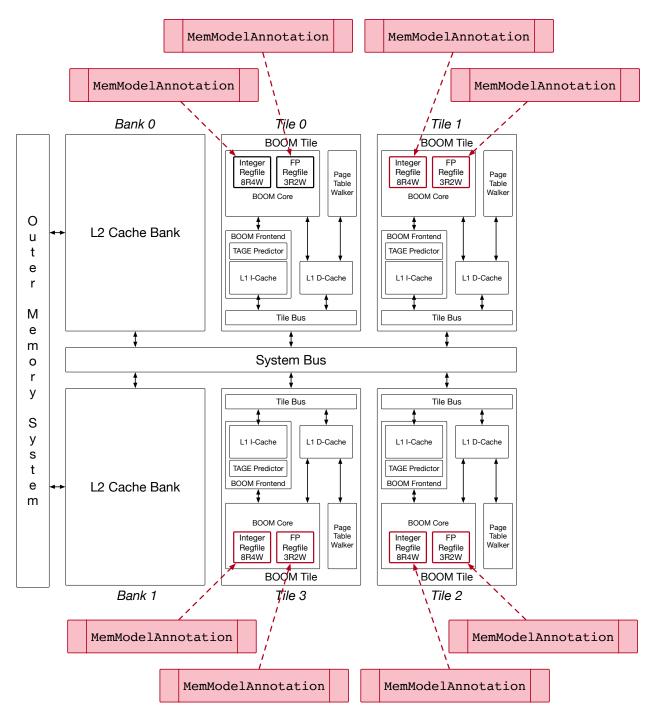

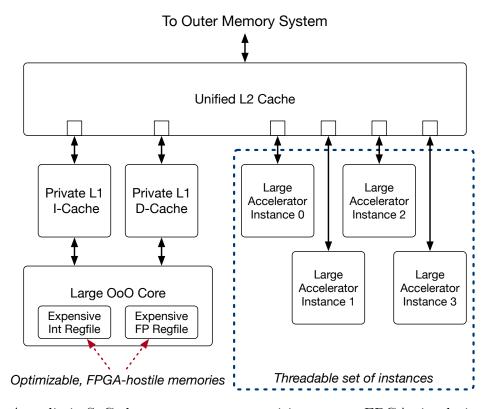

| 7.1<br>7.2                             | An SoC with distinct targets for memory and threading optimizations Transforming a target hierarchy with nested optimization targets                                                                                                                                                | 82<br>84                                                             |

| 7.3 | Applying multiple optimizations to Rocket Chip                        | 86  |

|-----|-----------------------------------------------------------------------|-----|

| 7.4 | Simulator LUT utilization vs. core count vs. optimization strategy    | 88  |

| 8.1 | An example liveness property expressed in the Chisel LTL language     | 98  |

| 8.2 | A Chisel single-entry FIFO queue with an associated LTL specification | 102 |

| 8.3 | An object-oriented verification generator                             | 104 |

| 9.1 | LIME Flow                                                             | 107 |

| 9.2 | Partial Implementation Model                                          | 108 |

# List of Tables

| 5.1 | Key specifications for Rocket and LargeBOOM cores                      | 48  |

|-----|------------------------------------------------------------------------|-----|

| 5.2 | Register file parameters for Rocket and LargeBOOM cores                | 50  |

| 5.3 | Performance comparison of baseline and threaded simulators             | 52  |

| 5.4 | Performance impact of banking multi-cycle memory models                | 53  |

| 6.1 | Comparison of register-threading strategies                            | 66  |

| 6.2 | Performance comparison of baseline and threaded simulators             | 76  |

| 6.3 | Configuration parameters for Gemmini targets                           | 78  |

| 7.1 | Qualititative microarchitectural tradeoffs of two optimizations        | 83  |

| 7.2 | Observed FMR for simulators with varying core counts and optimizations | 89  |

| 7.3 | Comparison of simulator capabilities vs. optimization strategy         | 91  |

| 8.1 | Production rules for legal LTL properties                              | 95  |

| 9.1 | Runtime for a LIME Partial-Implementation bounded model check          | 111 |

# Glossary of Terms

#### Abbreviations

ASIC Application-Specific Integrated Circuit FAME FPGA Architecture Model Execution FPGA Field-Programmable Gate Array

LI-BDN Latency-Insensitive Bounded Dataflow Network

LTL Linear Temporal Logic

MIDAS Modeling Infrastructure for Debugging and Simulation

**RTL** Register Transfer Level

#### **Definitions**

Chisel An open-source hardware description language embedded in Scala

FAME-1 A simulator that may execute one target cycle across multiple host cycles

FAME-5 A simulator where a host resource may represent n copies in the target

FIRRTL Flexible Intermediate Representation for RTL: the output of Chisel

Host The system of hardware & software resources used to implement a simulator

LIME Latency-Insensitive Model Equivalence: a checker for FAME-1 simulators

RISC-V An open standard instruction set architecture

Target The system & environment that are simulated by an architectural simulator RAMP Research Accelerator for Multiple Processors: a many-core FPGA simulator

### Acknowledgments

Though there are many uncertainties in the PhD process, I have been certain throughout my time at Berkeley that I am very lucky to have an amazing group of colleagues. Their mentorship led me to pursue graduate school, and their support enabled me to finish.

- I am deeply grateful to my co-advisor Jonathan Bachrach for always believing in me. From offering a student in class a job to seven years of collaboration, you've been a welcome source of optimism and forward-looking vision.

- Without a common vision, the fantastic collaboration in the Berkeley Architecture Research group would not be possible. My co-advisor Krste Asanović has helped foster a true team dynamic, which has been the foundation of lasting relationships with other graduate students. Krste has always been a reliable source of great ideas and a dedicated teacher.

- I would like to particularly thank Sanjit Seshia for helping to shepherd our EE219C project and for his detailed feedback on the ICCAD publication on GOLDEN GATE.

- Unfortunately, I am saddened to hear of the untimely passing of Pramod Subramanyan. His patient and enthusiastic help as an instructor for EE219C was the greatest enabler in learning more about model checking and UCLID5.

- As my first mentor in the ASPIRE Lab, Palmer Dabbelt taught me more than I thought I wanted to know about computers. He is a one-of-a-kind friend who is always willing to share.

- My long-term collaborator Adam Izraelevitz has always been a source of inspiration. From letting me sleep on his couch, to working together on class projects, to seven years of Chisel meetings, he's always made everything a bit more fun. Most of all, I appreciate his ability to bring positivity any situation.

- Through many projects (and even more project acronyms), I have always enjoyed collaborating with Jack Koenig. The quality of his insights are matched only by his ability to never take himself too seriously.

- I know I am not alone in thanking Andrew Waterman for his consistent willingness to spend time discussing ideas, even long after his own graduation from Berkeley. His dedication to teamwork and to continual improvement of mature projects like Chisel continue to have lasting impact at Berkeley and beyond.

- For many years, Eric Love has been both a reliable friend and a tireless driver of a close, friendly research group environment. Outside of work, he has been a part of many of the great memories of my time at Berkeley. In these isolating times, I will always look back fondly on our many Zoom calls, especially those with our friends Nathan Pemberton and Jordan Kellerstrass.

• Last, but certainly not least, without the help of David Biancolin, I would never have made it through the latter half of my PhD. His collaboration in so many aspects of my research helped make this entire dissertation possible. More importantly, he has been a tireless source of advising and has always helped me keep a clearer vision of where my work is headed. Outside of work, his humor and shared interests have made grad school much more enjoyable.

Outside of work, I would like to thank my family for a lifetime of support. My parents, along with my sister Lydia and brother Derek, have always made me feel as though I have the capability to take on anything. I know that grad school can be a test of patience for any parents, but I never felt pressure to pursue a more immediate or practical path. Finally, most of all, I would like to thank my fiancée Orianna for always listening when I needed it most, for being the best Powerpoint editor I know, and for helping show me by example that finishing grad school is in fact possible.

# Chapter 1

# Introduction

As the semiconductor industry ventures further into the twilight of transistor scaling, there is broad consensus that improvements in computing performance and energy efficiency must come from innovations above the transistor in the computing stack. This comes at a time when there are myriad emerging applications, in domains like AI, virtual and augmented reality, and the Internet of Things, that depend on the availability of higher-performance, more energy-efficient computing systems. As a result, system architects have turned to specialization: in modern SoCs, application cores increasingly yield their area to specialized accelerators [36]. However, this specialization begets complexity that makes these systems more difficult to build, verify, and program. This drives up the non-recurring engineering (NRE) costs of developing new chips, making custom silicon inaccessible to all but high-volume markets.

The lack of an affordable full-system simulation technology that is both fast and accurate is one key driver of these NRE costs. A simulator that is too slow cannot exercise bugs that manifest deep into execution and is thus unusable for software development. However, a faster, less detailed simulator may differ too greatly from the actual silicon to exhibit the same bugs and performance pathologies, precluding effective pre-silicon verification and validation.

Among the leading solutions for digital logic simulation, Field-Programmable Gate Arrays (FPGAs) have long been used for prototyping and emulation of ASICs in both industry [55] and academia [91, 49]. While FPGAs have great potential as a commercial-off-the-shelf technology that offers radical speedups over software simulation, no current FPGA-based system offers the ideal combination of simulation speed, capacity, affordability, and ease of use. Direct FPGA prototypes are affordable and fast, but require the user to manually model the external environment of the device and to invest significant effort to meet resource constraints. Commercial emulation platforms offer automated scaling to larger designs, but suffer from high cost of entry and take a large performance hit when partitioning designs across many FPGAs. While manually resource-optimized simulators such as RAMP Gold [83] present large increases in per-FPGA capacity, this approach lacks the flexibility to model arbitrary target designs. When contrasted with the simplicity of software simulation,

it is clear that FPGAs provide the potential for large speedups at the expense of flexibility. In this work, we hypothesize that FPGA simulation can be improved by employing abstractions inspired by software simulators and specialized emulation processors.

In general, the problem of mapping a design to an FPGA-based emulation platform centers around translating register-transfer level (RTL) designs to direct FPGA implementations, which imposes a fundamental capacity constraint: every component in the target design must have a corresponding component in the FPGA implementation. This is very much in contrast to either a software simulator or an advanced emulation platform[12], which use the notion of serial execution to extend the capacity of a finite set of hardware resources such as an application processor or specialized emulation chip. Traditionally, FPGA capacity limitations have been addressed via manual optimization of the target design (the design under simulation) to better suit the host FPGA platform, or by partitioning the design across multiple FPGAs. While these techniques are valuable and often necessary, they are grounded in the limitations that arise from the direct translation of a target RTL design into an FPGA implementation. Though this direct translation is convenient, it is unnecessarily restrictive.

This dissertation presents an alternative approach: automatic construction of resource-optimized FPGA simulators by introducing a *simulator compiler* to the simulation workflow. In contrast with traditional FPGA tools, such a compiler is explicitly aware of the notion that it is creating a simulator, rather than an implementation. This distinction provides the freedom for the compiler to transform components of the RTL design into simulation models that do not rely on an equivalent implementation at the RTL level; rather, these models are hardware implementations of a specification that implies cycle-accurate simulation of the target design.

As a concrete implementation of this concept, this dissertation introduces automatic resource optimizations in Golden Gate, a simulator compiler framework that accepts target RTL designs and produces RTL implementations of cycle-accurate simulators. By introducing this extra level of abstraction, GOLDEN GATE decouples the cycle-by-cycle execution of the FPGA simulator from the cycle-by-cycle forward progress of simulated target execution time. While other simulation frameworks have used the notion of independent FPGA and simulation time to reconcile issues arising from the I/O boundary or to support co-simulation of software-hosted models, Golden Gate is designed from the start to support optimizations such as time-multiplexing of FPGA resources to enable flexible tradeoffs of simulation throughput and resource efficiency. In contrast to previous work in static time-multiplexing of FPGA resources, GOLDEN GATE employs the Latency-Insensitive Bounded Dataflow Network (LI-BDN) formalism to decompose the simulator into sub-components, each of which may be independently and automatically optimized. This structure allows Golden Gate to support a broad class of optimizations that improve resource utilization by implementing FPGA-hostile structures over multiple cycles, while the LI-BDN formalism ensures that the simulator still produces bit- and cycle-exact results.

This work focuses on two composable optimizations that provide significant increases in per-FPGA capacity, allowing much larger systems to be simulated on a single FPGA.

The first optimization replaces highly ported memories in the target design with multi-cycle simulation models that rely on serialized accesses to efficient underlying FPGA memory resources. While this optimization is applicable only to very specific blocks in the target design, it provides a significant benefit when applied to RTL implementations of multi-ported register files in out-of-order processors. In addition, a second optimization focuses on reducing the effective footprint of a broad swath of the design: the large footprint of the combinational logic contained in repeated instances of large blocks, which are a signature feature of modern multi-core systems. When viewing an FPGA simulator as a hardware implementation of a simulation specification, rather than as a direct implementation of the target design, it is clear that there is considerable redundancy; therefore, the *multi-threading* optimization allows GOLDEN GATE to serialize the simulation of multiple instances. This optimization provides a radical increase in capacity at the expense of extending the latency required to simulate a single cycle of the set of instances.

Finally, while these optimizations provide significant benefit in isolation, the advantage of the structured approach of Golden Gate to generating simulators allows the two optimizations to compose. While the multi-threading optimization radically reduces the resource utilization of the combinational logic in multiple instances, it does nothing to reduce the footprint of FPGA-hostile memories. However, when composed with the memory optimization, the resulting simulator provides relative capacity increases exceeding the product of the two optimizations' individual benefits. Furthermore, as in other domains, the use of multiple threads of execution is effective at hiding latency increases elsewhere in the system; in practice, this allows the composed simulator to deliver performance similar to the theoretical maximum of a simulator employing the instance multi-threading optimization alone.

In addition to the two optimizations, this work involves substantial contributions to the hardware compiler infrastructure that underpins Golden Gate. In addition to several components of the Golden Gate software implementation, the development of these optimizations included various efforts to validate the behavior of the simulator implementations. One component of this validation process is LIME, the Latency-Insensitive Model Equivalence checker. This dissertation presents LIME and other infrastructural improvements as examples of how improved software support can improve productivity in developing computer-aided design (CAD) tools for simulation and other applications in digital system design.

# 1.1 Previous Publication, Collaboration, and Funding

Portions of this work were published at the 2019 International Conference on Computer-Aided Design as "Golden Gate: Bridging The Resource-Efficiency Gap Between ASICs and FPGA Prototypes." This project is designed to integrate with the FireSim[49] project; specifically, it replaces MIDAS, the hardware compiler that allows FireSim to transform target designs to add the ability to "pause" the advance of simulated time. While MIDAS relied on a fairly simple transformation, GOLDEN GATE introduces an optimizing compiler

to allow the simulator to trade off time for reduced utilization of scarce host FPGA resources.

The baseline, non-optimizing compiler framework for Golden Gate was developed in collaboration with David Biancolin. While this dissertation focuses on the research contribution of enhancing FPGA capacity with automatic resource optimization, most of the engineering effort is associated with co-developing this original software framework. Furthermore, the pattern described in Section 4.5 was also developed through the collaborative integration of the multi-ported memory models with the rest of the Golden Gate compiler. Finally, the LIME verification tool was originally developed as a class project for EE219C with David Biancolin and Jack Koenig.

The information, data, or work presented herein was funded in part by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number DE-AR0000849. Research was partially funded by ADEPT Lab industrial sponsors and affiliates Intel, Apple, Futurewei, Google, and Seagate, and supported by gifts provided by Amazon Web Services and Xilinx.

The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# Chapter 2

# Background

The work presented in this dissertation draws on a long background of prior work in FPGA simulation. Many academic and industrial projects have made notable advances in resource-efficient use of commodity FPGAs, some of which have laid the groundwork for the optimizations presented in Chapters 5 and 6. Furthermore, we rely on a broad assortment of open-source projects to provide infrastructure for generating parameterized target designs, developing hardware compiler transforms, and targeting cloud-hosted FPGA host platforms.

## 2.1 Prior Work in FPGA Emulation

Pre-silicon evaluation of ASICs has long been a core application for FPGAs [25]. While this takes many forms, including prototyping, emulation, and hardware-accelerated simulation, each involves mapping a *target* system (the device being simulated) onto a *host* system that includes one or more FPGAs.

## 2.1.1 FPGA Prototyping

Direct FPGA prototypes, where designs are directly mapped onto FPGA fabric, are a common way to enable pre-silicon software development and functional validation [1]. At a high level, an FPGA prototype implementation is produced by providing the RTL design of a chip as an input to a standard FPGA development suite, such as Xilinx Vivado or Intel Quartus Prime. By appropriately mapping the I/O pins of the FPGA and designing a suitable board, such an implementation can be used as a near-direct replacement for the chip under in-circuit emulation.

Ideally, this would be a push-button flow, but in reality, multiple hurdles often necessitate the labor-intensive development of an "FPGA version" of the design:

1. Device capacity: nontrivial ASICs must be partitioned across multiple FPGAs at the expense of slower execution rates, longer compile times, and more expensive host platforms [37].

- 2. Resource conversions: ASIC power, reset, and clocking structures do not map directly to the host FPGA and must be replaced [1, 38].

- 3. I/O modeling: I/O devices and environment models may not map well to the fabric, necessitating adapters for in-situ prototyping. One recurring example of this issue is the need to slow down external I/O to match the reduced speed of an FPGA prototype.

With a traditional FPGA prototype, the burden of overcoming these hurdles is left to the user.

### 2.1.2 Commercial Emulation Systems

Commercial FPGA-based emulation systems generally consist of a custom hardware platform, along with a set of software tools to streamline the partitioning and I/O modeling problems [55]. These tools build on advances in inter-chip routing [51, 38] and time-multiplexing of pins [4] to reduce the speed and productivity overhead of using multi-FPGA host platforms. Furthermore, they may offer transactional emulation mechanisms for interfacing with I/O models that are co-simulated in a software environment [43, 56], which can resolve the issue of I/O speed matching by gating the clock in the target design to wait for software. However, these features come at a price: large monetary cost of entry and slowdowns due to partitioning.

In addition to FPGA-based systems, multiple commercial emulation platforms rely on custom emulation chips as an underlying implementation substrate, including the IBM Yorktown Simulation Engine [73], Cadence Palladium [12] and Mentor Graphics Veloce [86]. While these systems employ similar multi-chip partitioning strategies to large FPGA emulators, each chip relies on application-specific emulation accelerators that execute an instruction stream, rather than an intrinsically parallel FPGA implementation. This key distinction brings many of the advantages associated with programmability, including the flexibility to accept larger programs (and therefore simulate more logic), along with the ability to implement arbitrarily complex behaviors, including gate-level simulation and non-RTL constructs of modeling-oriented HDLs. Furthermore, since these products' toolchains effectively generate software images for emulation processors, they have much faster compile times than those of large multi-FPGA emulators, which may be measured in multiple days. However, as evidenced by the continuing popularity of FPGA-based solutions, these systems are not without significant drawbacks: they come at an even higher cost that is prohibitive for all but the largest chip-building operations, and the flexibility of programmability comes at the cost of lower emulation throughput. Though academic efforts such as Malibu [35] and Cyclist [5] have attempted to provide low-cost alternatives, specialized emulation hardware remains the domain of large CAD tool vendors.

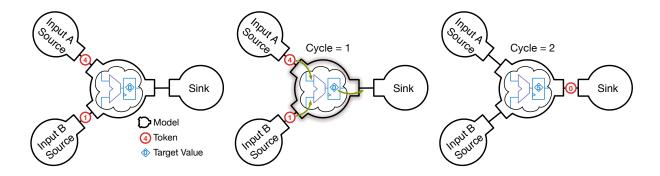

Figure 2.1: A 32-bit adder model and environment simulating a single cycle of target time.

### 2.1.3 Decoupled FPGA-Accelerated Simulators

While computer architecture research has long relied on software simulators in lieu of complete RTL implementations, the Research Accelerator for Multiple Processors (RAMP) [91] project aimed to use FPGAs to increase the speed and fidelity of microarchitectural simulations of many-core systems. This cross-university initiative led to the development of numerous FPGA simulators; in contrast with commercial logic emulation systems that model the behavior of concrete RTL designs, these simulators were generally designed from the ground up to optimally model a particular target system or class of systems. By exploiting introspection of the behavior of the target design in the design of the host implementation, these simulators were able to overcome some of the intrinsic the resource constraints faced by FPGA prototypes. In particular, some RAMP simulators such as HAsim [71] and RAMP Gold [83] used optimized RTL timing models to model FPGA-hostile structures like multiported RAMs over multiple FPGA cycles. This host-target decoupling, the ability to simulate one target clock cycle over a variable number of FPGA-host clock cycles, is the hallmark of these decoupled simulators.

To support host-target decoupling, the target machine can be simulated as a synchronous dataflow graph [63] of *models*; we give an example in Figure 2.1. To simulate one target cycle, a model dequeues one *token* from each of its input ports and enqueues a token into each of its output ports. The simplest RTL implementation of a model waits for all of its input tokens to be available and all output ports to be ready before executing; this is a direct application of Carloni et al. [14]. Simulation models that properly implement this formalism tolerate latency on the arrival of tokens and may take variable number of host cycles to compute their outputs. This makes it possible to apply these optimizations without changing the target's RTL behavior.

An important measure of decoupled simulator performance is the FPGA-Cycle-To-Model-Cycle Ratio (FMR) [72]: the average number of FPGA cycles elapsed per simulated target cycle over a full simulation. The simulation rate of a decoupled simulator can thus be given as  $f_{\rm FPGA}/{\rm FMR}$ . In contrast, a direct FPGA prototype by definition has FMR = 1 and a

resulting simulation rate of  $f_{\text{FPGA}}^{1}$ .

To date, such optimized simulators have seen little adoption, as their specialized timing models are difficult to design, optimize, and validate—which for nontrivial models may be far more complex than simply implementing the target design.

### 2.1.4 The FAME Simulator Taxonomy

Developed to help navigate the proliferation of academic FPGA simulators developed under the umbrella of the RAMP project, the FPGA Architectural Modeling and Execution (FAME) [84] taxonomy outlined three primary dimensions of the simulator design space. The binary presence or absence of three main features—decoupling, derivation from a high-level abstract description, and multi-threading—are used to encode a number in increasing order of significance. While this schema presents convenient labels, it belies some of the subtlety in systems that may potentially combine all three.

#### Decoupling

The lowest-order bit of the FAME taxonomy denotes whether a simulator is decoupled or direct. As a result, a simulator with decoupling alone is represented as the 3-bit binary number 001. For convenience, this is generally referred to as a "FAME-1" simulator.

However, this simple property does not capture any relative degree of decoupling in a particular simulator. In particular, given that many decoupled simulators are based upon an implementation split across one or more FPGAs and various software components, it is worth examining whether there is decoupling within the FPGA component. A simple decoupled simulator might simply decouple a monolithic FPGA component from the rest of the simulator, implying that the portion of the system simulated on the FPGA advances in time in unison. In contrast, more elaborate simulators might feature decoupled interfaces among disparate FPGA-based simulation models.

#### **Abstractly Specified Models**

The next bit—in the 2<sup>1</sup> place—encodes whether the simulator uses a full RTL design (zero) or a higher-level description (one) to specify the behavior of the target. It is generally well understood that the use of higher-level specifications—and their correspondingly weaker constraints—allow more algorithmic freedom to synthesize optimal implementations. While RTL provides a relatively strict specification for a system, an abstract model might elide microarchitectural details and adhere only to an architectural specification. This relaxation in constraints could lead to a more resource-efficient implementation.

While this broader solution space could theoretically be exploited by a compiler, there is no guarantee that an automated flow from an abstract specification to an FPGA implemen-

<sup>&</sup>lt;sup>1</sup>In some partitioned FPGA prototypes, "FMR" is actually a fixed number greater than one to allow for serialization-deserialization of target signals that span multiple FPGAs.

tation would necessarily outperform a traditional RTL-to-FPGA flow. Indeed, one need only examine the long and incremental road to viability of modern High-Level Synthesis (HLS) tools—which map behavioral algorithms to hardware implementations—to understand that abstract specifications do not always lend themselves to producing effective results in hardware systems.

In light of these challenges, real-world efficiency gains from abstract FAME models have generally come from careful human effort and engineering. A common pattern is the separation of an abstractly specified simulator into two parts: a simplified functional model that lacks microarchitectural detail, and a reduced-cost timing model that, while including fine-grained microarchitectural detail, may elide the significant fraction of the hardware dedicated to computing functional results. This timing-functionality split has generally been achieved through careful hand design of simulation models in prototypical systems such as FAST [20] and HAsim [71].

This reliance on handwritten design highlights an interesting question about abstract simulation models: are they more user-friendly than full RTL simulators? Though intrinsically subjective, it depends on multiple concrete properties of the entire simulation task, including the design cycle of the target system, the desired accuracy, the degree of variation in the target design space, and the time budget available for simulator development.

During early design exploration, the use of an abstract model avoids the need to develop a fully fledged RTL implementation of the target. However, since there is no general way to synthesize an implementation realizing the potential efficiency improvements of an abstract model, this is offset by the need to instead develop an RTL implementation of the model itself, where the need to explicitly consider the behavior of the host simulator adds additional challenge. However, while simulators relying on split timing and functional models have seen limited deployment due to their implementation complexity, well-designed abstract models can offer considerable flexibility, with new features being prototyped in hours, rather than days [84].

In contrast, when designs are further along in their life cycle, there is likely already a full RTL specification. Therefore, the use of abstract models would represent duplicated effort, and the ideal simulator compiler would operate on the ASIC-ready RTL. Though this increases the barrier to modeling extreme changes to the the target system, it also obviates the need to validate such changes in an abstract simulator. While abstract models may suffer from the same tradeoffs of flexibility and validation that have dogged high-level software architectural simulators [84], the use of RTL specifications ensures cycle accuracy by construction. Furthermore, advanced tools for writing hardware generators—discussed in Section 2.2—can help bridge the productivity gap in exploring large design spaces.

#### Multi-threading

The highest-order bit in the classification reflects the use of *threading*, a means by which the FPGA resource utilization of a simulator can be radically reduced at the cost of simulation throughput. While a direct mapping of an RTL design to an FPGA will result in a fully

parallel implementation that is theoretically capable of simulating one target cycle in a single host FPGA cycle, a threaded simulator will rely on serialization of the implementation relative to this parallel baseline. As discussed at length in Chapter 6, this is typically achieved by using a single underlying datapath to simulate multiple identical instances of a particular block or subset of the target design. While this reduces the peak throughput of the simulator by a degree equal to the number of replicated instances, scheduling logic that interleaves the different threads of simulation corresponding with the different instances can achieve good effective throughput by hiding other latencies, including that of modeling decoupled I/O.

#### **Combining Features**

As discussed above, while the FAME taxonomy relies on binary flags to represent the features employed by a simulator, not all combinations are practical. The decoupled simulators including these features fell into three primary categories: FAME-1, FAME-3, and FAME-7.

Employing decoupling alone, a FAME-1 simulator relies on the ability to "pause" the progress of simulated target time to model the I/O of a chip. Though this presupposes a division of the simulator into separate system and environment components, this is a natural fit for such simulators, as the system is specified as an RTL design. While FAME-1 simulators have appeared primarily in academic research, including the Green Flash [92] and MIDAS [54] (discussed further in 2.1.5), this paradigm is also employed by the commercial SCE-MI [43] standard for integrating FPGA-hosted simulations with software-defined modeling of external I/O.

In general, any abstractly specified component of a simulator would preclude a direct mapping of target to FPGA implementation, so this feature is naturally coupled with some degree of decoupling. Therefore, the use of abstract models in a decoupled simulator would be encoded as 011, and such a simulator would colloquially be called a "FAME-3" system. Similarly, the use of multi-threading generally implies a decoupling of host FPGA clock cycles and simulated time. While a "FAME-5" simulator would provide a threaded, decoupled implementation of a concrete RTL specification, the extant simulators that inspired the original FAME taxonomy tended to couple the use of threading with the use of abstract specifications. In particular, advanced "FAME-7" simulators such as HAsim and RAMP Gold tended to rely on threading of independent functional and timing models for a highly optimized FPGA resource footprint.

#### Hybrid Simulators and Model Granularity

While the FAME levels provide an intuitive classification for FPGA simulators, they lack the nuance to describe the full space of decoupled simulators. For example, while the use of abstract models would promote a decoupled simulator to FAME-3, it is crucial to note that this does not preclude the use of concrete RTL specifications for some components of the target design. Indeed, abstract and RTL specifications each provide distinct and complementary advantages; a practical hybrid simulator might transform the RTL implementation

the majority of a target SoC into a decoupled simulator while incorporating abstract models of difficult-to-implement, expensive components such as DRAM interfaces.

#### 2.1.5 FireSim and Golden Gate

While decoupled FAME simulation offers advantages in capacity, flexibility, and co-simulation capability, the engineering effort associated with developing a decoupled simulator has proven to be a significant barrier to adoption. Furthermore, the effort expended on developing abstractly specified models is often highly coupled to a particular target architecture—a hindrance to adopting agile hardware design methodologies. To address this gap, the FireSim [49] project aims to strike a balance between the generality of prototyping and the desirable features of decoupled simulation. To this end, it occupies a useful niche in the FAME space: co-simulating software models of off-chip components with a decoupled SoC simulator derived from full ASIC RTL. Furthermore, with an extreme focus on versatility and ease of use, it aims to provide a "batteries included" experience to a broad variety of users.

FireSim is a multi-layered framework that includes not only FPGA simulation tools for modern SoCs, but also a high-quality reference platform for computer architecture research. It includes configurable generators for Rocket-Chip-based systems (see Section 2.4), a collection of programmable accelerators, tools for generating Linux-based target software workloads, and co-simulated network simulation models to enable deterministic, coordinated simulation of multiple SoCs in a cluster- or datacenter-scale network. When simulating multiple SoC nodes, a networked FireSim simulation can be viewed as the composition of SoC-level units, each responsible for the cycle-accurate simulation of a single node. This layer involves a contrast with previous work in decoupling, as the compiler infrastructure of FireSim automatically generates a decoupled simulation model from the RTL implementation of the target design. Though the simulator may rely on composition with hand-written or software-based models, this "core" model is automatically transformed from the input ASIC RTL; in the simplest case, this becomes a FAME-1 component of an overarching FAME-3 simulator.

To preserve modularity in this complex workflow, the task of transforming the portion of the target design specified via concrete RTL is performed by a dedicated *simulator compiler*. While many components of the FireSim ecosystem are in some way specialized for the existing space of target designs, this simulator compiler is more general, operating on a nearly arbitrary input design. At the time of this writing, there have been two generations of simulator compilers included with FireSim: MIDAS and GOLDEN GATE.

#### **MIDAS**

Throughout its initial development and release, FireSim relied on a non-optimizing compiler, MIDAS [54], to convert the portion of the target design specified via RTL to a monolithic decoupled model. The model transformation performed by MIDAS was fairly straightforward: it automatically added handshaking interfaces to the I/O boundary and added enable

signals to state updates that could "pause" forward progress, allowing the model to stall while it waits for tokens [52]. This technique enables co-simulation of network interfaces to model networks of thousands of target machines [49] and FPGA-accelerated modeling of the external DRAM interfaces of the target ASIC [8]. While this resembles the clock-gating approach used to support transactional emulation [43], the flexible decoupled interface with the target simplifies instrumentation to support power modeling and debugging features [54, 53]. However, while MIDAS effectively added FAME-1 decoupling, the ASIC RTL used within the model is largely unchanged, yielding the same resource utilization challenges as FPGA prototypes. Furthermore, this approach assumed the use of both a single clock domain and exclusively synchronous reset, restricting its applicability to simple systems not entirely representative of modern SoCs.

#### Golden Gate

In order to address the limitations of MIDAS, recent releases of FireSim have relied on Golden Gate, an optimizing simulator compiler for realistic SoCs [68]. Golden Gate relies on a higher degree of decoupling, allowing the portion of the target design specified via RTL to be decomposed into multiple simulator "blocks," with each independently compiled to a decoupled implementation and potentially optimized. This modular structure allows the compiler to be extended to include new features, and the work presented in this dissertation is implemented as part of Golden Gate. Chapters 3 and 4 provide an introduction to the overall structure of Golden Gate; this common infrastructure was implemented as a joint collaboration to enable both optimizations and enhanced support for target design features to be added to FireSim. The optimizations described in subsequent chapters build upon this baseline and are incorporated into the latest releases of Golden Gate.

# 2.2 Chisel: A Modern Language for Hardware

While the hardware design industry generally relies on the Verilog [42] and VHDL [40] hardware description languages (HDLs) to express register-transfer level (RTL) designs, these dated languages continue to present productivity hurdles for designers. In particular, while each has proven to be an effective foundation for modern ASIC flows built around logic synthesis, their low-level semantics are a strict superset of synthesizable behaviors, allowing for deeply non-intuitive mismatches with designer expectations. Furthermore, despite the excessive generality of their low-level operations, both languages have limited support for parameterization, hindering design reuse.

In many ways, the pitfalls of HDL semantics for logic design are a natural consequence of their development: neither VHDL nor Verilog was originally intended as a means to develop concrete hardware implementations; instead, they were intended to describe the behavior of a system in a modeling or simulation environment. This mismatch has led to perennial issues where expectations do not match the semantics of the language: misguided inference of latch-based state by synthesis tools [27], four-state logic [82], and complicated ordering of statements [34] have dogged digital designers throughout the modern era of relying on Verilog-based synthesis tools for RTL design. In response, a broad industry of linters and other EDA tools has emerged to help guard the gaps between user expectations and Verilog semantics [79]; while this has proven to be useful in practice, it is an imperfect solution that also introduces extra complexity and arcane restrictions.

Given these qualities of popular HDLs, designers are faced with the paradoxical realization that such languages are simultaneously far too expressive for strict RTL semantics but insufficiently expressive to reuse implementations across common parameterization patterns. For example, while Verilog supports generate blocks for static replication of RTL templates, it lacks support for parameterizing the set of I/O signals of a module or polymorphically selecting which of a set of different child modules to instantiate within a parent. To circumvent these limitations, tools such as Genesis [80] employ a strategy similar to a C preprocessor to embed fragments of Verilog or VHDL within an enclosing program—or *qenerator*—in a scripting language such as Perl. When the script is executed, it assembles the fragments into a valid HDL specification; this process can employ dynamically varying execution paths, string interpolation, and rich parameter sets to allow a wide range of different designs to be produced from a single generator. This paradigm is more generally an example of staged meta-programming, where the execution of one program leads to the generation of another [13]. However, this approach suffers from two primary flaws: it does little to address the potential for mismatches with RTL semantics, and given the disparate semantics of the stages, it offers no guarantees that a given generator output will even be valid HDL code.

In contrast to these Perl-based preprocessing flows for Verilog, the Chisel [6] project provides a safer, more principled approach for meta-programming digital hardware generators. Rather than employing a second scripting language to assemble fragments of an existing HDL, Chisel is a hardware construction language (HCL) embedded in the Scala programming language [81]. A Chisel generator uses a simple core API to manipulate elements that correspond with RTL signals; while this allows the enclosing Scala program to comprise a highly parameterized generator that dynamically constructs varying circuits through its execution, the simplicity of the API guarantees that the resulting circuit is valid. Indeed, since this API contains only strict RTL behaviors, it is possible to say that any Chisel-generated circuit is synthesizable by construction.

Given its emphasis on predictable behavior, Chisel has naturally lent itself to CAD research. As discussed in Section 2.3, the generated circuits are represented via a portable intermediate representation, FIRRTL, which serves as a foundation for the work presented in this dissertation. Though FIRRTL is not intrinsically tied to Chisel and can be produced by other user-level tools, Chisel serves as the primary design language for both the target designs used in our experimental evaluations (introduced in Section 2.4) and for numerous instances of simulation-specific hardware in the GOLDEN GATE implementation.

# 2.3 The FIRRTL Hardware Compiler Framework

Introduced as part of the compiler infrastructure for Version 3.0 of Chisel, FIRRTL [47], the Flexible Intermediate Representation for RTL, is an intermediate representation for digital circuit designs. Inspired by the success of LLVM [60], an Intermediate Representation (IR) from the software compiler world, the open-source FIRRTL project provides both a specification and a reference compiler implementation. Beyond its use in the Chisel ecosystem, FIRRTL also provides an ideal infrastructure for writing tools that manipulate digital circuits; since it is "language-agnostic" with respect to the frontend, user-facing design language, it allows tool developers to focus on the core functionality of CAD or simulation tools.

### 2.3.1 FIRRTL Intermediate Representation

The FIRRTL representation (IR) is designed to capture the range of essential features for modern digital circuits at the register-transfer level (RTL). In contrast with a general-purpose HDL such as IEEE Verilog [42] or SystemVerilog [41], the design of FIRRTL is specialized for writing transformations that operate at the RTL level, which provides several notable benefits to the implementer of complex tools like GOLDEN GATE.

- 1. Unlike Verilog, which is capable of modeling many subtly different forms of concurrent execution, FIRRTL limits the semantics of assignment statements to RTL behavior.

- 2. As a direct consequence of the "RTL-only" restriction, all FIRRTL circuits are synthesizable by construction.

- 3. Since FIRRTL is designed to integrate with powerful front-end languages like Chisel, it lacks complex features like functions, loops, and generate statements.

- 4. FIRRTL provides explicit wire and register declarations that intrinsically restrict corresponding assignments to be combinational or synchronous, respectively.

- 5. First-class memories include port and behavior definitions, which avoids the challenges of inference and errors with multi-dimensional array accesses.

While an alternative to handling Verilog and all its complexities would be to rely on a specialized netlist format or structural subset of Verilog that disallows procedures, tasks, and functions, there is also a significant productivity advantage associated with using FIRRTL. In contrast to a pure netlist, FIRRTL includes convenience features such as composite types and conditional assignments. With these small additions, FIRRTL represents a happy medium between an HDL and a netlist that is particularly amenable to writing tools such as GOLDEN GATE that involve not only transforming a circuit but modifying its RTL behavior in a programmatic fashion.

### 2.3.2 The Reference FIRRTL Compiler

While FIRRTL IR is effectively a language that is specified in a reference manual [65], the FIRRTL compiler infrastructure includes a default implementation that is structured as an extensible Scala framework, allowing the reference compiler to be reused and extended in whole or in part. The core unit of reuse in a FIRRTL flow is a *transform*, which is a functional transformation from an input circuit to an output circuit.

# 2.4 The Rocket Chip Generator

Rocket Chip [3] is an open-source project that provides a configurable generator to combine multiple processor implementations, coherent caches, accelerators, and peripherals to produce custom SoCs. It is industry-proven, and has served as the basis for numerous academic ASIC tapeouts in modern process technologies [77]. By combining a lengthy silicon track record, modern architectural features, extreme customization, and permissive open-source licensing, it has proven to be a valuable target design for the FireSim project. Larger, more feature-rich configurations may provide multiple cores, multiple levels of caches, page-based virtual memory (with TLBs to cache translations), and support for running Linux. Furthermore, Rocket Chip is tightly integrated with the Chisel language and therefore enables straightforward experimentation with FIRRTL-based compiler tools such as GOLDEN GATE. Therefore, the work presented in this dissertation is evaluated against a set of target designs based on the Rocket Chip generator. While these targets rely on a common generator, the generated SoCs span a wide range of performance, power, and area (PPA) by varying parameters such as type and number of cores. In particular, we examine designs based on the in-order Rocket core and the high-performance, out-of-order BOOM core [16].

#### 2.4.1 Rocket

In its default distribution, Rocket Chip is based on Rocket, a traditional five-stage in-order pipeline. As with the top-level SoC generator, Rocket is highly parameterizable, with support for both 32- and 64-bit RISC-V ISAs along with all standard extensions. At the microarchitectural level, the bypassing of data from older instructions that have not yet committed their architectural results to newer, dependent instructions can be enabled to improve performance or disabled to save resources. Efficient hardware support for IEEE 754 floating point operations can be selectively added, as can variable-latency units for integer multiply and divide. While Rocket issues instructions in program order, these long-latency operations can be improved by enabling a scoreboard to allow out-of-order completion.

As Rocket was the first silicon-proven implementation of the RISC-V ISA, it has been repeatedly validated in both academic and industrial systems. Furthermore, it represents a sensible combination of performance and efficiency for many applications. Therefore, it remains a mainstay of RISC-V SoCs, while also providing a mature benchmark for tools in the Chisel and FIRRTL ecosystem.

#### 2.4.2 BOOM

BOOM, the Berkeley Out-of-Order Machine, is an open-source out-of-order, superscalar implementation of the RISC-V ISA. It is organized around explicit register renaming and a unified physical register file; in this respect, it is similar to notable out-of-order RISC processors such as the MIPS R10000 [95] or the DEC Alpha 21264 [50]. Like Rocket, BOOM is implemented as a core generator using Chisel; however, it extends this parameterization to reflect the broader design space of out-of-order cores. In addition to the sizes of discrete-capacity structures like register files and reorder buffers, BOOM provides the novel capability to vary the maximum degree of instruction-level parallelism allowed at various points in the pipeline. By appropriately choosing the fetch, decode, and issue widths, along with the mix of execution units, it is possible to generate instances ranging from an efficient two-issue core to a large, four-issue core comparable in performance to a mobile application processor. Furthermore, BOOM offers a collection of parameterizable branch prediction algorithms; users may even define their own, providing a powerful tool for computer architecture research.

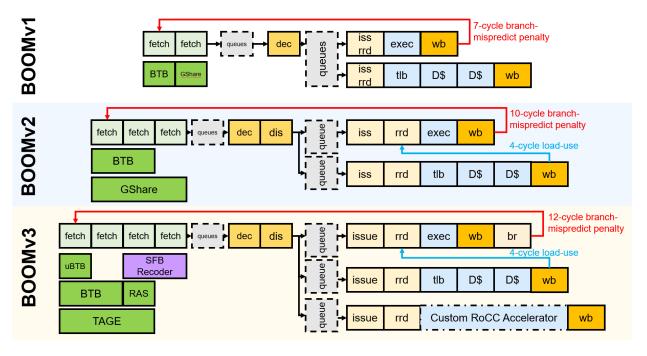

Though BOOM provides unique flexibility, it is constrained by the need to provide high-quality, performant, physically realizable implementations of various design points. Since selection of these design points presents its own challenges, the BOOM repository includes several pre-defined default configurations spanning various levels of PPA; these "sane defaults" provide good starting points for research and realistic benchmarks for hardware design tools. Furthermore, as with any large open-source project, BOOM has gone through multiple revisions. To illustrate the gradual evolution in complexity—and performance—over time, a high-level pipeline diagram for each version is shown in Figure 2.2. The BOOM v2 release [15] focused on physical design considerations based on experiments in mapping the core to a modern 28nm process technology, which led to a successful tapeout. The current BOOM release, known as SonicBOOM [96], offers significantly improved performance, with instructions-per-cycle (IPC) metrics that are competitive with some comparably sized commercial cores on industry-standard benchmarks.

Figure 2.2: (Figure used with permission from Jerry Zhao [96]) A set of pipeline diagrams representing the microarchitectures of the three major BOOM releases. The SonicBOOM release represents a significant step forward in performance through increased instructions-per-clock (IPC) over BOOMv2.

# Chapter 3

# Dataflow Simulation with Golden Gate

In the broad landscape of existing simulation FPGA simulation projects, the presence of decoupling has been used to delineate advanced simulators from those that rely on directly mapping input RTL to equivalent FPGA implementations. However, the definition of decoupling is largely operational: a decoupled simulator is one that may use multiple clock cycles of host FPGA execution to simulate a single cycle of target system behavior. In this chapter, we explore the nuances associated with decoupled simulators, particularly hybrid or compositional simulators that employ a higher degree of decoupling to enable automatic optimization of the resulting FPGA implementations. Finally, drawing upon previous work, we outline a framework for robustly constructing compositional simulators from target RTL designs.

# 3.1 All Simulators are Hybrid Simulators

As discussed in Section 2.1.4, advanced decoupled simulators may often apply different simulator implementation strategies to model different subsets of the the target system. These hybrid simulators might combine abstract models of some components, such as DRAM or PCIE interfaces, with a simulation of the remainder of the SoC that is derived from an RTL specification.

However, even the most basic simulators generally employ some form of hybrid design; when viewing a simulation as a "closed world," even a direct FPGA prototype will generally rely on some software functionality on a general-purpose host processor. Most practical FPGA-based simulators include at least some software components hosted on a general-purpose processor. As typified in the SCE-MI standard for software co-modeling, these often serve to model I/O or other components not implemented in the RTL specification for the device under test.

In this work, we focus on hybrid simulators that not only support co-simulation, but

also divide the task of simulating the RTL specification of the target design across a network of communicating *simulation models*. Each component of this network may simulate a corresponding partition of the target with an implementation that falls under a different level of the FAME taxonomy, and the resulting hybrid simulator will involve many internal, asynchronous communication interfaces that lead to a very high degree of decoupling.

### 3.1.1 Refining the Notion of Decoupling

Though the FAME taxonomy presents a dichotomy between FPGA prototype and decoupled simulators where the former requires a one-to-one relationship between target and host clock and the latter does not, this operational definition makes it difficult to classify many practical FPGA simulators. FPGA prototypes often involve multiple clock domains, including ones that do not directly represent a target clock. Large multi-FPGA simulators often use fast SERDES to serialize the exchange of signal values across the boundaries of the partitions; this technique to circumvent pin-count limitations spreads one element of simulating a particular target cycle over multiple periods of a high-frequency host clock. Indeed, even double-pumping of block RAMs to model highly ported memories exploits the ability to reason about the FPGA clock as a feature of the host platform. However, simulators employing these techniques alone do not generally fit with the explicit decoupling found in FAME simulators.

With this in mind, it is clear that simulators may possess varying degrees of decoupling. Arguably one of the most important features of FAME simulators like FAST, HAsim, ProtoFlex, and RAMP Gold is not merely dividing the work of simulating a target cycle across multiple host cycles, but allowing the implementation to tolerate variable latency. This is enabled by the use of asynchronous handshaking interfaces to exchange data among simulation models, allowing for true decoupling of their execution. Furthermore, such "globally asynchronous" simulators vary in the degree to which simulation is distributed across multiple decoupled components; the most advanced simulators like RAMP Gold blend components with single-cycle, fixed multi-cycle, and variable latencies [83].